在 DC/DC 电源的 PCB 布局设计中,功率电感正下方是否应该铺铜,是许多硬件工程师反复讨论甚至争论的话题。支持者认为,完整的铜层有助于散热并抑制 EMI;反对者则担忧铺铜会引入涡流损耗、改变电感量并带来地噪声。本文将从电感的核心分类出发,结合实际测试数据,分析铺铜的利弊,并针对不同类型的电感给出明确的设计建议。

电感的分类

在解决铺铜争论之前,我们首先需要了解电感通常是如何分类的。简而言之,根据磁场的屏蔽程度,功率电感主要可分为三类。

非屏蔽电感

结构:磁芯为开放或半开放结构(如棒状、E 型、无外罩绕线),磁场会大量向外辐射。

特点:

- 成本低、工艺简单,电感值范围广;

- 磁场泄漏大,对外 EMI 干扰 强,同时自身也容易受外界干扰;

- 对下方铺铜极敏感:交变磁场会在铜皮中产生明显涡流,导致电感量下降、损耗剧增。

典型应用:低频滤波、对 EMI 要求不高的消费电子、非关键电源支路。

Layout 建议:正下方必须挖空铺铜,同时应远离 ADC、时钟、射频等敏感信号线。

半屏蔽电感

结构:磁芯外部包裹一层金属或磁性屏蔽罩(如铁氧体外壳、磁胶包覆),但未完全封闭磁路。

特点:

- 磁场泄漏显著减少,EMI 性能优于非屏蔽型;

- 成本适中,兼顾了性能与价格;

- 对下方铺铜较敏感:仍存在部分漏磁,高频下的涡流损耗仍不可忽视。

典型应用:对 EMI 和成本有平衡要求的通用电源场景。

Layout 建议:正下方优先挖空,若出于散热考虑,可在电感周边铺网格铜,避免用实心铜直接覆盖。

一体成型电感

结构:绕组与金属磁粉(如铁硅铝、铁镍钼)一体压铸成型,磁路高度闭合,几乎无磁场泄漏。

特点:

- 屏蔽效果极佳,EMI 辐射极低,抗干扰能力强;

- 饱和电流大、直流电阻(DCR)低、散热性能好;

- 对下方铺铜敏感度低:磁场被严格限制在磁芯内部,因此涡流损耗和电感量偏移很小。

典型应用:大电流 DC/DC(如服务器、电动车、手机快充)、高频开关电源、EMI 要求严格的场景。

Layout 建议:可适度在下方铺实心铜以辅助散热,仅需保留少量安全间距即可。

实验验证

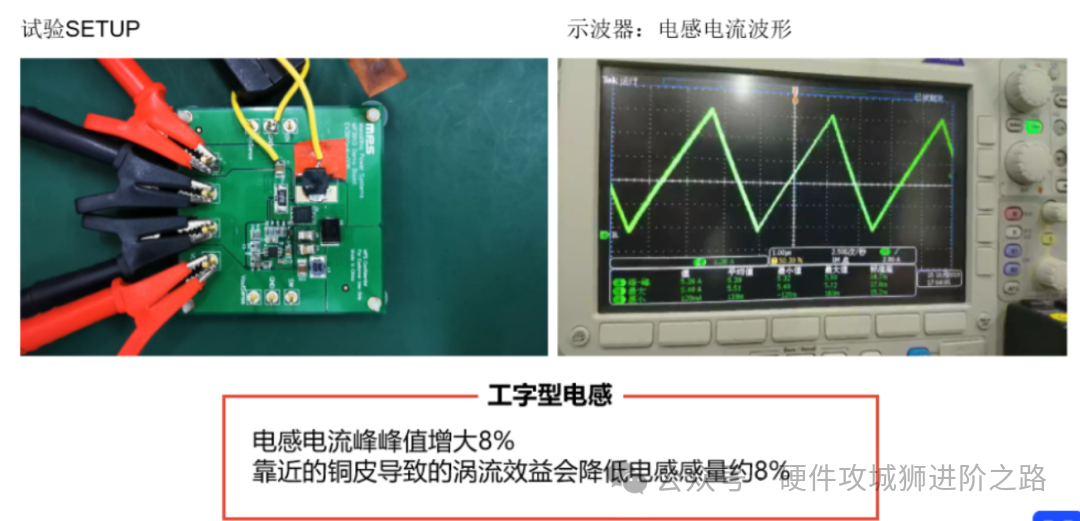

理论分析需要数据支撑。本次研究采用了某芯片厂商的专用评估板进行对照试验,通过在功率电感附近增设接地铜箔,等效模拟电感底部铺铜的实际工况,并以电感电流波形的纹波(峰峰值)为核心指标,定量分析铺铜带来的影响。

测试数据显示,当接地铜箔靠近工字型非屏蔽电感时,其电感电流峰峰值相比无铜箔状态上升了约 8%(如下图所示)。电流峰峰值增大,意味着等效电感量下降,这与涡流损耗的理论相符。而在半屏蔽电感、一体成型电感的对比测试中,电流峰峰值未出现明显变化,整体保持稳定。

图:使用评估板进行验证实验,示波器显示工字型电感电流波形

这个实验清晰地证明:在电感底部铺铜,仅对非屏蔽电感的感量有可观测的影响,而对屏蔽型电感(半屏蔽、一体成型)的感量则基本没有影响。

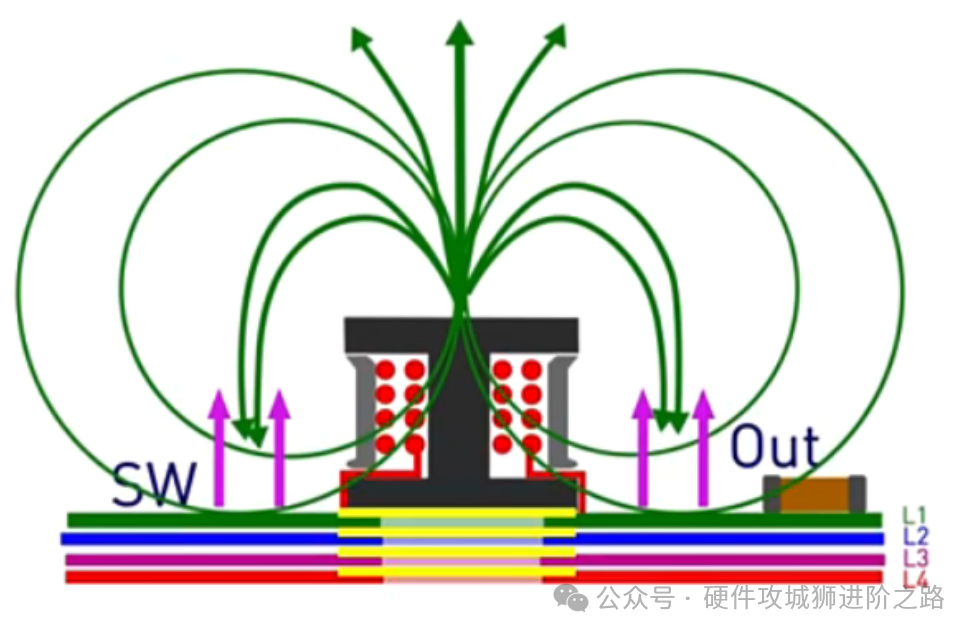

在电感下方铺铜的益处

铺铜的主要正面效应在于 EMI 屏蔽。下方的铜皮会形成涡流,这些涡流产生的磁场方向与电感泄漏磁场相反,从而抵消部分向外辐射的高频磁场,降低对外的 EMI 干扰。其电磁场原理如下图所示:

图:涡流效应抵消高频磁场,降低对外辐射

结论

综合理论分析与实测数据,我们可以得出以下设计结论:

- 对于非屏蔽电感(如工字电感):底部铺铜会引入显著的涡流损耗,导致电感量下降、温升增加。强烈建议在正下方所有层挖空铺铜,以确保电感性能稳定。

- 对于半屏蔽电感:仍存在一定漏磁,铺铜可能带来轻微影响。优先考虑正下方挖空;如果散热压力大,可采用网格铜或在周边铺铜的方式进行折中。

- 对于一体成型电感:磁场封闭性极好,铺铜影响微乎其微。推荐在下方铺实心铜,这不仅能有效辅助散热,还能提供额外的 EMI 屏蔽 benefit,提升系统整体 EMC 性能。

因此,关于“电感下方要不要铺铜”的问题,答案并非一成不变。关键在于识别你所使用的电感类型,并根据其磁场特性做出最合理的布局决策。掌握这一原则,你的电源设计在性能和可靠性上都会更上一层楼。

希望这篇结合了原理与实验的分析能为你带来启发。如果你想深入探讨更多硬件设计细节,欢迎访问 云栈社区 与广大开发者交流。 |