本文献给所有刚刚踏入或即将开始硬件电路设计领域的朋友。时间过得真快,距离我第一次绘制电路板已经过去三年了。回想最初接触电路板时,我和你们一样,心中充满疑问,却又夹杂着兴奋。网络上关于硬件电路的经验和知识浩如烟海,像信号完整性、电磁干扰(EMI)、电源设计这些概念,很容易让人感到晕头转向。别着急,凡事都需要一个循序渐进的过程。

总体设计思路

设计硬件电路,首先要理清大的框架和系统架构,但这本身就不是一件容易的事。有时候,项目的整体框架可能由你的老板或导师已经规划好,你的任务是将想法具体实现;也有些情况需要你亲自搭建框架,这时就必须明确要实现哪些功能,然后去寻找是否有实现相同或相似功能的参考电路板。懂得借鉴他人的成熟成果,是一名工程师走向成熟的重要标志,经验越丰富的工程师越擅长此道。

理解电路是关键

如果你幸运地找到了合适的参考设计,那么恭喜你,这能为你节约大量时间。仔细研究它的原理图,判断其关键参数是否符合你的要求,以及你能否看懂这些参数,都是硬件工程师能力的体现,这需要长期的积累。在这个过程中,要善于提问,因为你自己不懂的地方,别人往往一点就透。

核心设计流程与工具

现在主流的电路设计工具,比如 Altium Designer (Protel) 在国内比较流行,容易上手,应对一般的设计工作已经足够。它采用的是“后命令”操作模式,类似于 Windows 的操作习惯;而 Cadence 的 Concept & Allegro 则是“前命令”模式。习惯了 Protel 再突然转向 Cadence,肯定会感到不适应。

无论使用哪种工具,一个完整的设计通常都包含以下几个核心环节:

- 原理图设计

- PCB 设计

- 制作 BOM 表(物料清单)

下面我们简要谈谈设计流程中的关键步骤。

1. 建立原理图库

要在原理图中放置一个新元件,必须先建立该元件的库。库文件主要定义了元件的引脚定义及其属性,并用图形符号表示(通常是一个代表芯片本体的矩形,周围是代表引脚的短线)。Altium Designer 创建库非常简便,而且由于用户众多,许多常用元件都能找到现成的库,这对初学者极为友好。你需要清楚地区分芯片本体(IC Body)、芯片引脚(IC Pins)、输入引脚(Input Pin)、输出引脚(Output Pin)、模拟引脚(Analog Pin)、数字引脚(Digital Pin)和电源引脚(Power Pin)等概念。

2. 绘制原理图

有了充足的元件库,就可以开始绘制原理图了。根据芯片数据手册(Datasheet)和系统设计的要求,用导线(Wire)将相关元件连接起来。记得在关键位置添加线条(Line)和文本(Text)进行注释。这里要注意,Wire 具有电气连接属性,而 Line 没有,仅用于图形注释。Wire 用于连接相同网络名的节点。

3. 生成网络表(Netlist)

原理图绘制完成后,需要将其转换为网络表。网络表是连接原理图和 PCB 的桥梁,包含了各个元件的封装信息以及网络连接信息。

4. 电气规则检查(ERC)

生成网络表前,别急着进行下一步,先做 ERC 检查。ERC 能排查一些原理图上的基本设计错误,比如多个输出引脚短路连接在一起等。但务必仔细检查自己的设计,不能过分依赖工具,毕竟工具无法理解你的设计意图,它只是基于固定规则进行检查。

5. 导入 PCB 与板框定义

从网络表导入 PCB 后,面对密密麻麻的元件和数不清的预拉线(飞线),是不是有点头皮发麻?别急,我们一步步来。首先在禁止布线层(Keepout Layer)或机械层(Mechanical Layer)绘制板框,这将限定布线的区域。确定板框时,需要综合考虑板子的尺寸(长、宽,有时还有厚度)以及叠层方案。例如,一块4层板,顶层走信号,中间第一层铺电源,中间第二层铺地,底层走信号,这就是一种常见的叠层策略。

6. 元器件布局

确定板框后,就到了极为关键的元器件布局阶段。布局的好坏往往直接决定了后期布线难度。哪些元件该放在正面,哪些该放背面,都需要仔细考量。这有时没有绝对标准,从不同角度思考会有不同的摆放方案。实际上,自己画的原理图,自然对每个元件的功能了如指掌,对布局也会有清晰的认识。对于新手,重点关注模拟与数字元件的隔离、元件机械位置的限制,以及电源网络的拓扑结构即可。

7. 布线

布线工作通常与布局互动进行。有经验的设计师在布局时就能预判哪些地方布线会困难。如果某些区域确实难以走通,可能还需要返回去调整布局,甚至在 FPGA 等复杂设计中,有时需要修改原理图来适配布线。

8. 后续处理与生产

布线完成后,有些 PCB 还需要敷铜(这可能会增加成本),将走线与焊盘的连接处做成泪滴状(有些 PCB 工厂会帮你添加)。最后,将 PCB 文件转换为 Gerber 文件即可交付生产。

9. 准备装配与 BOM 表

要装配 PCB,就需要准备 BOM 表,通常可以直接从原理图软件中导出。但需要注意的是,必须心里清楚原理图中哪些元件需要焊接,哪些不需要。对于小批量或研发板,用 Excel 自行管理比较方便;大公司则会使用专业的物料管理软件。对于新手的第一版设计,不建议直接将所有 BOM 物料交给工厂焊接,这样不利于后续问题排查。最好的方法是自己根据 BOM 表备好元件,等 PCB 板到手后,再一步步焊接、调试。

硬件调试实战指南

调试第一步:上电前检查

拿到焊接好的板子,第一步做什么?千万不要急着上电测试功能。硬件调试不可能一步到位。

- 检查短路:先用万用表测量关键网络是否异常,重点是检查电源(VCC)与地(GND)之间是否短路。尽管生产厂商会做测试,但这一步亲自检查非常必要,看似繁琐,却能节省后面大量排查时间!短路问题不一定出自 PCB 设计,可能是生产、焊接任何一个环节导致的。I/O 口短路一般后果不严重,但电源短路就可能导致灾难性后果。

- 检查电源:如果电源网络没有短路,太好了。接着检查各电源芯片的输出电压是否正常。对于初学者,建议调试时逐个焊接芯片,第一个要焊的就是电源芯片。

常见电源问题排查

- 电源网络短路了? 这比较麻烦。需要仔细核对原理图是否存在短路可能,同时结合“割线法”一步步排查,确定是 PCB 制造问题、装配问题还是自身设计问题。

- 电源芯片没有输出? 检查电源芯片的输入电压是否正常,还有使能(Enable)信号、分压电阻配置、反馈网络等。

- 电源输出值偏差太大? 如果偏差超过10%,首先检查分压电阻,这两个电阻通常要求1%的精度。同时检查反馈网络,它也会影响输出电压。

电源稳定性测试

电源输出正常了,也别高兴太早。有条件的话,最好用示波器抓取一下电源上电瞬间的波形,观察输出电压从无到有的建立过程,看看是否存在过冲、振铃等异常。这是评估电源动态性能的重要一环。

深入理解电源设计

电源无疑是整个电路板稳定工作的基石。电源不稳,一切免谈。我们最常遇到的电源设计场景是:从一个稳定的高电压,得到一个稳定的低电压。这就是常说的 DC-DC(直流转直流)。

在 DC-DC 中,最常用的稳压芯片有两类:LDO(低压差线性稳压器) 和 PWM(脉宽调制开关电源)。我们常听说 PWM 电源效率高,但 LDO 响应快,这是为什么呢?让我们从原理入手来分析。

下面会涉及一些基础理论,但保证浅显易懂。如果你觉得吃力,或许该回顾一下自己的电路基础了。

一、线性稳压电源(LDO)工作原理

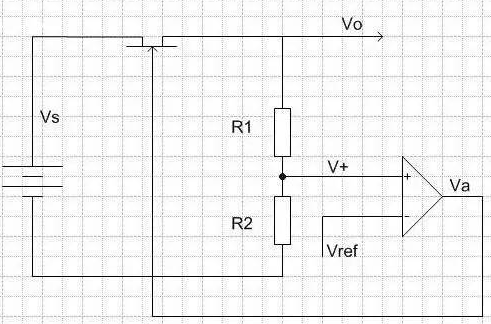

上图是线性稳压电源内部结构的简化示意图。目标是从高输入电压 Vs 得到稳定的低输出电压 Vo。Vo 经过 R1 和 R2 分压得到 V+,V+ 被送入误差放大器的正端。放大器的负端接一个恒定的内部参考电压 Vref。放大器的输出 Va 连接到 MOSFET 的栅极来控制其导通阻抗。Va 变大,MOSFET 阻抗变大;Va 变小,阻抗变小。MOSFET 上的压降就是 Vs - Vo。

稳压过程:假设 Vo 变小 → V+ 变小 → Va 变小 → MOSFET 阻抗变小 → 在相同负载电流下,MOSFET 上的压降 (Vs-Vo) 变小 → 从而将 Vo 抬升,抑制其下降。反之亦然。这是一个典型的负反馈闭环控制系统,理解这个反馈环对掌握计算机基础中的控制系统概念很有帮助。

二、开关电源(PWM)工作原理

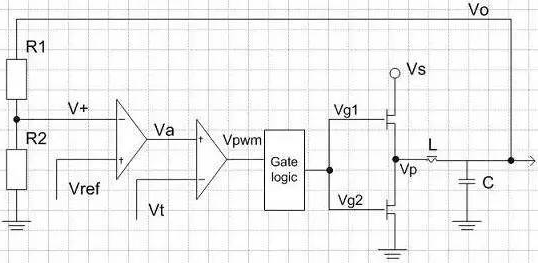

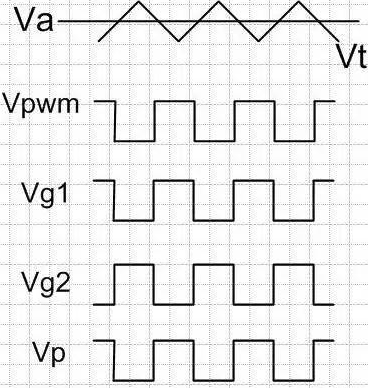

如上图,为了从高电压 Vs 得到 Vo,开关电源采用了一对反相(互补)的方波信号 Vg1 和 Vg2 来驱动上下两个 MOSFET。当上管(Vg1)导通时,下管(Vg2)关断;下管导通时,上管关断。这样在电感 L 的左端就产生了一个一定占空比的方波电压。电感 L 和电容 C 组成低通滤波器,将方波滤波后得到平滑的直流电压 Vo。

Vo 经过 R1、R2 分压后得到 V+,送入误差放大器的负端。误差放大器的输出 Va 作为 PWM 比较器的正端输入。PWM 比较器的负端输入 Vt 是一个固定的三角波。当 Va 高于三角波时,Vpwm 输出高电平;低于时输出低电平。这样,Va 的电压值就决定了 Vpwm 方波的占空比。Vpwm 经过门逻辑电路生成两路反相的驱动信号 Vg1 和 Vg2。

(图示:开关电源关键节点的波形关系)

三、LDO 与开关电源的比较

理解了工作原理,就很容易明白它们的特性差异:

- 线性稳压电源(LDO):内部结构简单,反馈环路短,因此噪声小,瞬态响应快(输出电压变化时补偿迅速)。但因为输入输出的压差全部消耗在 MOSFET 上(以热的形式散失),所以效率较低。通常用于小电流、对电压精度和噪声要求高的场合。

- 开关电源(PWM):内部结构复杂,影响输出噪声的因素多,且反馈环路长,因此噪声性能通常不如 LDO,瞬态响应也较慢。但其优点在于效率高,因为 MOSFET 工作在完全导通或完全关断状态,理想情况下自身损耗很小(除了驱动损耗和导通电阻损耗),大部分能量都输出了。

高速信号设计的常见误区

这一部分旨在澄清关于高速信号认识的一些常见错误观念。

误区一:高速看的是信号沿,不是时钟频率。

- 通常,时钟频率高的信号,其上升沿也快,所以我们把它们归为高速信号。但反过来不一定成立!时钟频率低的信号,如果上升沿很陡,一样要当作高速信号来处理。根据信号理论,快速的边沿包含了丰富的高频成分。如果设计不当,很容易出现边沿缓慢、过冲、下冲、振铃等问题。例如 I2C 信号,在超快速模式下时钟仅 1MHz,但规范要求其上升/下降时间不超过 120ns!很多板卡的 I2C 信号就栽在这个参数上。

- 因此,我们更应关注的是信号带宽。一个经验公式是:带宽 (Fw) × 上升时间 (Tr, 10%~90%) ≈ 3.5。

误区二:选择示波器时只关注采样率,忽略带宽。

很多人知道采样率需要满足奈奎斯特定律(大于信号最高频率的2倍),却忽略了示波器带宽这个更关键的参数。错误的原因在于混淆了时钟频率和信号带宽。你需要保证示波器的带宽大于你待测信号的带宽(通常至少是信号最高频率的3到5倍)。一个 100MHz 带宽的示波器,其前端放大器对 100MHz 正弦波的衰减约为 -3dB。对于数字信号,示波器带宽至少应为信号基频的 3 倍,若要精确测量上升时间,则要求更高。例如,测量一个上升时间为 1ns 的信号,需要的示波器带宽至少为 0.35 / 1ns = 350MHz。同时,千万别忘了你使用的探头也必须具备相应的带宽!

希望这份融合了流程、调试与原理分析的指南,能为你学习硬件设计提供一条清晰的路径。如果在实践中遇到具体问题,欢迎到云栈社区与更多硬件爱好者一起交流探讨。