在高速PCB设计中,信号完整性是一个无法回避的核心议题。一个常被提及的关键词就是“阻抗”。它到底是什么?为什么它的匹配如此重要?今天,我们就来深入探讨一下PCB设计中的阻抗问题。

什么是阻抗

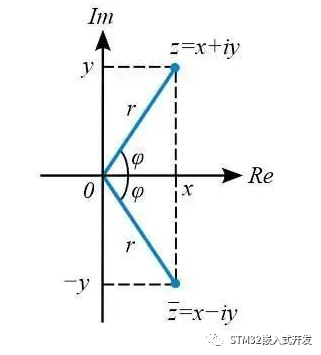

在电学中,常把对电路中电流所起的阻碍作用叫做阻抗。阻抗的单位为欧姆,常用 $Z$ 表示,并且它是一个复数:

Z = R + i(ωL – 1/(ωC))

具体说来,阻抗可分为两个部分:电阻(实部)和电抗(虚部)。其中电抗又包括容抗和感抗。由电容引起的电流阻碍称为容抗,由电感引起的电流阻碍则称为感抗。

阻抗匹配的理想模型

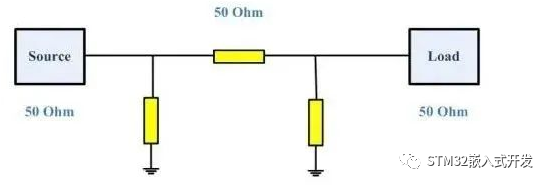

许多射频工程师都遇到过阻抗匹配的问题。通俗地讲,匹配的目的是确保信号或能量能从“信号源”高效地传送到“负载”。

最理想的模型当然是:源端的输出阻抗为50欧姆,传输线的特性阻抗为50欧姆,负载端的输入阻抗也是50欧姆。一路50欧姆下来,信号畅通无阻,这是最完美的状态。

然而现实情况往往并非如此:源端阻抗很少恰好是50欧姆,负载端阻抗也经常偏离这个值。这时,我们就需要引入由电感和电容构成的匹配电路来进行调试,以达到最佳的射频性能。

阻抗匹配的方法

阻抗匹配主要有两个思路:一是改变阻抗力,二是调整传输线。

改变阻抗力:通过电容、电感与负载进行串联或并联,从而调整负载的阻抗值,使其与源阻抗相匹配。

调整传输线:增加源和负载之间的距离,并配合电容和电感,将阻抗力调整为零,从而消除反射。此时信号能量将全部被负载吸收。

在高速PCB布线中,通常将数字信号的单端走线阻抗设计为50欧姆。行业内也通常规定:同轴电缆基带为50欧姆,频带为75欧姆,而对绞线(差分线)的阻抗则在85-100欧姆之间。

阻抗匹配应用举例——振铃现象

在实际项目中,尤其是进行电信号测量时,工程师们经常会遇到令人头疼的“振铃”现象。

由于任何传输线都不可避免地存在引线电阻、引线电感和杂散电容,一个标准的脉冲信号在经过较长传输线后,极易产生上冲和振铃。简单来说:

- 引线电阻会使脉冲幅度减小。

- 引线电感和杂散电容是产生上冲和振铃的“元凶”。电感越大,振铃越严重;电容越大,信号上升时间越长。

当信号在传输过程中感受到阻抗突变(例如从低阻抗区域进入高阻抗区域,或反之),就会发生反射。根据反射系数公式,如果信号感受到的阻抗突然变小,会发生负反射,产生的负电压会使信号波形产生下冲。信号在驱动端和负载端之间来回反射多次,最终就形成了我们所看到的振铃波形。大多数芯片的输出阻抗较低,如果它小于PCB走线的特性阻抗,在没有进行源端匹配的情况下,振铃几乎必然发生。

那么,如何在实际电路中抑制或减小振铃呢?这里有几个实用方法:

- 串联电阻:在靠近接收端的位置串联一个适当的无感阻尼电阻,可以有效减小脉冲幅度和振铃。但电阻值不宜过大,否则会过度衰减信号并延迟前沿。

- 减小引线电感:这是最根本的方法。

- 尽量缩短走线长度。

- 加粗导线和PCB铜箔的宽度。

- 减小信号的传输距离。

- 在传输高速脉冲信号时,选用引线电感小的元器件。

- 优化负载端:尽量减小负载电路的等效电感和电容,特别是要注意避免过长的地线,其形成的地线电感影响不容忽视。

- 电路端接技巧:在数字电路信号线上增加上拉电阻或交流终端负载。例如,接入一个上拉电阻可以将逻辑高电平稳定上拉,而交流终端负载可以在不影响直流驱动能力的前提下,有效抑制高频振铃。

此外,振铃的严重程度与脉冲前沿的上升时间密切相关。上升时间越短,上冲峰值越大。因此,在满足系统速度要求的前提下,应避免过度追求极陡峭的脉冲前沿,这对提升信号质量是有利的。

Smith圆图在RF匹配电路调试中的应用

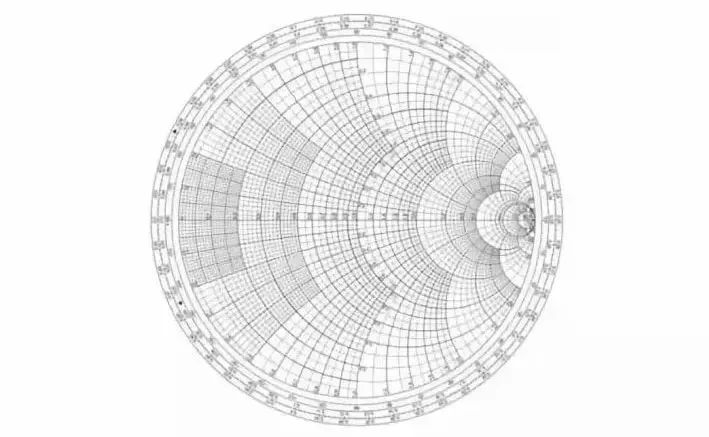

对于射频工程师而言,Smith圆图是一个强大的图形化工具,它能在同一个图上综合反映阻抗$Z$、导纳$Y$、反射系数、驻波比等多种参数。

是不是感觉有些复杂?我们聚焦到最常用的阻抗圆图上来看:

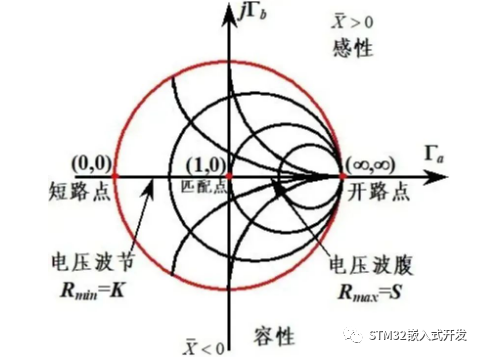

阻抗圆图是将归一化输入阻抗表示在反射系数极坐标系中,其核心规律可以归纳如下:

- 上半圆阻抗为感抗,下半圆阻抗为容抗。

- 实轴代表纯电阻,最外圈的圆代表纯电抗。

- 实轴的右半轴(除开路点)皆为电压波腹点,左半轴(除短路点)皆为电压波节点。

- 三个关键点:匹配点(1, 0)、开路点(∞, ∞)和短路点(0, 0)。

- 图中有两个特殊圆:最大的圆是纯电抗圆,与虚轴相切的圆是匹配圆。

- 运动方向:在圆图上逆时针旋转代表向负载端移动,顺时针旋转代表向波源(信号源)移动。

有趣的是,同一张Smith圆图既可以作为阻抗圆图使用,也可以作为导纳圆图使用(两者中心对称),但在单次操作中必须明确其用途。

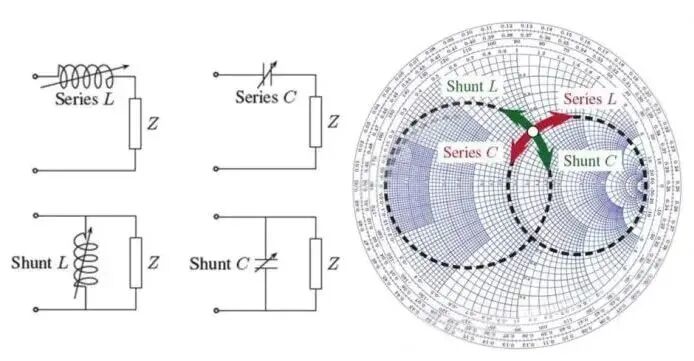

Smith圆图最实用的地方在于,它能直观展示匹配元件的效果。例如,在负载端串联或并联一个可变电感或电容,其在圆图上的运动轨迹是确定的:

其运动规律可以总结为:

- 当使用阻抗圆图时:串联电感使阻抗点顺时针移动,串联电容使其逆时针移动。

- 当使用导纳圆图时:并联电感使导纳点逆时针移动,并联电容使其顺时针移动。

掌握这些基本规律,工程师就能在Smith圆图的辅助下,快速、直观地设计出匹配网络,将复杂的阻抗点“牵引”到中心匹配点,从而解决信号反射和能量传输效率的问题。

理解并控制阻抗是保障高速电路信号完整性的基石。从基本概念到振铃分析,再到利用Smith圆图进行匹配,这是一个系统性的工程思维过程。如果你对这类硬件设计或信号完整性话题感兴趣,欢迎在云栈社区与更多同行交流探讨。