除了舍入注入法,实现乘法运算的收敛舍入还有另一种关键技术——进位修正技术(Carry Correction Technique),其具体流程如下图所示。该方法同样区分向奇收敛(Round to Odd)和向偶收敛(Round to Even),两者核心区别仅在于模式字(PATTERN)的配置不同。

流程图中,我们假设乘积的原始结果小数部分字长为4位,因此用于比较的常数C的低3位为1(即1的个数加1等于小数部分字长)。

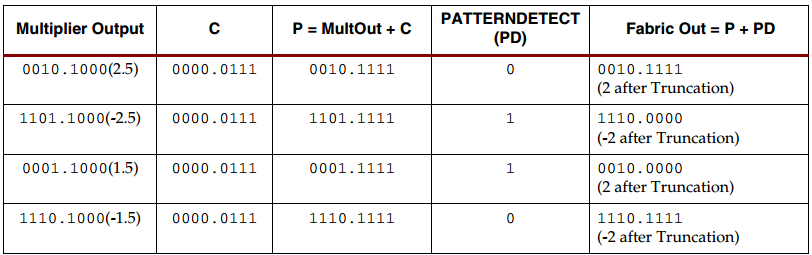

向偶收敛(Round to Even)案例

若进行向偶收敛,则模式字PATTERN的低5位需全部设置为1,其余位为0。具体案例如下表所示:

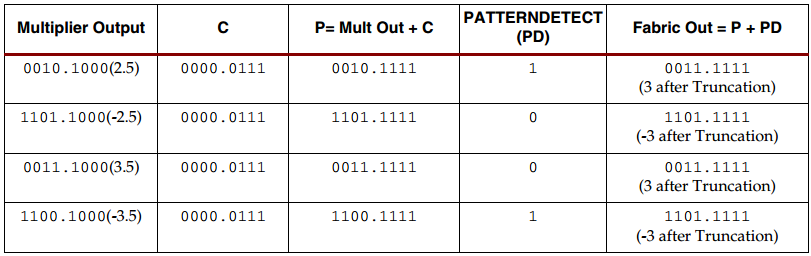

向奇收敛(Round to Odd)案例

若进行向奇收敛,则模式字PATTERN的低4位设置为1,其余位为0。相应案例如下表所示:

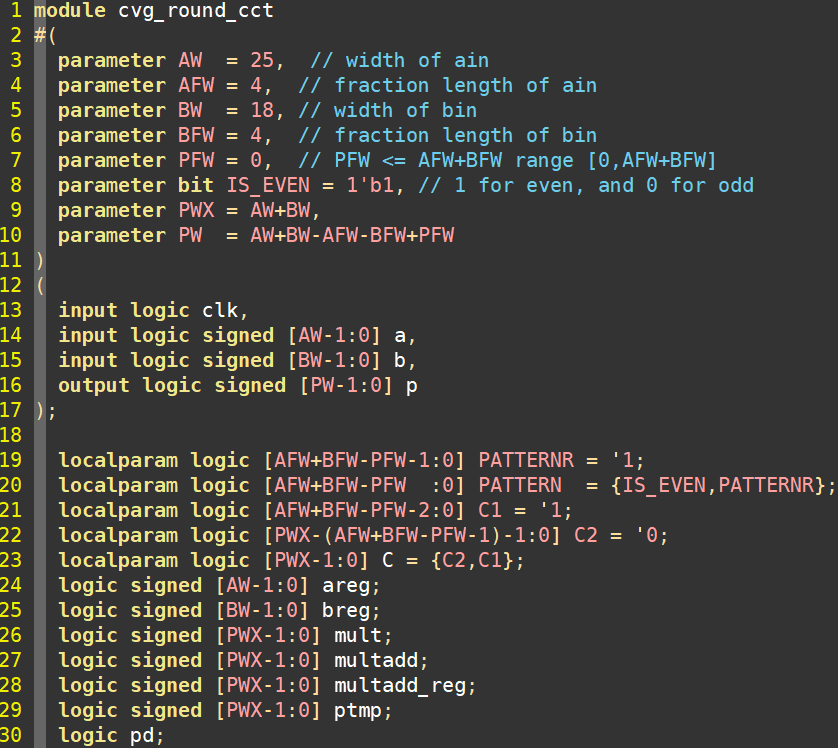

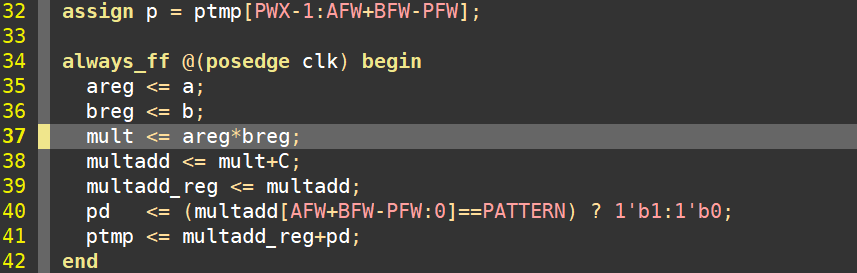

SystemVerilog实现代码

基于上述算法流程,可以编写出如下所示的SystemVerilog代码。在硬件描述语言中实现此类精密舍入逻辑,是高性能计算单元设计的关键。

代码解读:

- 第8行:参数

IS_EVEN 用于指定舍入模式,1 代表向偶舍入,0 代表向奇舍入。

- 第19-20行:利用参数

IS_EVEN 动态生成所需的 PATTERN 常量。

- 第35-38行:这部分逻辑(模式匹配与进位C的生成)可以在一个Xilinx DSP48E模块内完成。

- 第40行:模式检测信号

PD 也可由DSP48E内部电路产生。

- 第41行:最终的加法操作(

P + C)通常需要额外的逻辑资源(如FPGA中的SLICE)来实现。若本DSP48E的输出需传递给下一级DSP48E进行累加,则可将进位信号 PD 作为下级DSP48E的 CARRYIN 输入,从而优化算法实现路径。

下图进一步展示了该模块的输入输出接口:

该设计通过参数化配置,灵活地支持了两种主要的收敛舍入方式,为高精度数字信号处理中的乘法运算提供了关键的舍入解决方案。 |