你是否曾对那些定义了早期计算时代的经典芯片充满好奇?在20世纪70至80年代,像Zilog Z80和Intel MCS-51(也就是我们熟知的8051)这样的8位处理器,曾是家用电脑、嵌入式设备和无数单片机系统的核心。

它们架构简洁、指令集清晰,是许多人踏入计算机世界的第一道门槛,其设计思想至今仍深刻影响着计算机基础领域的学习。

如今,随着FPGA(现场可编程门阵列)技术的普及和开发门槛的降低,我们有了一个绝佳的机会:在FPGA内部用硬件描述语言重新“铸造”这些经典的CPU核心,并围绕它们构建出能真实运行的单板计算机(SBC)。

本文将带你深入了解一个具体的开源实战项目:如何在一块Intel MAX 10 FPGA开发板上,分别实现Z80和8051单板计算机系统。这不仅是对经典的致敬,更是一次从软核CPU到完整外设系统的沉浸式学习过程。

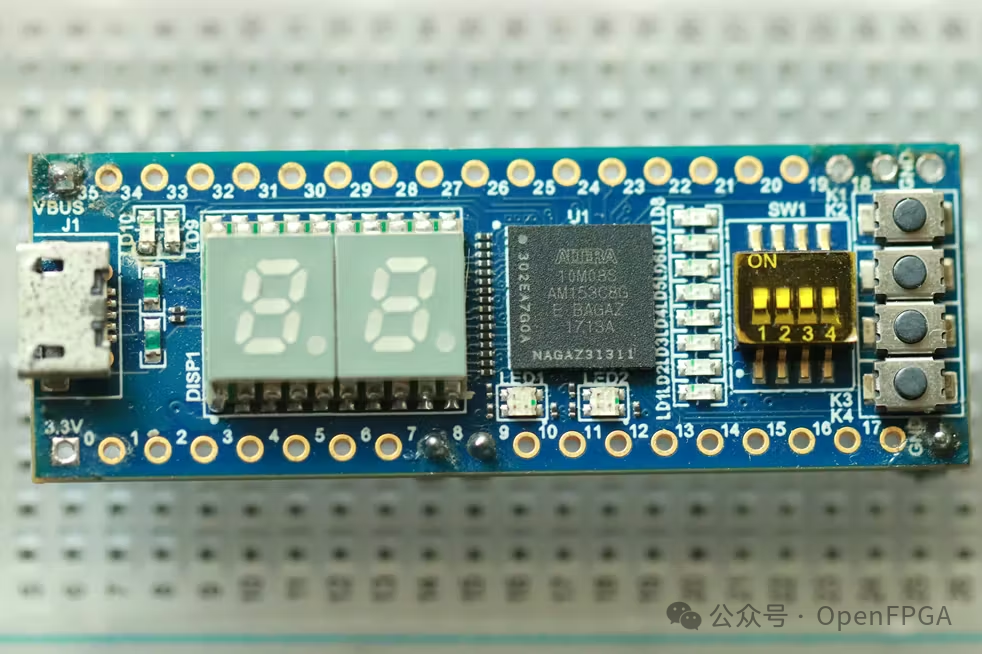

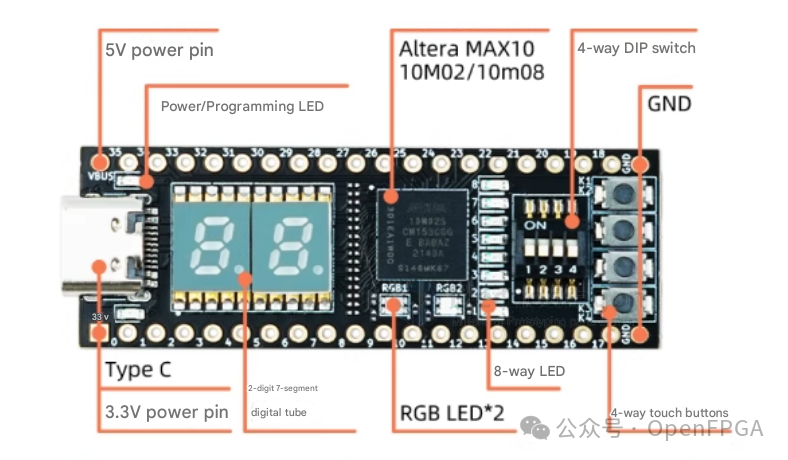

项目使用的硬件平台

本项目的硬件核心是一块基于Intel MAX 10 FPGA的开发板。

- MAX 10 FPGA:采用Intel 14nm工艺的低功耗FPGA,兼具非易失性配置存储器的便捷性和FPGA的灵活性。

- 开发环境:使用Intel官方提供的Quartus Prime集成开发环境进行设计、综合与烧录。

- 丰富外设:板载配置Flash、支持SD卡接口,并提供了大量的GPIO引脚用于扩展。

选择这块板卡的原因显而易见:

- 成本友好:相较于高端FPGA,MAX 10系列具有极高的性价比。

- 学习曲线平缓:对于FPGA初学者而言易于上手。

- 资源充足:其内部的逻辑单元和存储器资源足以模拟复杂的8位CPU系统。

- 扩展性强:充足的引脚为连接各种外围设备提供了可能。

SBC核心架构

该项目成功实现了两套独立的单板计算机系统,它们都运行在同一块FPGA芯片内部。

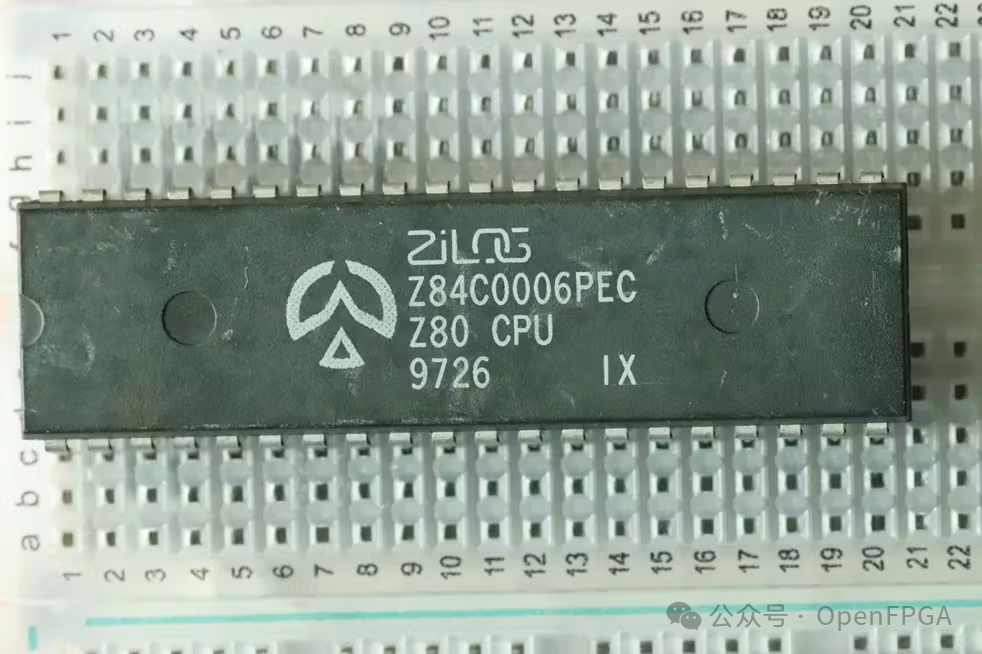

1️⃣ Z80单板电脑

这套系统完整再现了一台基于Z80 CPU的经典微机,其典型架构包括:

- Zilog Z80 CPU软核:在FPGA逻辑中实现的处理器核心。

- 内存系统:包括存放引导程序的ROM和运行程序的RAM。

- 串口通信(UART):用于与PC终端进行通信。

- 视频输出控制器:可驱动显示器(根据具体实现)。

- 键盘输入模块:接收用户输入。

整个CPU子系统完全在FPGA内部运行,能够忠实地执行原始的Z80汇编指令,其行为与一块物理的Z80芯片别无二致。

2️⃣ MCS-51 (8051) 单板电脑

同样,该部分在FPGA内构建了一个完整的8051单片机系统,包含:

- 8051 CPU软核:实现了标准的8051指令集架构。

- 程序存储器(ROM):存放监控程序或用户固件。

- 输入/输出(I/O)模块:管理GPIO端口。

- 串口/UART:提供异步串行通信能力。

- 定时器与中断控制逻辑:用于精准定时和事件响应。

8051作为史上最经典、应用最广泛的单片机架构之一,至今仍是许多微控制器课程的核心教学案例。

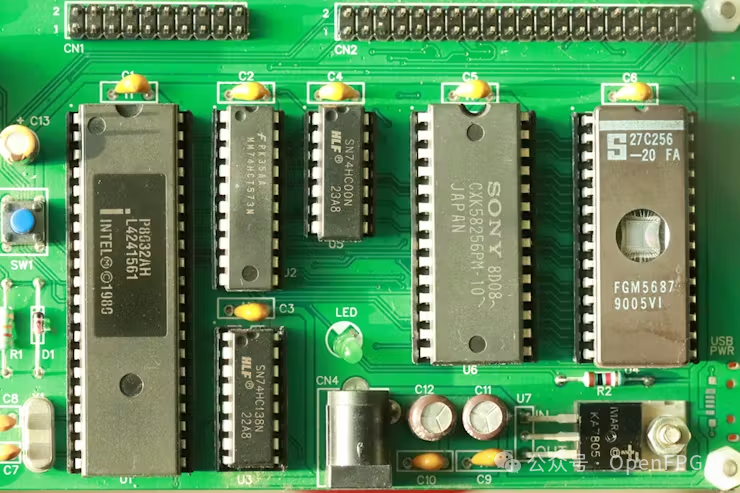

Zilog Z80 SBC 基于MAX10 FPGA

对于一个能够运行Microsoft BASIC 4.7b版本的最小Z80系统,需要约8kB的ROM空间和4kB的RAM空间。MAX10 FPGA提供的资源远多于这个需求,为未来增加更多外设功能留足了余地。

该项目使用Quartus II 18.1版本进行编译和测试。开发者提供了完整的项目归档,你可以在Quartus中直接打开并恢复项目。项目文件夹内甚至包含了预编译好的SRAM目标文件(SOF)和用于烧录Flash的可编程目标文件(POF),这意味着你可以跳过编译步骤直接使用。

通过Micro USB线将开发板连接到电脑,你可以选择写入SOF文件(断电后配置丢失)或POF文件(会存储到板载Flash中,每次上电自动加载)。

下面这段BASIC代码演示了如何在Z80 SBC的I/O端口上进行简单的计数输出:

05 REM COUNT 0 To 255 on PORT 145 (Z80)

10 FOR I = 0 TO 255

20 PRINT I,

30 OUT 145, 255-I

35 FOR J = 0 TO 99 : NEXT J

40 NEXT I

45 FOR K = 0 TO 4095 : NEXT K

46 OUT 145,255

50 END

再来看看更有趣的例子。以下代码同样使用Microsoft BASIC 4.7b,在Z80上实现了一个ASCII字符画(通常是曼德博集分形图)并循环运行。要退出这个无限循环,需要在终端中按下Ctrl+C。

10 FOR Y=-12 TO 12

20 FOR X=-39 TO 39

30 CA=X*0.0458

40 CB=Y*0.08333

50 A=CA

60 B=CB

70 FOR I=0 TO 15

80 T=A*A-B*B+CA

90 B=2*A*B+CB

100 A=T

110 IF (A*A+B*B)>4 THEN GOTO 200

120 NEXT I

130 PRINT " ";

140 GOTO 210

200 IF I>9 THEN I=I+7

205 PRINT CHR$(48+I);

210 NEXT X

220 PRINT

230 NEXT Y

240 PRINT

250 GOTO 10

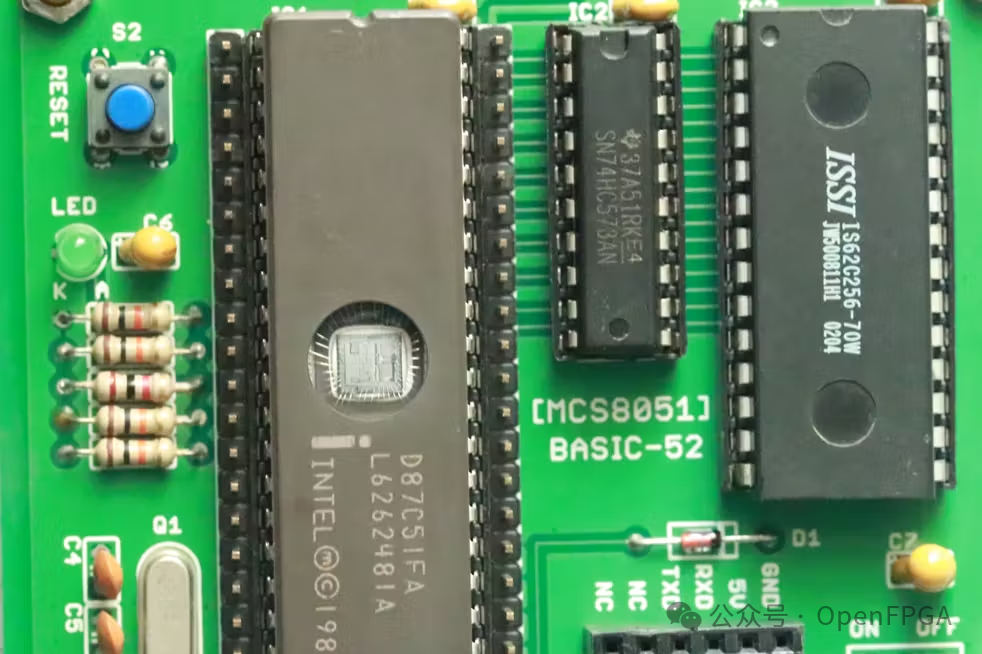

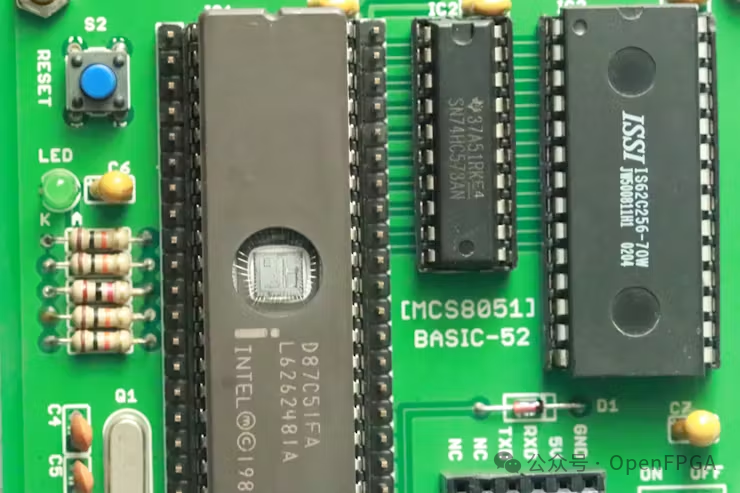

基于MAX10 FPGA的Intel MCS-51单板计算机

对于8051 SBC,项目提供了两个预置的镜像文件供直接使用。这里涉及到一个历史背景:Intel最初将BASIC-52 Ver 1.1解释器公开到了公共领域,但那个原始版本存在不少漏洞甚至隐藏的“彩蛋”。后来,Hans-Jürgen Böhling在2001年2月发布了修复后的BASIC-52 Ver 1.31,并为其增加了I2C总线支持扩展。

镜像一:8kB ROM 和 32kB RAM,频率50 MHz

此镜像包含8kB的代码内存,不支持I2C扩展。系统为用户的BASIC程序提供了32kB的RAM空间。系统时钟通过MAX10内部的锁相环(PLL)从12MHz晶振倍频至50MHz,从而获得更高的执行速度。

镜像二:16kB ROM 和 16kB RAM,频率为11.059200 MHz

此镜像包含完整的16kB代码内存,支持I2C扩展功能。系统为用户程序提供16kB RAM。时钟频率为精确的11.059200 MHz,这个频率特别有利于产生标准波特率的串口通信。尽管频率看似不高,但由于FPGA实现的软核通常是单周期或多周期执行,其性能仍比传统的12时钟周期(12T)的物理8051内核快约10倍。I2C功能在此频率下运行良好。

以下是一个基础的LED流水灯程序,使用BASIC-52语言编写。它通过PORT1端口控制8个LED,让一个亮点从最低有效位(LSB)移动到最高有效位(MSB),然后再移回来,不断循环。

01 REM 8 LED SHIFT

02 REM SHIFT LEFT AND RIGHT

10 LED = 1

20 IF LED <= 80H THEN PORT1 = 0FFH.XOR.LED ELSE GOTO 1000

30 LED = LED * 2

40 FOR J = 0 TO 999 : NEXT J

50 GOTO 20

900 REM RIGHT SHIFT

1000 LED = 080H

1100 IF LED >= 1 THEN PORT1 = 0FFH.XOR.LED ELSE GOTO 10

1120 LED = LED/2

1130 FOR J = 0 TO 999 : NEXT J

1200 GOTO 1100

同样地,我们也可以在8051 SBC上运行ASCII字符画程序。以下是适配了BASIC-52语法的版本:

01 REM ASCII ART SOFT CPU

02 REM ASCII ART FOR MAX10

03 XTAL=50000000

05 TIME=0 : CLOCK 1

10 FOR Y=-12 TO 12

20 FOR X=-39 TO 39

30 CA=X*0.0458

40 CB=Y*0.08333

50 A=CA

60 B=CB

70 I=0

80 T=A*A-B*B+CA

90 B=2*A*B+CB

100 A=T

110 IF (A*A+B*B)>4 THEN GOTO 150

120 I=I+1 : IF I<=15 THEN GOTO 80

130 PRINT " ",

140 GOTO 170

150 IF I>9 THEN I=I+7

160 PRINT CHR(48+I),

170 NEXT X

180 PRINT

190 NEXT Y

200 PRINT TIME

210 GOTO 10

220 END

细心的你可能会发现,上面列出的Z80 BASIC代码和这里的BASIC-52代码只有非常细微的语法差异。另外需要注意的是,如果您的8051 SBC运行在11.059200 MHz频率下,则需要将上面程序中的第3行(XTAL=50000000)注释掉或删除,因为该行是为50 MHz系统声明时钟频率用的。

当然,你也可以选择在BASIC-52的命令提示符下直接声明系统频率:

XTAL = 50000000

上述ASCIIART程序会计算并打印出运行所需的时间(以秒为单位)。为了得到精确的时间,正确设置系统时钟频率(XTAL)是必要的。开发者可以根据自己的需求,灵活调整ROM和RAM的容量组合,并添加其他外设功能。

项目资源

- GitHub仓库:

https://github.com/mit41301/10M08SAM153C8G_Zilog-Z80_Intel-8051

- Hackster项目页:

https://www.hackster.io/mit41301/z80-and-mcs-51-sbc-on-a-max-10-fpga-742a9c

结语

这个项目清晰地展示了一个既有趣又极具教育意义的技术方向:利用现代FPGA的可重构能力,去重建和理解历史上的经典计算系统。它不仅仅是一次“复古计算”的娱乐,更是一个从最底层的逻辑门开始,逐步构建CPU核心、内存总线、外设控制器,最终形成一个完整可交互系统的全栈式学习体验。

无论你是:

- FPGA的入门学习者,想通过具体项目练手;

- 希望深入理解CPU/单片机底层架构的软件或硬件工程师;

- 复古计算爱好者,对老式硬件充满情怀;

- 还是对软硬件协同设计感兴趣,想进行系统级实验的开发者;

这个项目都能提供一个绝佳的起点和丰富的启发。通过亲手让这些经典芯片在硅片中“重生”,你对计算机系统的理解将会更加深刻。欢迎在技术社区进行更深度的开源实战交流与探讨。