当前,车载计算芯片正逐渐成为定义未来汽车性能与竞争力的核心要素。在通用处理器(CPU/GPU)、可编程逻辑(FPGA)和专用集成电路(ASIC)等多种技术路线的角逐中,ASIC凭借其极致的性能、能效比和成本优势,已然成为高级驾驶辅助系统及智能座舱等领域不可或缺的硬件基石。

市场背景与核心驱动力

汽车电子电气架构正经历从分布式向域集中式,乃至中央计算式的深刻变革。这一演进对芯片提出了“更高集成度、更强算力、更低功耗、更高可靠性”的四重严苛要求。

通用处理器(如CPU)和图形处理器(GPU)虽然具备良好的灵活性,但在执行神经网络推理、多传感器数据融合等特定任务时,往往存在能效低下、硬件资源利用率不高等问题。

因此,行业的技术发展呈现出鲜明的专用化趋势。ASIC是为特定应用或算法量身定制的集成电路,其硬件逻辑被固化以最优方式执行目标任务,从而彻底消除了通用架构中的冗余开销。这使得ASIC在计算密度和能效上远超通用处理器。在算法相对成熟且市场需求规模庞大的车载场景中,ASIC是实现性能、功耗和成本三者最佳平衡的关键选择。

这一市场的增长势头显著。根据《2025年车规级ASIC芯片全球行业动态及十五五规划剖析》的数据,2024年全球车规级ASIC芯片市场规模约为23.1亿美元,预计到2031年将达到36.77亿美元,2025至2031年间的年复合增长率为7.0%。

车载ASIC核心架构技术分析

面向不同计算任务的架构分化

车载ASIC并非采用单一架构,而是根据其所承担的核心任务进行针对性设计,主要可分为以下几类:

(1)传感器融合ASIC

传感器融合是ADAS感知层的核心技术,负责处理并融合来自摄像头、雷达、激光雷达、超声波等异构传感器的数据。此类ASIC的架构设计侧重于:

- 高并行数据流引擎:集成多个专用处理单元,以并行流水线方式处理来自不同传感器的原始数据或预处理后的特征,以满足严格的实时性要求。

- 异构计算单元集成:除了通用的向量处理单元,通常会集成NPU阵列用于基于深度学习的目标检测与分类,以及DSP模块用于雷达信号处理等。

- 复杂的内存子系统:传感器数据吞吐量巨大,因此需要设计多层次、高带宽的内存架构。例如,片上SRAM用于缓存高频访问的中间数据,并辅以高带宽外部DRAM接口(如LPDDR5),其内存带宽需求可达120-180 GB/s以支持数据级融合。

- 高带宽互联总线:用于连接内部各处理单元、加速器和内存控制器,确保数据在芯片内高效流动。

(2)ADAS计算ASIC(域控/中央计算)

此类ASIC通常以SoC(片上系统)的形式出现,集成CPU集群、GPU、NPU、各种专用加速器以及丰富的IO接口,承担着从感知融合、路径规划到车辆控制的全栈计算任务。

- 超大规模异构集成:以NVIDIA DRIVE Thor为例,它基于Blackwell GPU架构与Grace CPU,集成了下一代GPU、基于Arm的CPU以及深度学习、计算机视觉加速器,旨在将辅助驾驶、泊车、座舱和信息娱乐功能集中至单一芯片。

- Transformer引擎:针对当前自动驾驶算法中日益重要的Transformer模型,Thor SoC内置了专用的Transformer推理引擎,以加速大规模AI工作负载。

- 芯片互连技术:支持NVLink-C2C等先进互连技术,允许将多个Thor芯片或与其他计算芯片连接,以构建具备更高算力的计算平台。

- 功能安全岛设计:内部划分出独立的安全岛,运行经过ASIL-D认证的锁步CPU核心和安全固件,确保关键控制功能的安全可靠。

(3)边缘AI推理ASIC

这类ASIC设计更为聚焦,通常作为大算力域控芯片的补充,部署在传感器附近,进行前端的数据预处理和轻量级AI推理,以减轻中央计算单元的压力并降低数据传输延迟。

- 高能效NPU核心:其核心是经过极致优化的NPU,支持主流神经网络框架的量化与编译,在有限的功耗预算下提供可观的推理算力。

- 轻量级架构:通常不集成大型CPU集群,内存子系统也相对精简,以追求极致的能效比。

架构设计中的关键硬件模块

一个典型的现代车载AI ASIC(尤其是传感器融合与计算类)内部通常包含以下关键硬件模块:

- CPU集群:通常采用Arm Cortex-A/Cortex-R系列,A系列负责运行复杂的操作系统和应用,R系列(采用锁步设计)负责高安全等级的任务。

- NPU/深度学习加速器阵列:这是AI算力的核心,由大量并行化的乘加计算单元构成,专为卷积、矩阵运算等操作优化。

- 视觉预处理单元:用于处理摄像头原始数据,执行去马赛克、降噪、HDR融合等操作。

- 通用向量处理器/GPGPU:用于处理一些非标准或处于持续演进中的算法任务。

- 专用硬件加速器:如用于目标跟踪的卡尔曼滤波器硬件单元、用于路径规划的搜索算法加速器等。

- 复杂的内存层次结构:包括各级缓存、共享的片上SRAM、以及通过高速接口连接的外部DRAM。

- 高速片上互联网络:负责所有内部模块间的数据通信。

- 丰富的外设接口:包括车载以太网、PCIe、CAN-FD、LIN等,用于连接传感器和执行器。

功能安全(ISO 26262)合规性设计

标准要求概述

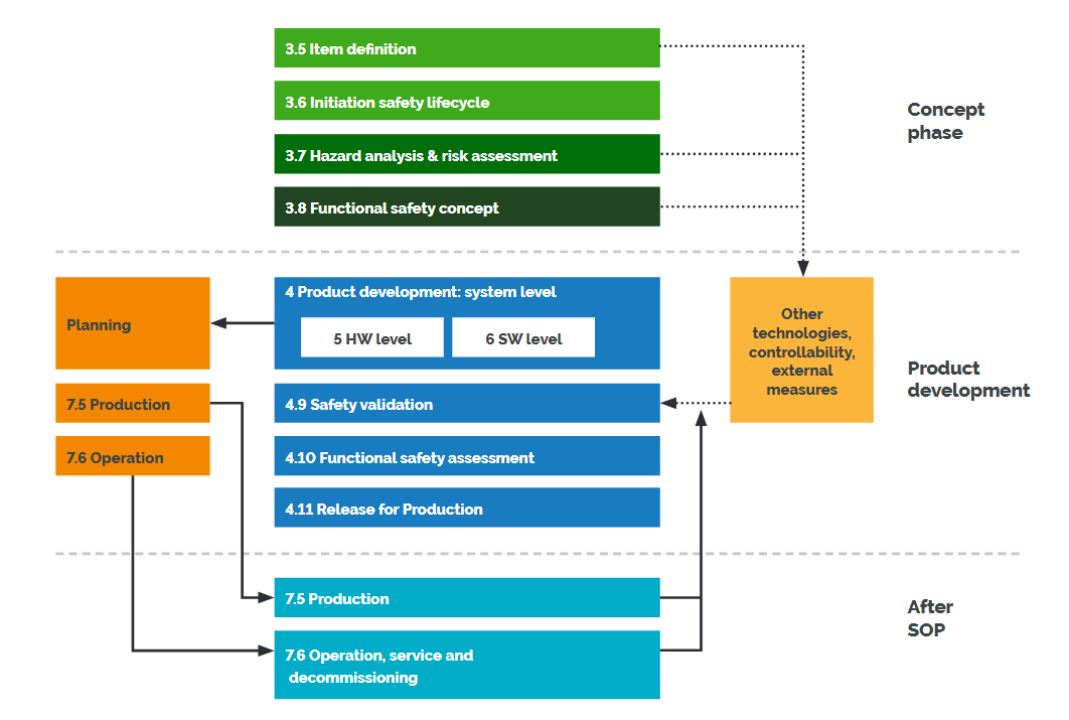

ISO 26262《道路车辆功能安全》是汽车电子系统开发的强制性安全标准。它定义了汽车安全完整性等级(ASIL),其要求贯穿于整个产品生命周期,从概念、开发到生产、运营。对于涉及驾驶安全的车载ASIC,尤其是用于ADAS和自动驾驶的芯片,通常需要满足最高的ASIL D等级要求。

硬件设计的关键要求

ISO 26262对硬件设计提出了系统性要求,旨在避免、检测和控制随机硬件故障及系统性故障。主要实现手段包括:

(1)安全机制的植入

- 锁步双核或多核:对于安全相关的CPU核心,采用两个物理核心执行相同指令,并实时比较输出。一旦结果不一致,则触发安全状态。

- 内存保护单元与错误校正码:MPU用于隔离不同安全等级的任务,防止非法内存访问。ECC用于检测和校正SRAM、DRAM中的单位/多位错误。

- 内置自测试与逻辑内置自测试:在芯片启动或运行时,自动对存储器和逻辑电路进行测试,以检测潜在故障。

- 看门狗定时器:监控处理器运行状态,防止程序跑飞。

(2)架构度量指标达标

ISO 26262-5要求对硬件架构进行量化评估,计算单点故障度量、潜在故障度量和随机硬件故障概率度量。设计时必须通过冗余、诊断等手段使这些指标达到目标ASIL等级的要求。

(3)安全相关硬件的独立与隔离

在SoC内部划分独立的“安全岛”,该区域拥有独立的电源、时钟、复位和调试接口。安全岛上运行经过认证的软件,并仅通过受控的通道与非安全区域进行通信。这是实现芯片级功能安全架构的通用做法,涉及到深层次的硬件安全设计理念。

未来趋势与挑战

Chiplet与先进封装

随着单颗大尺寸SoC的设计复杂度、制造成本和良率挑战激增,Chiplet(芯粒)技术成为必然选择。通过将大型SoC分解为多个功能化的、可采用不同工艺节点制造的小芯片(如CPU、NPU、IO Die),并使用2.5D/3D先进封装技术进行集成,可以实现更灵活的设计、更快的上市时间和更优的成本效益。这将是未来高端车载ASIC/SoC的主流架构形态。

先进制程的持续演进

为追求更高的性能密度和能效,车载ASIC将持续向更先进的半导体制造工艺迁移。从当前的7nm/5nm主流节点,向4nm、3nm甚至更先进的制程进军。然而,车规芯片对可靠性、寿命和温度范围的要求远高于消费电子,先进制程的车规化认证将是芯片厂商面临的巨大挑战。

软硬件协同设计与算法-架构协同优化

软硬件协同设计已成为高性能ASIC开发的标配,即算法开发与芯片架构设计深度联动。通过分析目标神经网络的计算图、数据流和内存访问模式,硬件架构师可以设计出最匹配的NPU微架构、内存层次和片上网络,从而最大化硬件利用率。这要求团队对计算机体系结构有深刻的理解。

小结

综合来看,车载ASIC架构技术正沿着高性能、高能效、高集成度、高安全性的方向飞速发展。

市场在ADAS的强劲需求下持续扩张。技术路径因计算任务的不同,呈现出传感器融合ASIC、中央计算ASIC和边缘AI ASIC的架构分化。ISO 26262功能安全标准已深度融入芯片硬件设计的每一个环节,成为产品准入的硬性门槛。性能竞赛的焦点正从单纯追求TOPS(每秒万亿次运算),转向追求在真实场景下的有效算力和极致能效比。

未来,Chiplet、先进制程、软硬件协同设计将成为推动车载ASIC突破现有瓶颈、迈向下一代的核心技术。对于汽车制造商和芯片厂商而言,深刻理解并掌握车载ASIC的架构技术与安全要求,是赢得智能汽车时代竞争的关键所在。

—end—

推荐阅读: