在芯片这个精密的世界里,内部数以亿计的晶体管完成计算,但它们如何与外部“对话”,接收指令并输出结果呢?这就离不开一个看似微小却至关重要的结构——Bond Pad(焊垫,也称焊盘)。它位于芯片的最顶层,是连接芯片内部“灵魂”与外部封装“躯体”的唯一物理桥梁。

简单来说,你可以把Bond Pad想象成芯片的“港口”或“接线端子”。芯片核心电路产生的电信号,通过内部金属布线抵达这些焊垫;然后,通过键合工艺(如打金线或植凸点),焊垫再与封装外壳的引脚相连,最终通向我们熟悉的电路板。因此,它承担着信号传输、电源供给、接地等核心电气功能,其设计与可靠性直接关系到整颗芯片的成败。

Bond Pad的结构与材料:不止一层金属

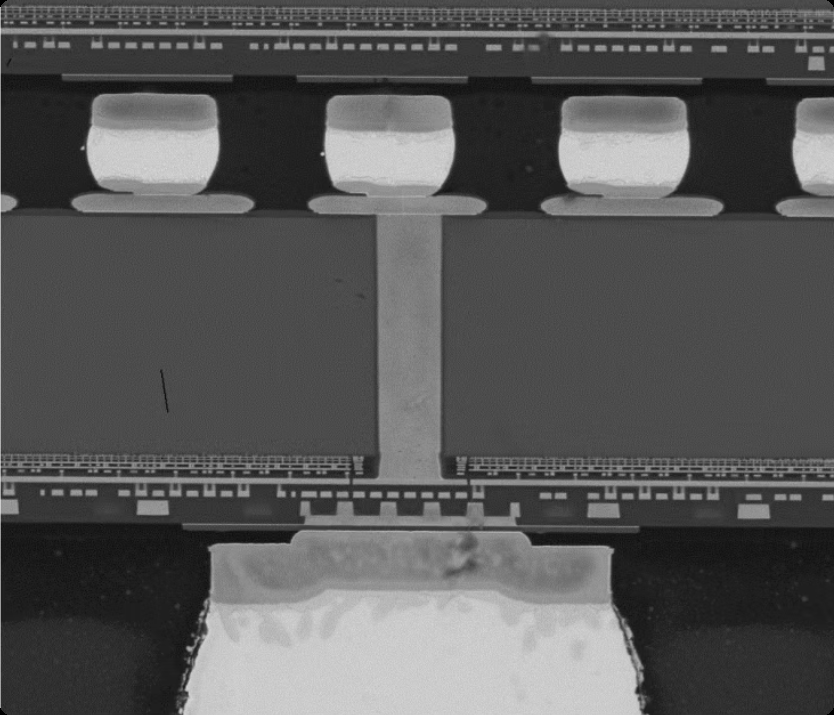

Bond Pad可不是一块简单的金属片。为了同时满足机械强度(承受键合压力)、优良的电学性能(低电阻)以及与前后道工艺的兼容性,它被设计成一个精密的多层“三明治”结构。

从表面向芯片内部看,其典型层级包括:

- 键合层:最表层,直接与键合线或凸点接触。常用材料是铝(Al)或铝合金,因其成本低、工艺成熟且与金/铜线键合兼容性好。在高频、高可靠性应用中,也会使用导电性更优、抗电迁移能力更强的铜(Cu)。

- 阻挡层:位于键合层之下,核心作用是防止上下层金属相互扩散(例如防止铜原子扩散到介电层中),同时阻挡外部杂质侵入。常用材料有氮化钛(TiN)、钛钨(TiW)或钽(Ta),厚度极薄,通常在0.1至0.3微米。

- 黏结层:用于增强Bond Pad金属堆叠与下方芯片钝化层(绝缘层)之间的附着力,防止剥离。多采用钛(Ti)或铬(Cr),厚度更薄,约0.05至0.15微米。

- 金属布线层:这是Bond Pad与芯片内部核心电路连通的“最后一公里”。在传统工艺中多为铝,而在先进制程中已普遍采用铜互连。

此外,针对特定需求还会有附加层:

- 抗氧化层:对于铜基焊垫,表面常会覆盖一层极薄的金(Au)或通过化学处理形成钝化膜,防止铜在空气中氧化,保证可焊性。

- 应力缓冲层:在一些大功率芯片中,可能会引入镍(Ni)等层,用于吸收和缓冲键合过程或温度变化产生的机械应力与热应力。

设计规则:与封装工艺的“精确舞蹈”

Bond Pad的设计绝非孤立进行,它必须与后续的封装工艺严丝合缝地匹配。主要考量因素包括:

- 尺寸与间距:焊垫的典型尺寸在50μm x 50μm到100μm x 100μm之间。尺寸大小需与键合线直径(如25μm金线)和键合设备的精度相匹配——太小了键合工具对不准,太大了则浪费宝贵的芯片面积。相邻焊垫的中心间距(Pitch)直接决定了芯片的I/O密度。传统打线封装间距通常大于50μm,而采用倒装芯片技术时,间距可以缩小到150μm甚至更小。

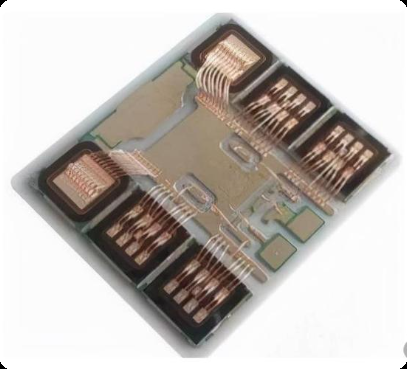

- 布局规划:焊垫在芯片上的排列方式也受封装类型影响。周边排列常用于打线封装,焊垫像“护城河”一样分布在芯片四周;而为了满足高I/O数量需求,阵列式排列(整个芯片表面分布)则成为倒装芯片封装的首选。

- “禁区”规则:为了防止键合时产生的机械应力损伤下方脆弱的晶体管,Bond Pad正下方的区域通常禁止布置任何有源器件。焊垫通过一段细细的“颈部”金属线与内部全局布线连接。

- 与封装技术对应:

- 打线键合:要求焊垫表面洁净、平整、无氧化。铝垫可以直接与金线通过超声波和热压形成金属间化合物(如AuAl2)实现连接。

- 倒装芯片:需要在焊垫上制作锡铅或铜柱凸点。此时,焊垫结构上还需增加“凸点下金属化层”,这是一个额外的多层结构,用于提供良好的粘附性、扩散阻挡和可焊性。

常见失效模式:可靠性挑战

在严苛的服役环境下,Bond Pad的失效是导致芯片故障的重要原因之一。了解这些失效模式,对于芯片设计与可靠性工程师至关重要。这通常涉及到对材料科学和计算机体系结构底层物理实现的深刻理解。

- 金属间化合物脆裂:在高温或长期使用后,键合层金属(如Al)与键合线金属(如Au)界面处会生长出金属间化合物。适量的化合物有助于连接,但过度生长会形成厚而脆的层,在热应力下容易开裂,导致连接失效。

- 阻挡层失效:如果阻挡层太薄或有缺陷,就无法有效阻挡扩散。例如铜原子可能穿过阻挡层污染下方的器件,或者外部杂质侵入导致腐蚀。

- 层间剥离:各层材料之间的热膨胀系数不匹配,在温度循环中会产生剪切应力,可能导致层与层之间分离(分层)。

- 电迁移:在高电流密度作用下,金属原子会沿着电子流动方向进行定向迁移,从而在焊垫或互连线上形成空洞(断路)或小丘(短路)。

- 腐蚀与氧化:如果保护不当,焊垫表面可能被环境中的湿气、氯离子等腐蚀,或氧化生成不导电的氧化膜,影响可焊性和导电性。

- 机械损伤:键合过程中压力控制不当,可能压碎焊垫下的介质层,或对焊垫本身造成物理损伤。

应对这些失效,需要从材料选型、厚度与结构设计、工艺参数控制以及应用场景防护等多维度进行优化。例如,选择形成稳定金属间化合物的材料组合、确保阻挡层的完整性与足够厚度、在铜垫表面增加有效的抗氧化涂层等。

总结与展望

从早期简单的铝垫金线键合,到如今先进制程中复杂的铜基多层堆叠与倒装芯片凸点下的精细化金属化体系,Bond Pad的演变史,就是一部围绕更高可靠性、更低信号损耗、更小尺寸与更高集成度而持续创新的历史。

它虽处芯片“边缘”,却肩负着中枢连接的使命。随着芯片朝着3D集成、异质集成、更高频率和功率密度的方向迈进,Bond Pad的设计与材料创新将继续成为支撑摩尔定律前行的重要一环。对于希望深入计算机科学底层硬件奥秘的工程师和爱好者而言,理解这个微小的接口,是洞察芯片如何“连接世界”的关键一步。

如果你对这类硬核技术细节的讨论感兴趣,欢迎到云栈社区的相关板块,与更多同行一起交流切磋。 |