在功率芯片的世界里,击穿电压(BV) 是衡量器件耐压能力的核心指标,它定义了芯片在偏置下能够承受的最高电压而不发生雪崩击穿的极限值。然而,在实际制造和应用过程中,芯片的实际击穿电压往往会偏离设计值,甚至出现异常退化,这种现象被称为 BV失效。理解BV失效的物理本质,对于提升芯片的可靠性至关重要。

什么是BV失效?

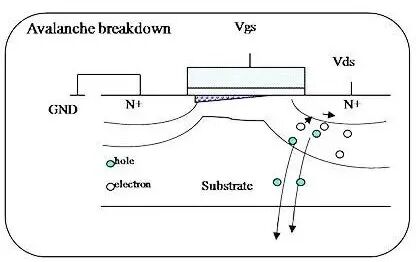

简单来说,BV失效是指功率器件的击穿电压低于设计规格或发生异常波动的现象。在理想情况下,芯片应能稳定工作在额定的电压范围内;当电压超过某一临界值时,才会发生可控的雪崩击穿。但当BV失效发生时,芯片可能在远低于设计电压的点就提前击穿,或者在击穿后出现电压回跳等异常现象,导致芯片无法正常工作甚至永久损坏。

那么,究竟是哪些因素会导致BV失效呢?

一、热预算不当

在芯片制造过程中,热预算的控制至关重要。无论是氧化、扩散还是退火,每一次高温处理都可能在材料中引入晶体缺陷。过高的温度或不当的热处理会使原子偏离晶格位置,形成位错、层错等缺陷。这些缺陷就像晶体内部的“薄弱点”,在反向电压作用下容易成为局部击穿的起点。特别是在宽禁带半导体如碳化硅中,热过程可能自发产生堆垛层错,这些缺陷会显著影响器件的理想因子和势垒高度,并最终导致反向击穿电压的退化。

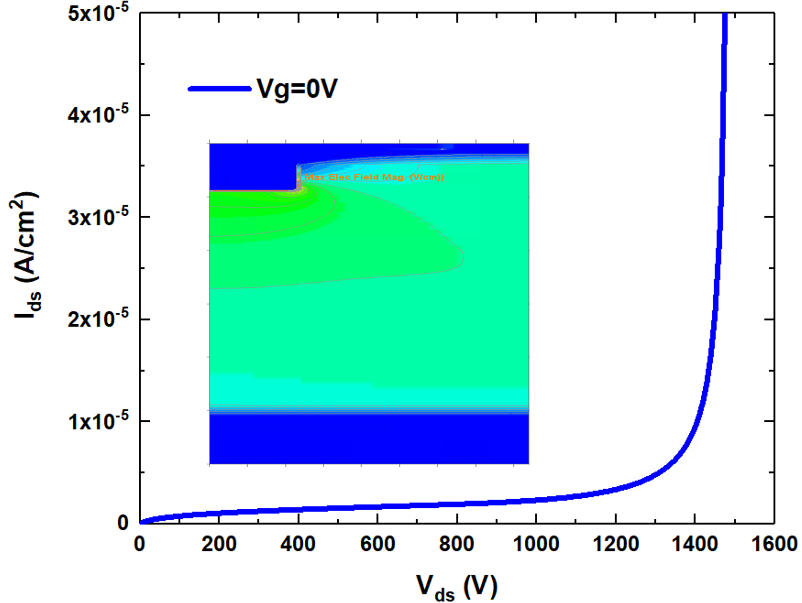

二、电场集中

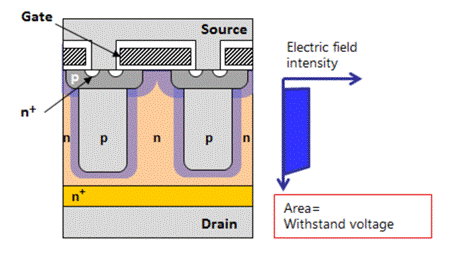

场板是功率器件中常用的边缘终端结构,用于缓解PN结边缘的电场拥挤效应。然而,不当的场板设计会适得其反。当场氧化层厚度与结深不匹配时,场板末端会产生严重的电场集中,导致局部电场强度远超材料临界值,从而引发早期击穿。这种电场集中现象在SiC功率器件中尤为突出,因为SiC的临界击穿电场很高,对任何微小的电场畸变都极为敏感。场板终止结构在金属终端处的氧化层内容易产生严重的电场拥挤,这不仅限制了器件的击穿电压,还埋下了氧化层可靠性的长期隐患。

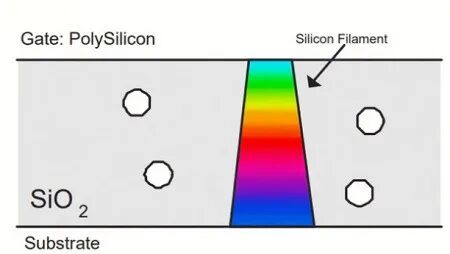

三、介质材料的特性差异

栅氧化层和钝化层的材料选择直接关系到器件承受电压的能力。氧化硅和氮化硅具有不同的介电常数和临界击穿场强,它们在器件中的分布会影响电场的均匀性。更重要的是,不同介质与半导体衬底的界面质量千差万别。例如,在SiC MOSFET中,SiO₂栅氧层与SiC衬底之间存在晶格失配,导致界面处存在高密度的缺陷态。这些缺陷在电场作用下会捕获载流子,引发阈值电压漂移,同时也在局部区域造成电场畸变,最终影响击穿特性。

四、衬底缺陷

衬底材料的晶体质量是决定BV稳定性的基石。无论是硅还是宽禁带半导体,衬底中存在的位错、堆垛层错等晶体缺陷,都是导致击穿电压退化的根本原因。研究发现,根据缺陷在器件有源区中的位置和尺寸不同,会产生不同类型的BV异常现象。缺陷区域会打乱原本均匀的电位分布,导致局部电流密度异常升高,从而诱发早期击穿。在宽禁带半导体如SiC和GaN中,由于材料生长技术尚未完全成熟,衬底中的位错密度远高于硅材料,这使得衬底缺陷对BV失效的影响更为突出。

BV失效是多种因素交织作用的结果。从热预算对材料完整性的破坏,到场板设计中的电场集中,再到不同介质材料的界面特性,直至衬底本身的晶体缺陷——每一个环节都可能在纳米尺度上埋下击穿的隐患。在功率芯片向着更高电压、更小尺寸迈进的今天,对BV失效机理的深刻理解与精准控制,已成为保障芯片可靠性的核心课题之一。只有将这些因素纳入设计与制造的全局考量,才能真正驾驭电压的极限。对这类底层原理的探讨,是推动技术发展的关键,这也是为什么 云栈社区 鼓励开发者们深入交流基础技术问题。 |