自1957年硅晶闸管(SCR)诞生以来,功率半导体技术已历经数十年的发展与演进。如今,它已成为现代电力电子系统中不可或缺的核心组成部分。

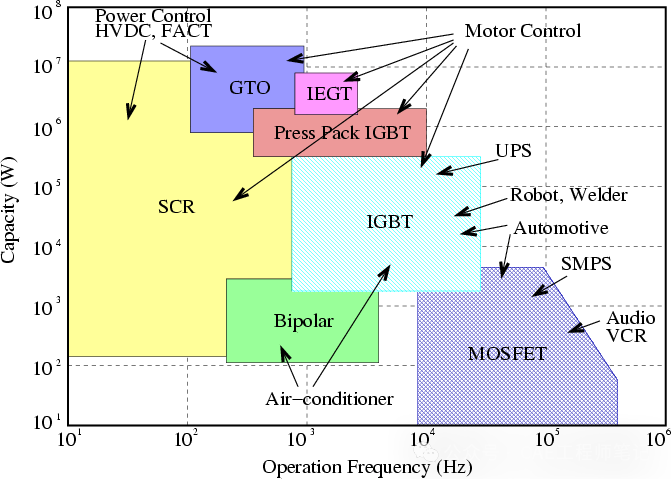

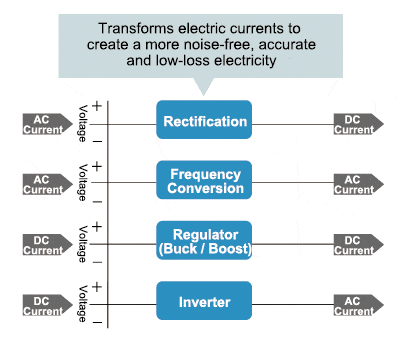

功率半导体器件,如MOSFET(金属氧化物半导体场效应晶体管)和IGBT(绝缘栅双极晶体管),凭借其在电能转换效率与可靠性方面的优势,构成了现代电力电子技术的基石,在确保各类电气设备稳定高效运行中扮演着至关重要的角色。

尽管基于硅(Si)的功率半导体已取得了令人瞩目的成就,但在应对新型应用对能耗和可靠性的更高要求时,仍面临挑战。近年来,以碳化硅(SiC)和氮化镓(GaN)为代表的宽禁带半导体材料崭露头角,展现出巨大的潜力。相比传统硅材料,它们具有更高的电子迁移率、更高的击穿电场强度以及更宽的工作温度范围。SiC和GaN器件能够在更高的电压和频率下稳定工作,同时具备更低的导通与开关损耗,有望突破传统硅器件在能耗与可靠性方面的瓶颈,推动整个功率电子领域向前发展。

许多成熟的硅(Si)工艺已经成功转移到SiC器件的制造中。然而,SiC独特的材料特性要求开发针对性的特定工艺,其参数必须经过仔细优化和验证:

- 刻蚀(Etch): SiC对化学溶剂呈惰性,因此通常仅干法刻蚀可行。需要开发的要点包括掩膜材料、掩膜刻蚀选择性、气体混合物、侧壁斜率控制、刻蚀速率以及侧壁粗糙度等。

- 衬底减薄(Substrate thinning): 该工艺用于降低低压器件(≤1.7 kV)的电阻,并便于操作高压器件制造所需的厚外延晶圆。SiC材料的硬度要求特殊的工艺配方。

- 掺杂(Doping): 由于SiC的高熔点及掺杂剂在其中的低扩散常数,传统的热扩散工艺在SiC中不实用。需要评估注入种类、剂量、能量、温度及掩膜材料等。注入后的SiC再结晶与注入激活退火方法(如炉管退火、RTA快速热退火、激光退火等)、温度、升温速率、时长及气体流量等参数也需要专门开发。同时,必须选择合适的退火保护覆盖层,以最小化SiC晶圆表面的退化。

- 金属化(Metallization): 需要评估与SiC热膨胀系数(CTE)匹配的金属,选择抗蚀剂类型并开发底切剥离轮廓,同时开发金属蒸发/剥离工艺以及溅射金属沉积和干法刻蚀工艺。

- 欧姆接触形成(Ohmic contact formation): SiC/金属界面的高势垒会导致整流接触。形成欧姆接触通常需要在金属沉积后进行退火。需要优化退火温度、升温速率、时长、气体流量并保持表面质量。

- 栅氧化层(Gate oxides): SiC/二氧化硅(SiO₂)界面质量差会降低MOS(金属氧化物半导体)反型层迁移率。需要开发有效的界面钝化技术以改善其质量。

- 透明晶圆(Transparent wafers): 当使用光学显微镜确定焦平面时,透明的SiC晶圆会使关键尺寸(CD)- SEM测量复杂化。其他计量工具需要调整软件/增益/硬件,以适配SiC不透明的波长。

- 相对缺乏平面性(Relative lack of planarity): SiC晶圆相对缺乏平面性,会使光刻和其他工艺(尤其是高压器件所需的厚漂移外延层)复杂化。高温工艺可能进一步负面影响晶圆的平整度。

- 绝缘介质(Insulation dielectrics): 由于无法生长厚的热氧化层,厚介质通常通过沉积方式覆盖在SiC上。沉积介质容易引入缺陷,必须评估其对边缘终端和器件可靠性的影响。

尽管SiC MOSFET和JBS(结势垒肖特基)二极管是电力电子的主力,但上述制造工艺适用于所有类型的SiC器件,包括JFET、BJT、晶闸管、IGBT和PiN二极管。

一、SiC刻蚀与衬底减薄

由于其极高的硬度,SiC在室温下不受单一酸的侵蚀。因此,湿法刻蚀需要高温下的腐蚀性混合物,其缺点包括需要专用的洁净室设备与区域,以及无法使用传统掩膜材料进行选择性刻蚀。为此,业界开发了具有实用刻蚀速率和良好选择性的干法刻蚀技术,如反应离子刻蚀(RIE)和电感耦合等离子体(ICP)刻蚀,用于SiC的深度图案化。

为硅工艺开发的商用RIE系统经过调整后可用于刻蚀SiC。常用的刻蚀气体体系通常基于氟、氯或溴:

- 氟基:SF₆, CF₄, NF₃, BF₃, CHF₃

- 氯基:Cl₂, BCl₃, SiCl₄

- 溴基:Br₂, IBr

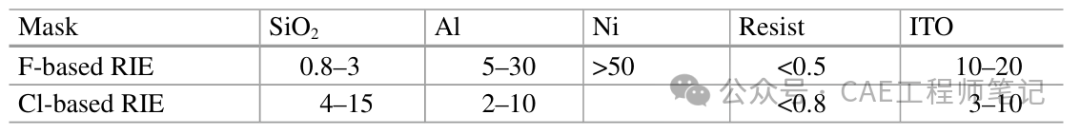

由于SiC材料硬度高,其刻蚀速率相对于硅较低,且传统光刻胶掩膜的选择性不足。因此,通常使用金属(如铝Al和镍Ni)、ITO(氧化铟锡)及SiO₂作为刻蚀掩膜材料。下表给出了各种刻蚀掩膜材料在特定条件下的代表性刻蚀选择比值。

通常会在刻蚀过程中引入O₂和Ar气流,以增强碳原子的去除,从而促进刻蚀过程。必须精确调整腔室压力、气体流速和射频功率等参数以优化刻蚀效果。与硅刻蚀类似,电感耦合等离子体(ICP)技术相比传统RIE能提供更高的刻蚀速率,常用于更深的刻蚀需求。

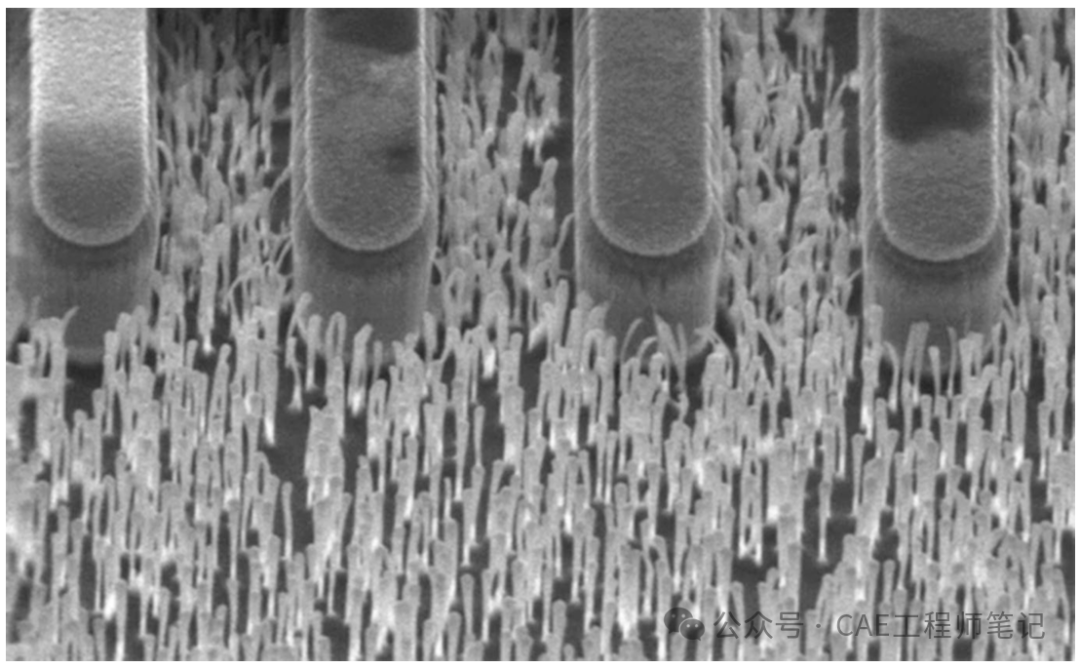

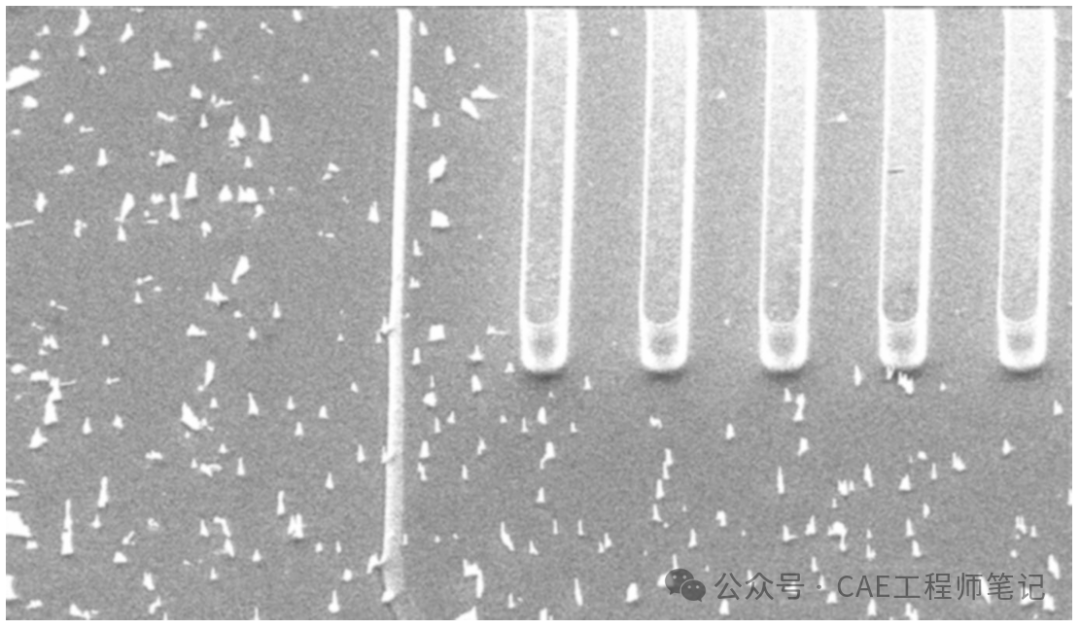

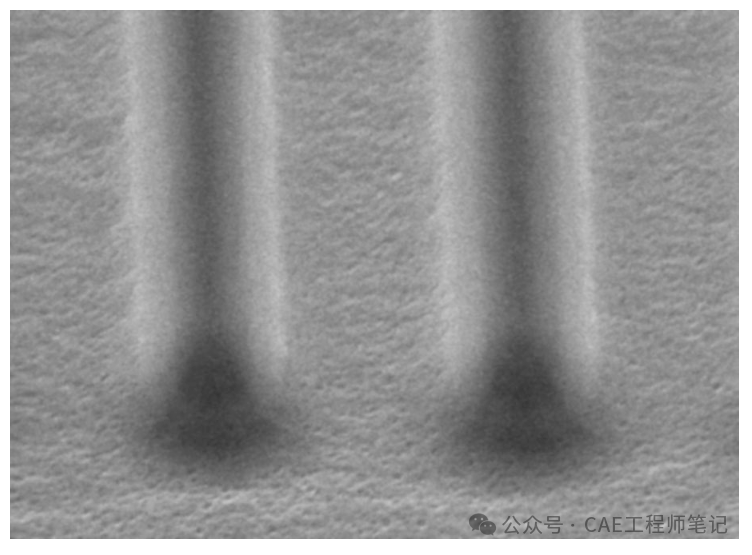

使用金属掩膜进行SiC RIE时,一个常见问题是微掩膜诱导的柱状“草形”表面粗糙度。如下图所示,在RIE过程中从铝掩膜上溅射出的铝颗粒可能形成非挥发性的Al₂O₃,这些颗粒被吸附在SiC表面形成微掩膜,导致刻蚀后形成柱状的“草形”粗糙结构。

一旦形成,这种薄薄的“草形”柱状结构可以通过热氧化工艺被部分或完全消耗掉,如下图所示。然而,这种“返工”操作具有不良副作用,即会同时减薄其他SiC特征结构,最终可能影响器件的设计参数。

已有研究证明,在RIE过程中引入H₂气流可以促进挥发性AlH₃的形成,从而去除溅射的铝颗粒,消除微掩膜诱导的SiC柱状物。使用SiO₂作为掩膜可以避免刻蚀过程中的金属污染。然而,由于SiO₂拐角在刻蚀中容易圆化,形成垂直侧壁可能更具挑战性。总体而言,刻蚀速率通常与图形的纵横比有关,大面积未掩膜的区域可能刻蚀得更快。

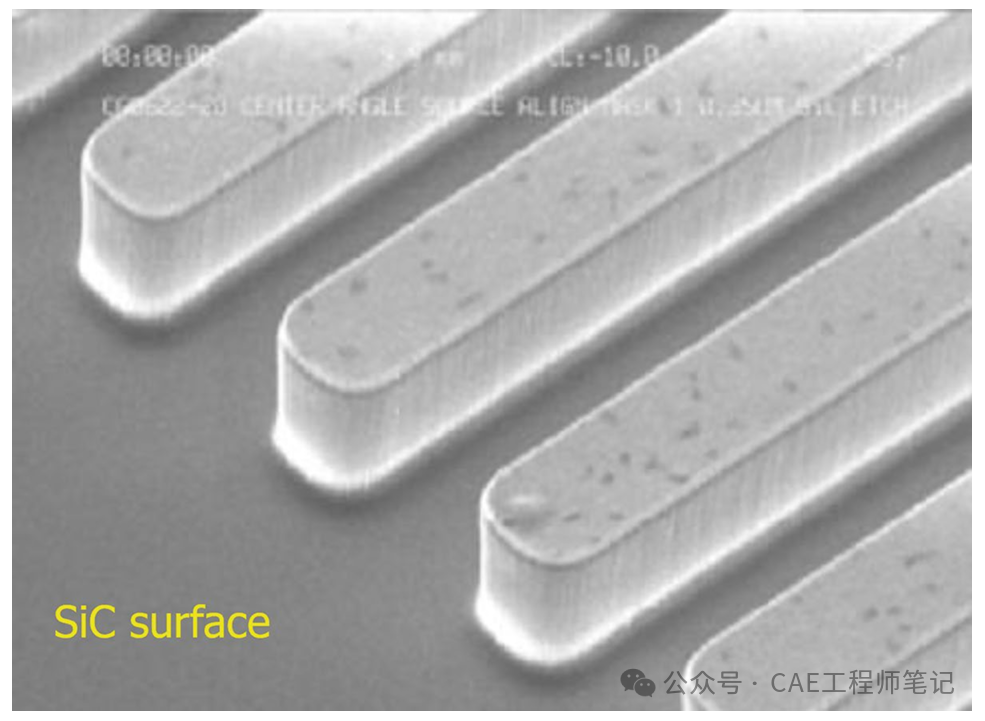

经过优化的氟基RIE工艺可用于刻蚀出深而垂直的源柱侧壁,如下图的SEM图像所示,该工艺采用了自对准技术。RIE设备的参数经过优化,旨在消除微掩膜并形成垂直的侧壁轮廓。图案化的Cr-Al复合掩膜有助于促进刻蚀过程,其中Cr层能增强金属层与SiC表面的粘附性。通过优化刻蚀参数和掩膜材料,实现了对源柱刻蚀深度的精确控制以及最小的侧壁粗糙度。

掩膜的图案化通常采用标准的步进式光刻技术完成,该技术能以高重复性和精度解析出窄线宽。抗蚀剂的厚度和轮廓由具体的工艺要求决定,例如关键线宽、刻蚀深度和后续的金属剥离工艺。

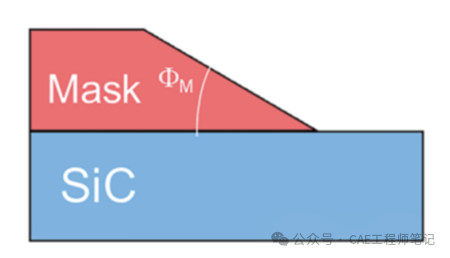

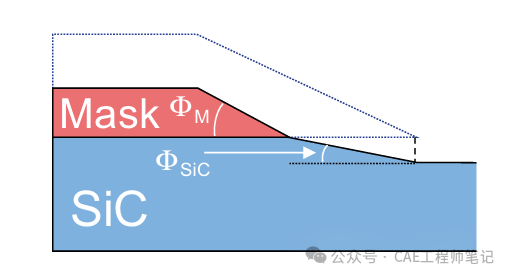

在某些应用中,例如为了形成斜角边缘终端以减轻器件边缘的电场集中,或者为了注入、金属连续性等目的,形成倾斜的SiC台面可能是必要的。有多种技术可用于RIE刻蚀倾斜SiC台面。一种标准方法是先在整片沉积于晶圆上的氧化物层上进行光刻并图案化抗蚀剂。然后,将图案化的抗蚀剂暴露于深紫外光下进行硬化处理,这能增加其对底层氧化物的刻蚀选择性。随后,通过烘烤使抗蚀剂回流至所需的倾斜角度。接着,通过RIE将这种回流(倾斜)的抗蚀剂轮廓转移到其下方的氧化物层上。这就为后续的SiC深刻蚀创建了一个倾斜的氧化物掩膜,如下图所示。该工艺必须仔细优化,因为硬化后的抗蚀剂可能在RIE结束时留下难以去除的残留物。

如上图所示的倾斜氧化物掩膜,通过RIE将其形状进一步转移到底层的SiC中,从而形成倾斜的SiC台面。图案化后的SiC倾斜台面如下图所示。在SiC RIE过程中,倾斜氧化物掩膜自身的减薄程度取决于具体的刻蚀参数、持续时间和材料间的刻蚀选择比。

在许多情况下,RIE工艺必须产生角度精确可控的SiC台面,以最大化器件的电学性能。

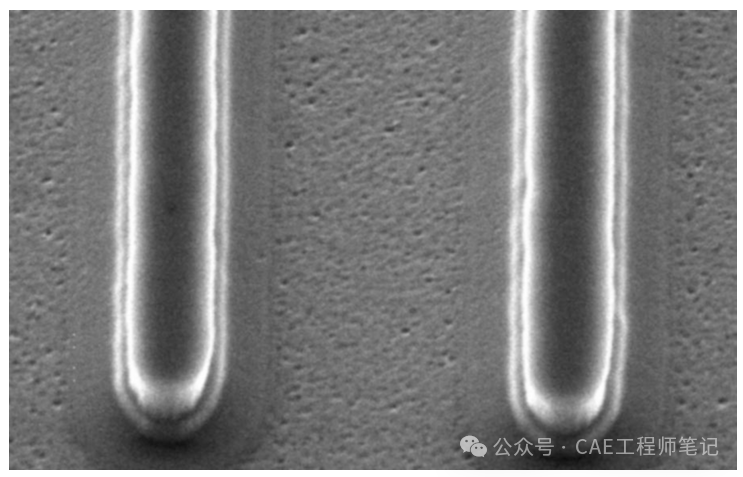

下图所示的SEM图像显示了为形成SiC倾斜台面,在整片氧化物层上图案化的初始抗蚀剂结构。

下图则显示了经过120°C烘烤回流后的深紫外硬化抗蚀剂的形貌。

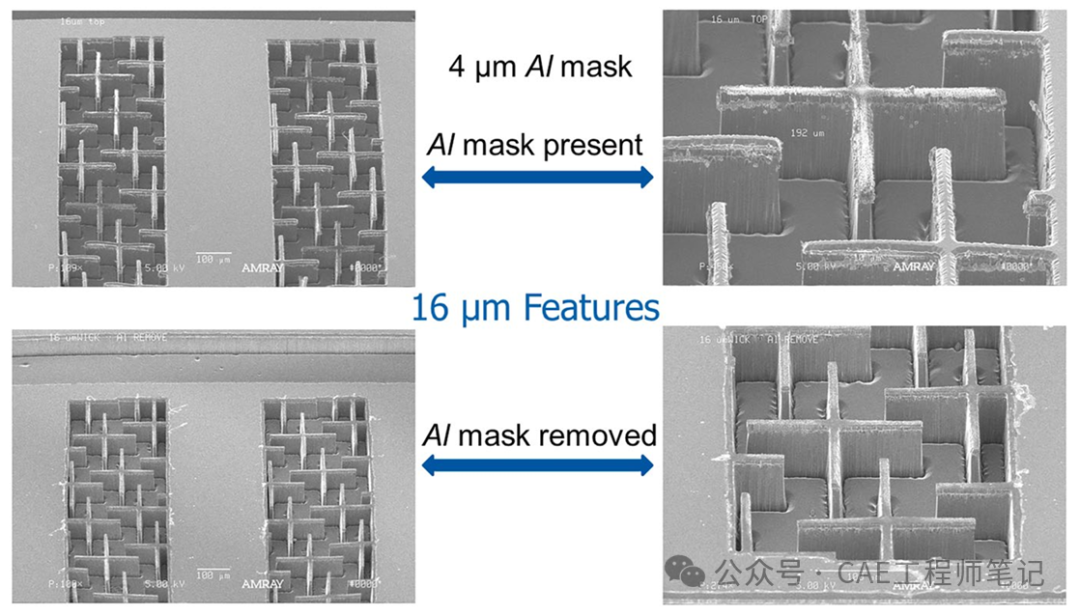

电感耦合等离子体刻蚀(ICP)可用于在SiC中创建穿衬底通孔(VIA),以及为了降低器件电阻或便于厚外延晶圆加工等目的而进行的衬底减薄。下图中的SEM展示了一次减薄衬底71μm,同时图案化出16μm宽的“十字”结构以保持机械稳定性的工艺结果。该工艺使用了4μm厚的铝金属作为掩膜。图中上部的两个SEM图像,展示了在完成71μm深的ICP刻蚀后,铝掩膜薄残留层仍然存在的情况。图中下部的两个SEM图像,则展示了移除铝掩膜后的相同区域。可以看到,16μm宽的“十字”结构被良好地解析出来,侧壁也较为垂直。在十字结构外围的沟槽底部,可以观察到一些由微掩膜效应形成的特征。这些特征可以通过进一步优化ICP刻蚀条件来消除。

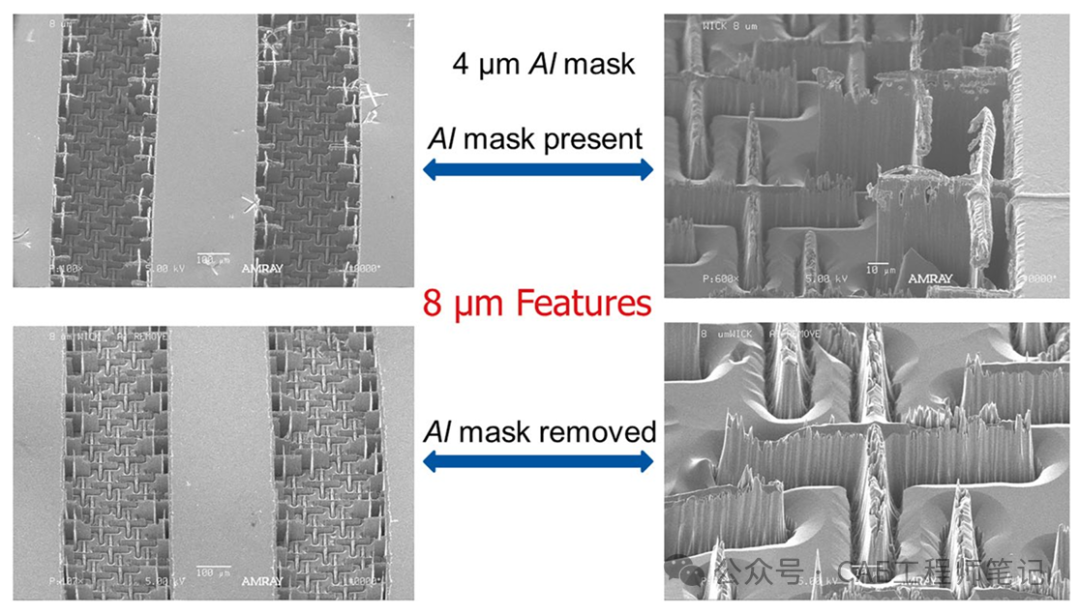

在与上图相同的工艺条件下,尝试减薄衬底71μm,同时图案化8μm宽的“十字”结构以保持机械稳定性,结果如下图的SEM所示。同样使用了4μm厚的铝金属掩膜。图中上部的两个SEM图像是完成71μm深ICP刻蚀后铝掩膜残留层存在的情况。图中下部的两个SEM图像是移除铝掩膜后的情况。可以看到,8μm宽的“十字”结构在某些区域解析不良。铝掩膜在许多区域已被ICP刻蚀“消耗掉”,十字特征及其侧壁在许多区域被部分刻蚀。这表明,优化ICP刻蚀条件对于实现良好的特征解析度、垂直的侧壁以及沟槽底部外围最小的微沟槽效应至关重要。

二、离子注入

由于常见掺杂物质(如铝、硼、氮、磷)在SiC中的扩散系数极低,且需要超过1800°C的极高温度才能实现有效扩散,传统的半导体热扩散工艺完全不适用于SiC。因此,离子注入是SiC制造中进行选择性掺杂的唯一实用方法,通过采用掩膜技术可以实现材料特定区域的掺杂。

SiC离子注入的掩膜可以通过沉积高质量的金属层,或者使用热生长氧化物与沉积氧化物的组合来实现。注入过程通常在高温(600-900°C)下进行,以最小化高能离子轰击造成的晶格损伤,这对于形成良好欧姆接触所需的高掺杂密度尤为重要。高温条件对掩膜材料的耐温性提出了严苛要求。对于较低的注入剂量(<10¹⁵ cm⁻²),室温注入是可行的;而对于欧姆接触形成所需的10¹⁹-10²⁰ cm⁻³的高掺杂密度,高温注入则是常规选择。

注入离子的深度分布可以通过蒙特卡罗模拟软件(如SRIM,即“物质中离子的阻止本领和射程”)进行预测,并通过二次离子质谱(SIMS)进行实际验证。注入后,大约1700°C的高温退火是修复晶格损伤和实现高掺杂剂电激活率(可达~95%)所必需的。对于Al、P和N等掺杂剂,注入后的深度分布在约1700°C退火后基本得以保留,这符合其低扩散常数的预期。这种缺乏扩散的特性使得在SiC中易于形成控制良好的浅结,但同时使得形成深结变得困难。

铝和硼通常被用作SiC中的受主(p型)掺杂剂,为了获得高导电性的p型材料,必须注入高浓度。注入的剂量和能量水平共同决定了p⁺区的深度和横向散射范围,进而影响器件的电容、接触电阻、夹断电压和栅极完整性等特性。这些参数值之间的权衡决定了最佳的离子注入设计。值得注意的是,硼的横向散射比铝更严重,通常不用于主流器件制造,因为其注入相关的缺陷生成率更高,并且受主的较高电离能阻碍了低电阻p型SiC的形成。

用离子轰击SiC会破坏其晶体结构。为了使材料再结晶并激活注入的原子,必须进行高温热退火。为了改善退火后的表面质量和形貌,注入后退火可以在特定的保护性气体氛围中进行。退火方式可以是炉管退火或快速热退火(RTA)。在使用炉管退火时,温度通常超过1300°C。在这些高温或高真空条件下退火,一个主要的担忧是硅(Si)从SiC表面蒸发导致的表面退化。通过在退火过程中使用覆盖晶圆表面的保护性覆盖层,可以有效地将表面退化降至最低。

常用的覆盖层材料包括石墨、SiO₂、Si₃N₄、AlN、BN/AlN复合层以及专门的碳保护退火覆盖层。其中,碳覆盖层的效果最佳。它们可以通过射频溅射或光刻胶高温石墨化的方式形成。在退火温度下,SiC与碳界面不会发生化学反应。退火完成后,可以通过灰化(O₂等离子体)或在700-800°C下进行氧化来去除碳覆盖层。

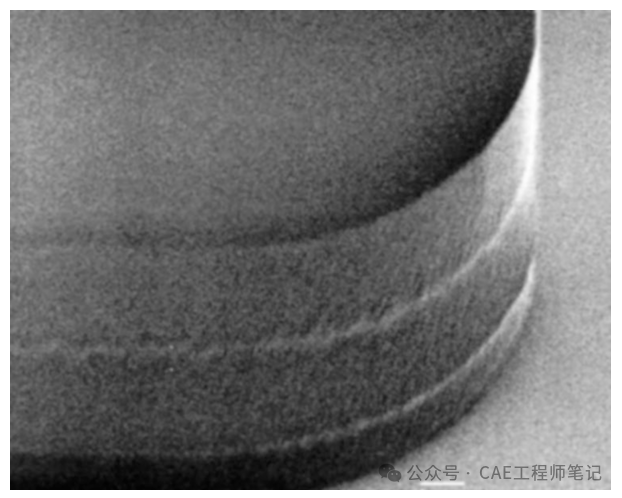

下图显示了未使用任何保护覆盖层进行离子注入后退火的SiC晶圆表面的SEM图像。可以看到,表面发生了广泛的损伤,形貌粗糙。

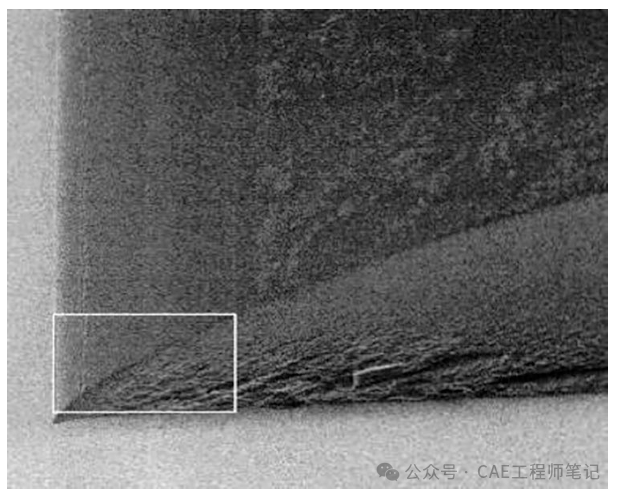

而下图则显示了在离子注入后热退火期间覆盖了石墨保护层的SiC晶圆表面的SEM图像。相比之下,表面平滑了许多。

一个生动的对比实验是:两个包含相同设计SiC JFET的晶圆,作为同一制造批次的一部分经历了完全相同的工艺步骤,唯一的区别在于退火时一个使用了石墨覆盖层,另一个没有。制造完成后,“无覆盖层”晶圆上的JFET功能成品率为零;而“有覆盖层”晶圆则获得了85%的相对较高的功能JFET成品率。

注入离子轰击的特征在上述SEM图像中SiC表面的点状纹理中依然可见。高炉温和退火完成后易于去除覆盖层,是选择合适覆盖层材料时的主要考虑因素。离子注入退火完成后,会采用热生长介质和沉积介质进行表面钝化和可靠性保护。通常会结合使用热氧化介质和经过高温致密化的沉积氧化物,并常常辅以牺牲氧化工艺。表面钝化的有效性可以通过低栅源泄漏电流和促进长期器件可靠性的、陡峭的电压击穿特性来证明。通过使用优化的热牺牲氧化钝化工艺,SiC pn结的泄漏电流可以降低好几个数量级。

然而,离子注入及随后的高温退火过程不可避免地会产生降低器件性能的缺陷。这些缺陷包括复杂的点缺陷、局域在禁带中的能级(浅能级或深能级)、扩展缺陷(如基面位错环和堆垛层错)以及新位错的产生或现有位错的移动。这些缺陷不仅会降低器件的即时性能,还可能引发长期的可靠性问题。因此,必须持续改进离子注入工艺。未来的目标是优化退火升温速率和整体注入工艺以最小化缺陷生成,并开发适用于低成本制造的高质量、室温、高剂量离子注入技术。

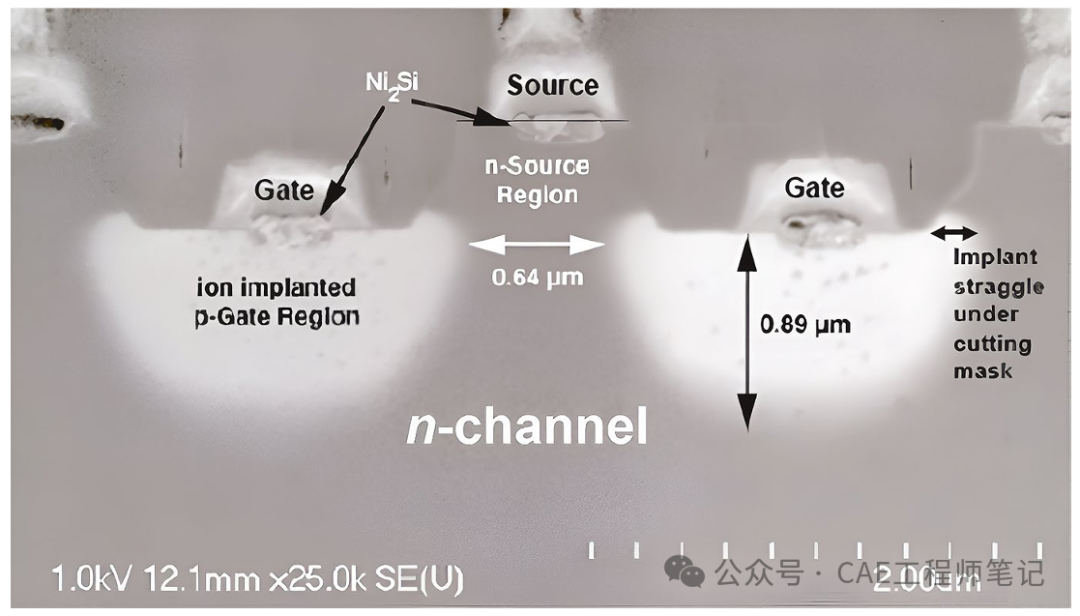

下图的SEM图像显示了一个n沟道SiC器件中,重掺杂p⁺注入栅区的横截面视图。可以清晰地看到,注入离子的横向散射会底切(Undercut)上方的掩膜边缘。

(本文详细探讨了SiC功率器件制造中的刻蚀、减薄及离子注入等核心前端工艺。在下篇中,我们将继续深入解析金属化、欧姆接触形成、栅氧界面优化等关键制造步骤,为读者呈现完整的功率半导体技术制造图谱。更多深入的半导体技术讨论,欢迎访问云栈社区进行交流。)