在功率半导体领域,垂直双扩散金属氧化物半导体场效应晶体管(VDMOS)凭借其高耐压、低导通电阻和快速开关特性,早已成为中高压功率转换的核心器件。有意思的是,与横向DMOS不同,VDMOS将源漏电流的方向从表面水平流动转变为垂直穿过硅片,这种看似简单的结构变化,却从根本上解除了耐压能力与芯片面积之间的强耦合关系。

一、垂直结构与耐压机理

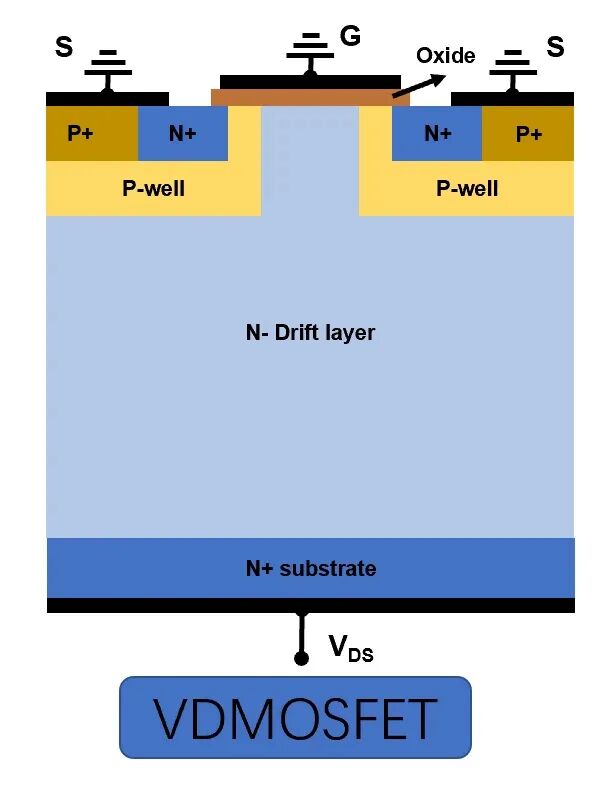

VDMOS的典型纵向结构自下而上依次为:重掺杂N+衬底(作为漏极)、轻掺杂N-外延层(漂移区)、P体区(通过注入和推阱形成)、N+源区以及位于P体区表面的栅氧化层与多晶硅栅极。当栅压超过阈值电压时,P体区表面反型形成横向沟道,电子从源极出发,先横向通过沟道,再垂直向下经过N-漂移区,最终被漏极收集。

器件的击穿电压主要由N-漂移区的厚度和掺杂浓度决定。为实现高耐压(例如600V),漂移区需要做得较厚(约30~50μm)且掺杂极低(约 $10^{14} \sim 10^{15} \, \text{cm}^{-3}$)。这种“厚而轻”的漂移区在反向偏置时能完全耗尽,均匀承受电场。然而,低掺杂的漂移区会带来较高的导通电阻,这正是硅基功率器件所面临的经典矛盾——导通电阻与耐压之间的折衷。

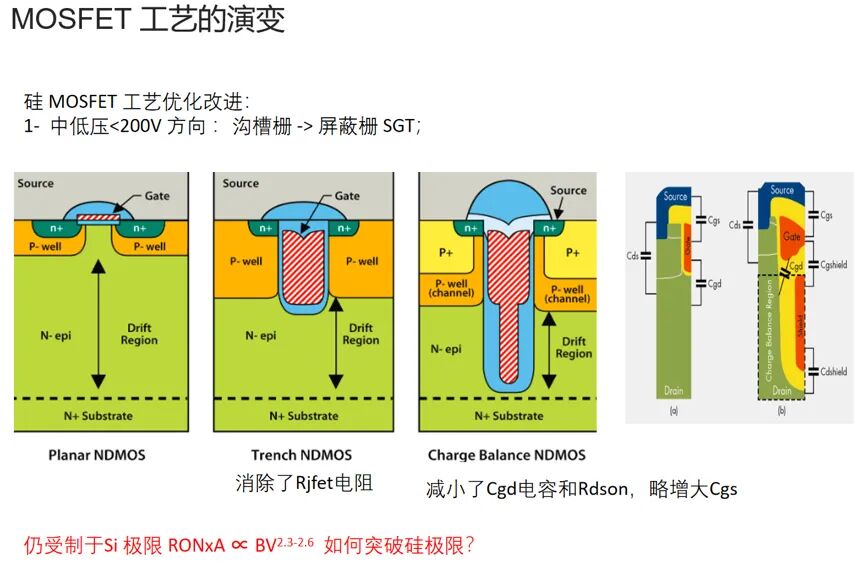

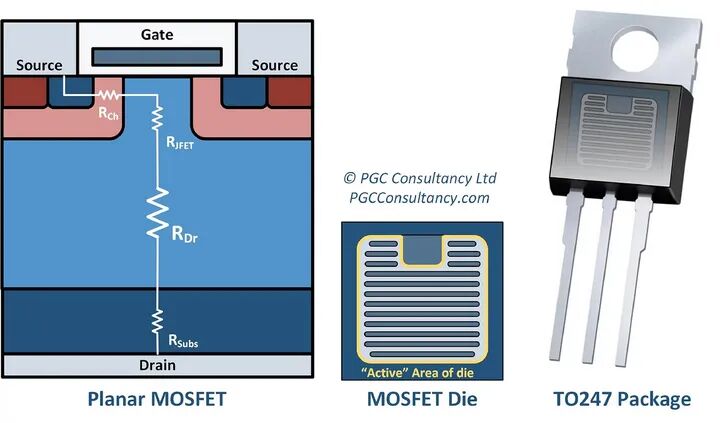

二、导通电阻的构成与沟槽技术

VDMOS的总导通电阻由几部分组成:沟道电阻、漂移区电阻、衬底电阻及接触电阻。在高压器件中,漂移区电阻占绝对主导地位。为了降低这个电阻同时不牺牲耐压,工程师们开发了沟槽VDMOS。通过深刻蚀形成垂直沟槽,将栅极埋入槽内,使沟道从横向变为纵向,消除了平面VDMOS中的JFET区电阻,并大幅提高单元密度——这意味着每个晶圆面积可以集成更多沟道。沟槽VDMOS的单元间距从平面的数微米缩小到亚微米级别,显著降低了比导通电阻。

三、超结技术:打破硅极限

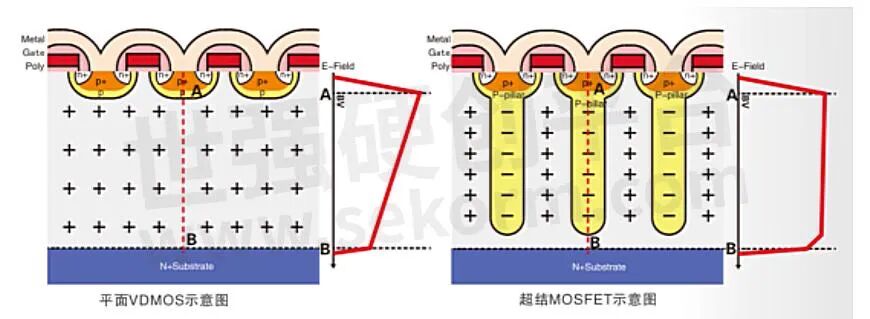

传统VDMOS的比导通电阻 $R_{on,sp}$ 正比于 $BV^{2.5}$(这被称为硅极限)。这意味着耐压每增加一倍,导通电阻将增加近6倍,简直是性能杀手。但超结(Super Junction)技术的出现颠覆了这一规律。超结VDMOS在漂移区中交替制作紧密排列的P柱和N柱,使器件在阻断状态时,P柱和N柱相互耗尽,形成近乎理想的横向电场分布。这允许漂移区掺杂浓度大幅提升(约一个数量级),从而将 $R_{on,sp}$ 与 $BV$ 的关系改善到接近线性( $R_{on,sp} \propto BV^{1.3}$ )。实现超结的关键工艺是多层外延与注入、或深沟槽刻蚀与填充,对电荷平衡精度要求极高。任何掺杂浓度的微小失配都会导致击穿电压严重下降。

四、关键工艺参数对电性的影响

VDMOS的制造涉及众多关键工艺。首先,阈值电压由栅氧化层厚度、P体区峰值掺杂浓度以及栅极材料功函数决定。为获得合适的 $V_{th}$(通常2~4V),P体区注入剂量需严格控制,退火条件直接影响杂质再分布。其次,沟道长度不是由光刻直接定义,而是靠P体区与N+源区的横向扩散差形成,典型长度约0.5~1.0μm,这对热预算的控制要求极高。再次,漂移区电阻率与击穿电压成反比,外延层厚度和掺杂浓度的均匀性直接影响整片晶圆的耐压良率。最后,沟槽刻蚀的深度、侧壁角度和底部形貌决定了积累层电阻及栅漏电容,需要精确调控刻蚀气体配比与偏压。

五、SiC等宽禁带材料的挑战

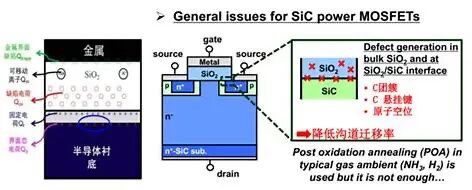

你有没有想过,硅基器件的极限在哪里?硅VDMOS在耐压超过900V后,漂移区电阻急剧上升,导致器件性能大幅下降。碳化硅(SiC)凭借10倍于硅的临界击穿电场,被广泛用于1200V以上的功率器件。SiC VDMOS可以在极薄的漂移区(约10μm)内实现1700V耐压,且导通电阻远低于硅器件,可谓降维打击。然而,SiC工艺面临诸多挑战:栅氧化层界面质量差导致沟道迁移率低(需采用高温退火或后氧化氮化来修复);P体区注入激活温度高达1600℃以上,对掩模和高温炉要求苛刻;沟槽刻蚀需要高密度等离子体设备和特殊气体化学。目前,平面栅SiC MOSFET已商业化,沟槽栅SiC MOSFET则面临沟槽拐角电场集中这一棘手问题,需要更精细的终端设计。

六、发展趋势

未来VDMOS的技术路线将分化:在600V以下消费电子领域,沟槽硅VDMOS和超结VDMOS继续优化成本与性能;在1200V以上的电动汽车、光伏逆变器领域,SiC MOSFET正在快速渗透;而在600-900V重叠区间,超结硅VDMOS与SiC MOSFET将展开激烈竞争。同时,新材料如GaN也以横向HEMT结构在650V附近与VDMOS形成互补。结构创新上,集成肖特基二极管的VDMOS(FREDFET)和采用多外延层的超结设计仍在不断涌现,力求将硅基功率器件的潜力推向极限。

可以说,VDMOS及其衍生物正与宽禁带半导体一道,服务于更高效的电能变换世界。如果你对功率半导体背后的器件物理和工艺细节感兴趣,云栈社区提供了硬核的安全与逆向分析视角,或许能帮你从另一个维度理解芯片内部结构。 |