今年二月初的 ISSCC(国际固态电路会议)上,三星电子公开了一篇关于其最新 HBM4 内存芯片的详细技术论文。表面上是常规技术发布,但深入分析后,这更像是三星对长期占据 HBM 市场主导地位的 SK 海力士发起的一次全方位反击。

作为全球最大的内存制造商,三星在过去几年的 HBM(高带宽内存)竞争中一直处于追赶者位置,自然不甘长期屈居人后。如今,HBM4 被其视为关键的翻盘机会。

HBM 是什么?为什么它对 AI 至关重要?

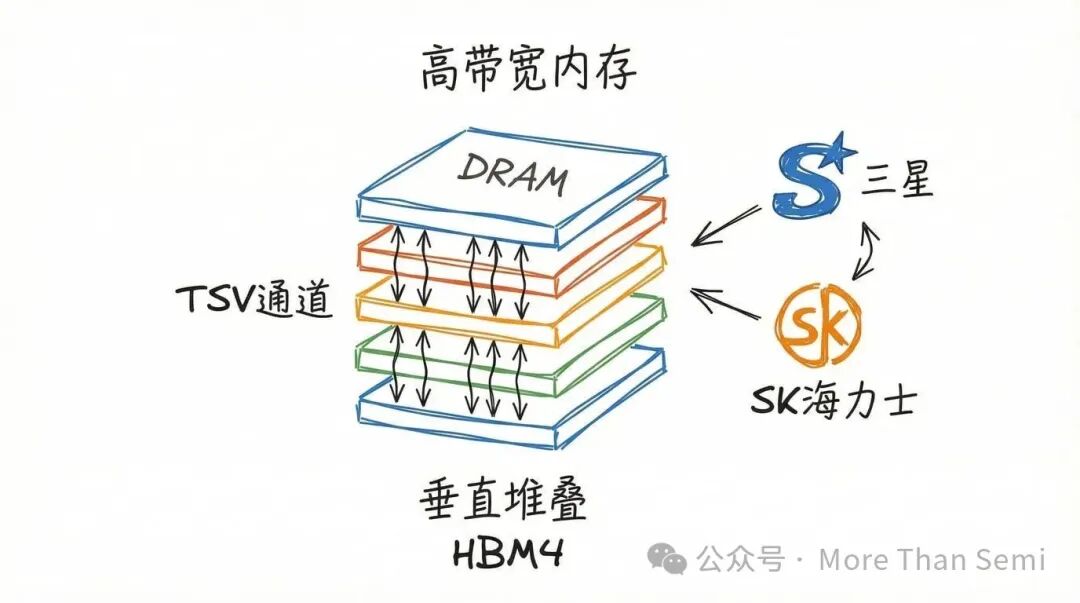

在探讨三星的具体技术突破之前,有必要先理解 HBM 的基本原理及其在当今 人工智能 浪潮中的核心地位。

传统内存可以比作“平房”,数据在平面电路板上传输。而 HBM 则是“摩天大楼”,它将多颗内存芯片垂直堆叠在一起,通过名为 TSV(贯穿硅通孔)的微型垂直通道连接。这些 TSV 就像大楼里的高速电梯,负责在各层芯片间快速运送数据。

这种设计为何如此重要?答案直接指向日益庞大的 AI 模型。垂直堆叠方式比水平扩展更高效,能在极小的物理空间内集成海量内存,并且由于离 GPU 等计算核心更近,数据传输的延迟也大幅降低。从 2018 年的 HBM2 到预计 2026 年的 HBM4,短短八年,带宽增长超 10 倍,容量增长 4.5 倍,充分印证了 AI 对内存性能近乎贪婪的需求。

规格亮眼:三星 HBM4 的核心参数

三星此次披露的 HBM4 原型规格相当激进:采用 12 层堆叠,提供 36GB 容量,具备 2048 个 I/O 引脚,总带宽高达 3.3TB/s。相较于当前的 HBM3E,带宽提升达 260%,单引脚数据速率(Data Rate)最高达到了 13Gb/s。

这里有一个值得玩味的细节:行业标准组织 JEDEC 为 HBM4 规定的官方最高速率是 8Gbps,总带宽上限为 2TB/s。三星实测的 13Gbps 大幅超出了标准 60% 以上。这清晰地表明,三星并不满足于仅仅达标,而是采取了非常激进的性能推进策略。

然而,三星面临一个严峻的现实:SK 海力士凭借其在 HBM3 和 HBM3E 上的先发优势,尤其是在英伟达等关键客户供应链中的主导地位,已经筑起了高墙。三星若想翻盘,必须拿出真正具有差异化的“硬核”技术。

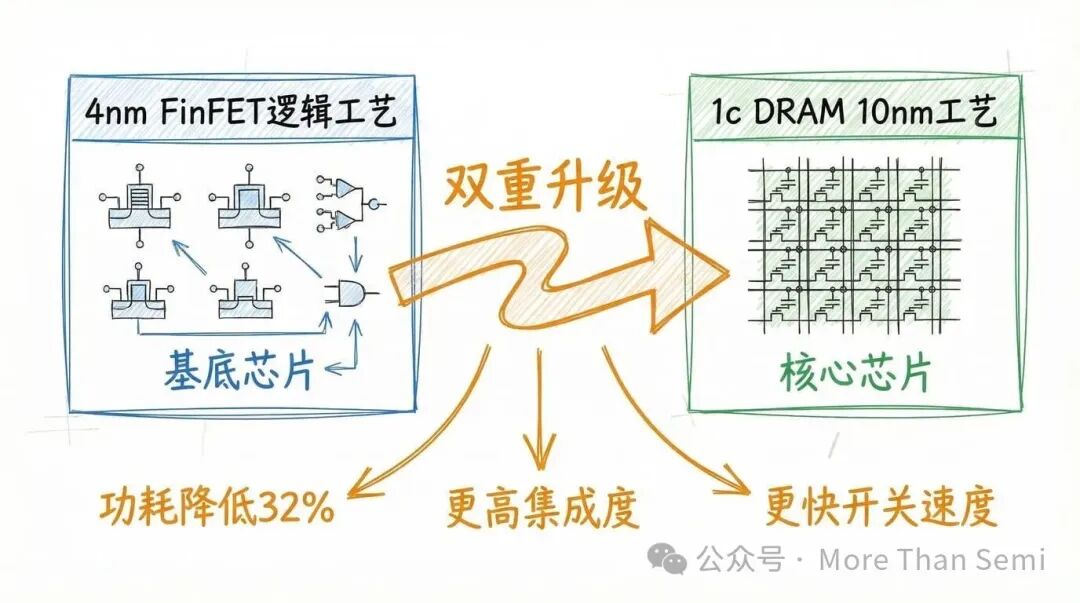

工艺双重升级:奠定性能翻倍的基石

三星 HBM4 最根本的变革,在于同时对构成内存堆栈的两种芯片进行了“世代跃进”。

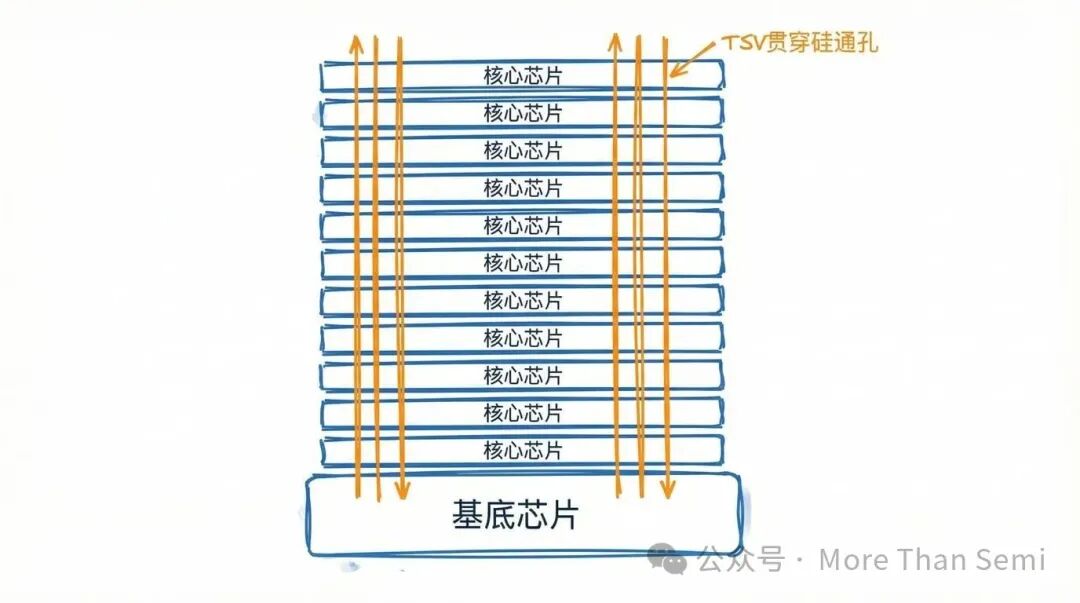

HBM 堆栈由两部分组成:上方是多层核心芯片(Core Die),负责数据存储;下方是一颗基底芯片(Base Die),负责对外接口以及与 GPU 通信。

其中,基底芯片的变革最为关键。 在 HBM3E 及之前的世代,基底芯片同样使用 DRAM 工艺制造。但 DRAM 工艺专为优化存储单元设计,并不擅长实现复杂的逻辑电路。三星此次将基底芯片的制造转移到了自家晶圆代工厂的 4nm FinFET 逻辑工艺上。

这一转变带来了多重收益:

- 晶体管尺寸显著缩小,同等面积可集成更复杂的电路。

- 晶体管开关速度更快,能实现更强大的逻辑功能。

- 工作电压从 1.1V 降至 0.75V,功耗降低约 32%。

- 为集成自动校准、高级自测试电路等复杂功能提供了可能。

核心芯片也实现了跨越式发展。 HBM3E 采用第四代 10nm DRAM 工艺,而 HBM4 直接跳过了第五代,采用了第六代 10nm(1c)工艺。这大幅缩小了存储单元的面积,在芯片尺寸不变的情况下,为其他关键结构腾出了宝贵空间。

这些释放出的空间至关重要,因为 HBM4 需要布置比前代多一倍的 TSV 通道。正是核心芯片面积缩小与基底芯片集成度提高的双重作用,才使得通道数翻倍成为可能。

从战略层面看,三星拥有自己的晶圆代工厂,4nm 逻辑工艺是自家技术。这种从 DRAM 工艺转向逻辑工艺的整合打法,是同时具备内存制造和先进逻辑工艺能力的企业才能实现的独特优势。相比之下,SK 海力士若想采用类似策略,则需依赖外部代工厂(如台积电)。虽然台积电工艺可能更先进,但在供应链整合的灵活性与可控性上,三星无疑占据了结构性优势。

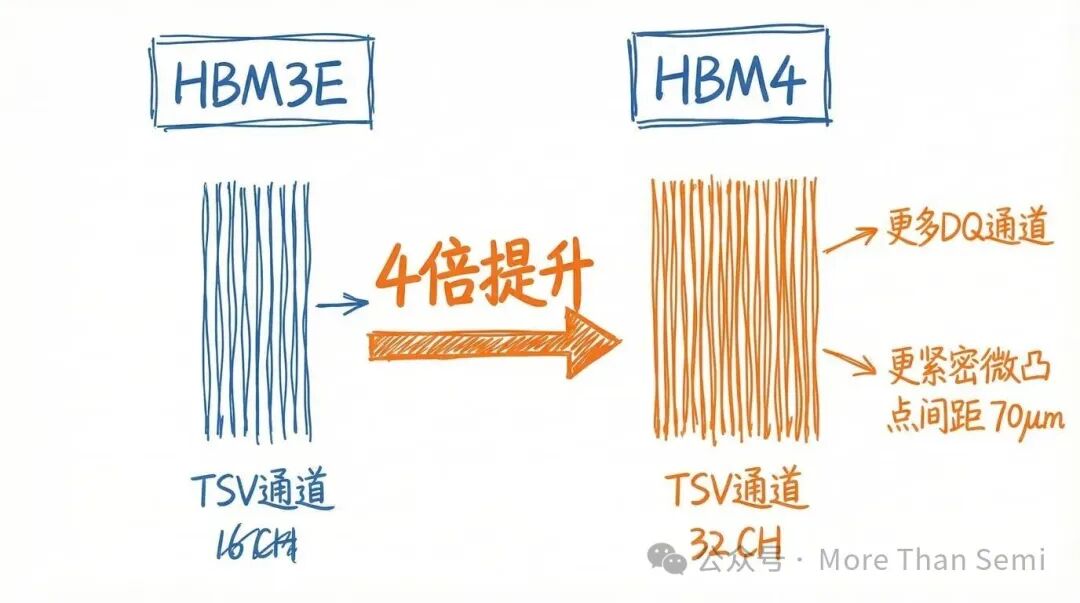

TSV 数量翻四倍:不止是简单的加法

TSV 是连接堆叠芯片的垂直数据通道。HBM4 的总 TSV 数量达到了 HBM3E 的 4 倍。这得益于两个因素:通道数从 16 个增至 32 个,同时每个通道内的 DQ(数据队列)TSV 数量也翻了一番。

DQ TSV 是实际传输数据的 I/O 引脚。更多的 DQ TSV 意味着单位时间内可并行传输更多数据,这对数据吞吐量要求极高的 AI 工作负载至关重要。

在 HBM3E 中,一个 DQ TSV 需要分时复用,依次处理两个数据信号(如 BL0 和 BL4),好比两个人轮流使用同一部电梯。而在 HBM4 中,这两个信号被分配到了独立的 DQ TSV 上,每个通道只负责一个信号。这样做的好处是为数据接收端提供了更宽的“时间窗口”(从 1 个时钟周期延长到 2 个),使数据捕获更加稳定可靠,从而为实现更高的传输速率铺平了道路。

实现这一点面临物理层面的挑战。连接芯片的微凸点(Microbump)间距从 HBM3E 的 96μm 缩小至 HBM4 的 70μm,缩减了 27%。更紧密的凸点间距是在有限面积内容纳更多 TSV 的先决条件。

此外,三星在 12 层堆叠的核心芯片上应用了 ABB(自适应体偏压)技术。由于制造过程中的细微差异,不同芯片的运行速度会有偏差。ABB 技术通过动态调整每颗芯片晶体管的体偏压,将运行较慢的芯片适当“加速”,将运行过快的芯片适当“减速”,从而使整个堆栈的性能表现更加均匀一致。

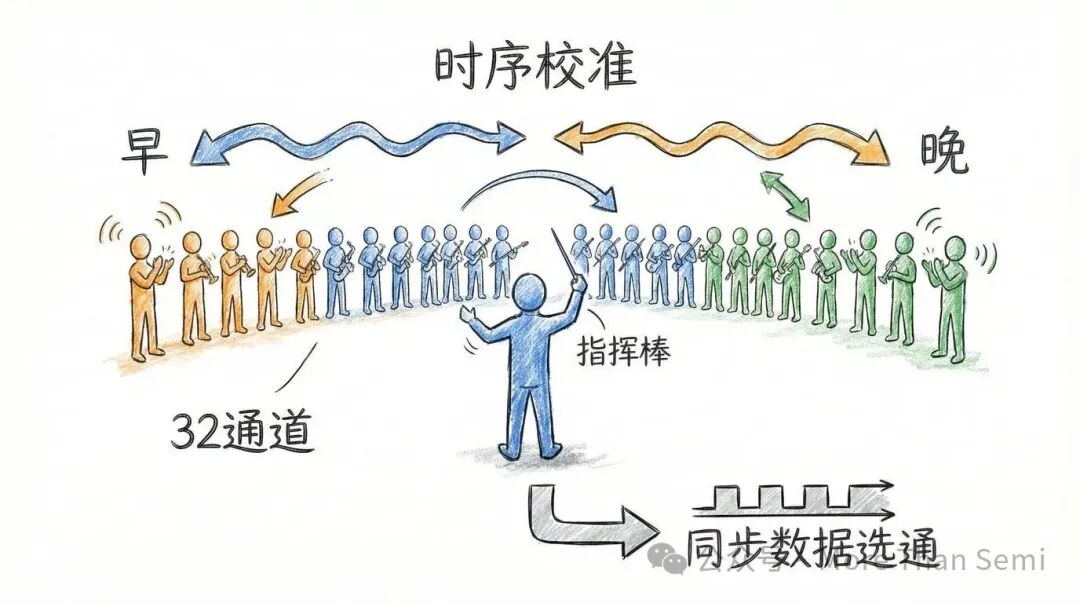

时序校准:确保32通道同步工作的“指挥家”

HBM4 拥有 32 个独立通道,数据信号需要穿过最多 12 层芯片才能到达基底芯片。不同通道之间不可避免地存在时序差异:有的信号到的早,有的到的晚。造成差异的原因包括 TSV 路径长度不一、制造公差,以及工作时的温度、电压波动。

若不解决此问题,GPU 在接收数据时就会遇到麻烦——部分通道的数据已就绪,另一部分却还在路上,导致数据错位。传输速率越高,这一问题就越凸显。

三星的解决方案是“每通道 TSV RDQS 时序自动校准技术”。RDQS(读数据选通)是内存向 GPU 发送数据时提供的时序参考信号,相当于告诉 GPU “数据包裹已送达,请开门查收”的门铃。

校准过程分为三个阶段:

- 初始化:系统上电后,每颗核心芯片发出就绪信号,触发校准流程。

- 测量:通过一个复制真实信号路径的电路(称为 Replica Tree),精确测量各通道的实际时序差异。系统以最慢的通道为基准。

- 对齐:利用 TDC(时间数字转换器)将每个通道的时序偏移量转换为数字编码。随后,通过数字可控延迟线,为到达快的通道增加适当延迟,为到达慢的通道减少延迟,最终让所有通道的 RDQS 信号同步到达。

三星用一个生动的比喻解释了该技术:想象有 32 个人要在同一拍上鼓掌,但每人反应时间不同。若不校准,指挥只能迁就最慢的人,放慢整体节奏。校准后,指挥先测量每个人的反应时间,然后告诉反应快的人“稍等片刻再拍”,这样所有人就能在同一瞬间整齐拍手,整体节奏得以大幅加快。

实测数据显示,经过该校准,在 tCCDR(不同芯片层间切换的最小延迟)为 2nCK 时,最大可实现速率从 7.8Gb/s 提升至 9.4Gb/s,提升约 20%。这不是纸面参数,而是 AI 系统在实际运行中能真切感受到的性能改善。

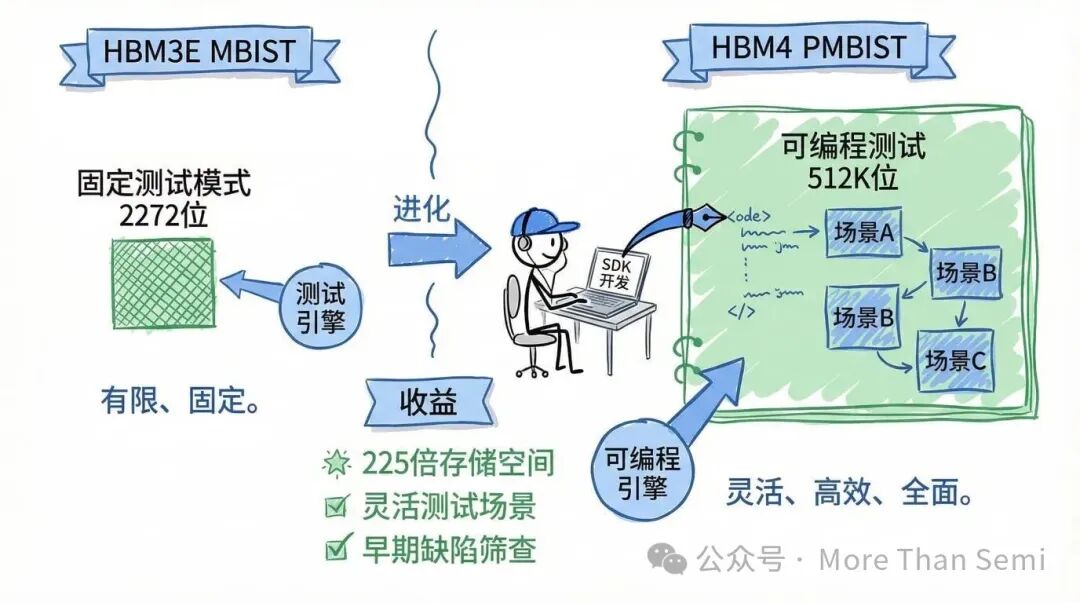

测试革命:将缺陷扼杀在摇篮里

HBM 结构复杂,拥有数千个 TSV 和数十个通道,测试难度极大。若等到与 GPU 完成高级封装后再发现缺陷,损失将极其惨重。

传统测试采用 MBIST(内存内建自测),但 HBM3E 的 MBIST 受限于 DRAM 工艺的面积,只能使用固定、有限的测试模式。这好比一场只有固定五道题的考试,如果缺陷恰好不在这五题的考察范围内,就会被漏检。

HBM4 引入了 PMBIST(可编程 MBIST)。得益于 4nm 逻辑工艺提供的充裕面积,测试程序的存储空间比之前大了 225 倍。固定的“五道选择题”变成了可自由编程的“海量题库”。测试工程师可以使用 SDK 像编写软件一样设计复杂的测试场景,并能将现场发现的新缺陷模式快速纳入未来的测试方案中。

测试顺序的灵活性也是一大创新。AI 工作负载的特点是 GPU 需要在不同内存芯片层间快速切换,这种切换速度(tCCDR)直接影响实际性能。HBM3E 的固定测试顺序无法有效测试这种快速切换场景。而 HBM4 的可编程测试序列可以模拟真实的 AI 工作负载模式进行针对性测试。

另一项创新是 WDQS(写数据选通)偏斜的晶圆级校正。HBM4 采用四相 WDQS 方案,四个相位必须精确均匀分布,即便几皮秒的偏差也会引发问题。传统方法只能在封装完成后检测,为时已晚。三星采用片上自环方法,在晶圆测试阶段就能测量并校正偏斜,将有问题的芯片在封装前就筛选剔除。

实测表明,应用晶圆级校正后,确定性抖动从 10.6 皮秒降至 4.5 皮秒,降幅超一半。这意味着更清晰稳定的数据信号,为高速稳定运行奠定了基础。

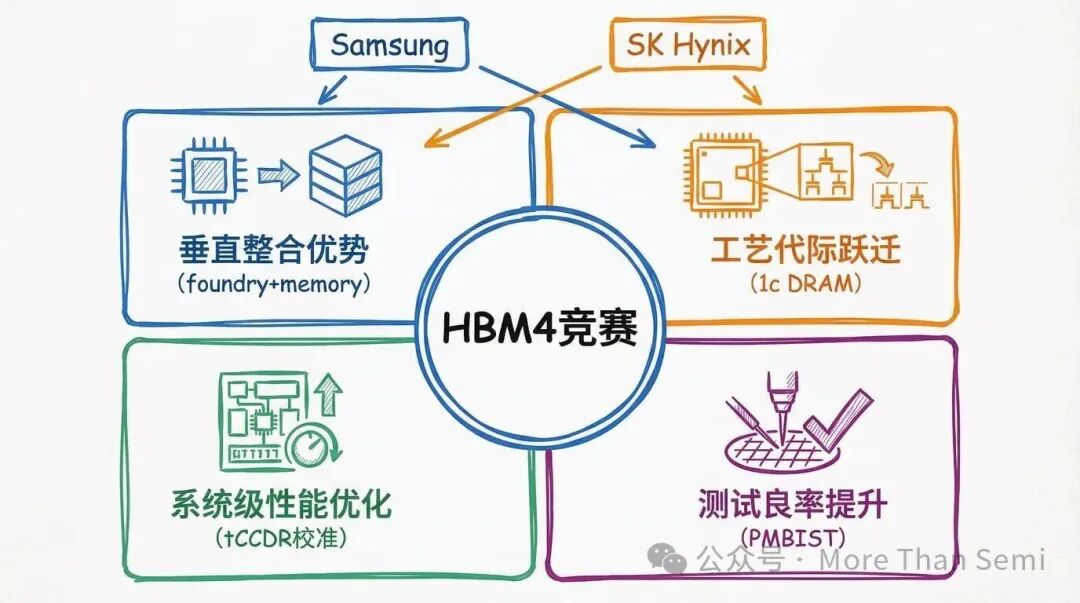

技术突围之后,三星的胜算几何?

从纯技术角度审视,三星 HBM4 确实展现出了强大的竞争力:

- 垂直整合优势首次充分兑现:HBM4 是三星真正利用其“内存+代工”双重身份的开端。4nm 基底芯片、PMBIST、高级自动校准等功能,均深度受益于这种内部协同能力。

- 工艺跳跃激进果断:核心芯片跳过第五代直接进入第六代 10nm 工艺,为 TSV 数量翻倍创造了物理空间。没有这一步,仅靠基底芯片升级无法达成目标规格。

- 测试与良率管理理念革新:PMBIST、晶圆级校正、tCCDR 自动校准三者形成正向循环,旨在实现更早的缺陷检测、更高的生产良率、更优的系统级性能。这是三星试图扭转 SK 海力士在 HBM3E 良率上建立优势的关键。

- 聚焦真实系统性能:tCCDR 自动校准提升的不是规格表上的峰值带宽,而是 GPU 在实际复杂负载下体验到的有效带宽。在优化层间切换的同时冲击 13Gbps 高速率,直接瞄准了英伟达等客户的痛点需求。

当然,现在就断言三星已经获胜为时尚早。三星代工厂的 4nm 工艺实际良率如何?全新的 1c DRAM 工艺在量产中是否稳定?论文中的性能数据能否在千万量级的产品中完美复现?这些问题都需要时间与市场来检验。

另一方面,SK 海力士必定不会坐以待毙。其很可能通过与台积电的紧密合作,推进自己的逻辑工艺基底芯片方案。这场围绕 智能 & 数据 & 云 时代核心资源的竞赛,最终格局仍存变数。

但有一点可以肯定:三星此次并非简单追赶,而是试图通过一套组合拳般的差异化策略重新划定赛道。HBM 竞赛的第二回合,哨声已经吹响。

写在最后

HBM4 的竞争,本质上是顶级半导体巨头在技术纵深与产业链整合能力上的全面较量。三星此番展现出的技术野心与执行路径,从底层工艺革新到系统级优化,从测试方法论突破到性能极限挑战,每一步都经过了周密计算。

对于关注半导体行业与 计算机基础 硬件演进的投资人与技术爱好者而言,HBM 市场的格局演变值得持续关注。倘若三星真能凭借 HBM4 实现弯道超车,不仅将重塑内存市场的竞争版图,更会对整个 AI 芯片的供应链生态产生深远影响。

毕竟,在这个由算力定义一切的时代,内存早已不是默默无闻的配角,而是制约系统性能的关键瓶颈之一。谁能更高效地突破这个瓶颈,谁就将在下一阶段的竞争中掌握更多主动权。

本文技术内容参考自:https://x.com/damnang2/status/2028006170779140227