探讨了一种用于电源电压检测的ADC采样电路,指出MOS管的选择不当可能导致上电过冲问题,影响ADC读数准确性甚至损坏控制器。分析了上电过冲产生的原因——MOS管的结电容,并提出了减少结电容的选择方案以解决此问题。

- 一、上电过冲问题

- 二、上电过冲产生原因

- 三、解决方案

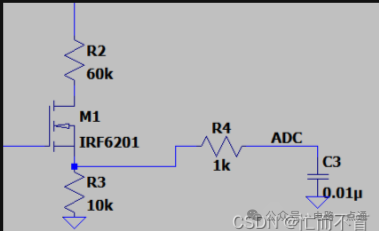

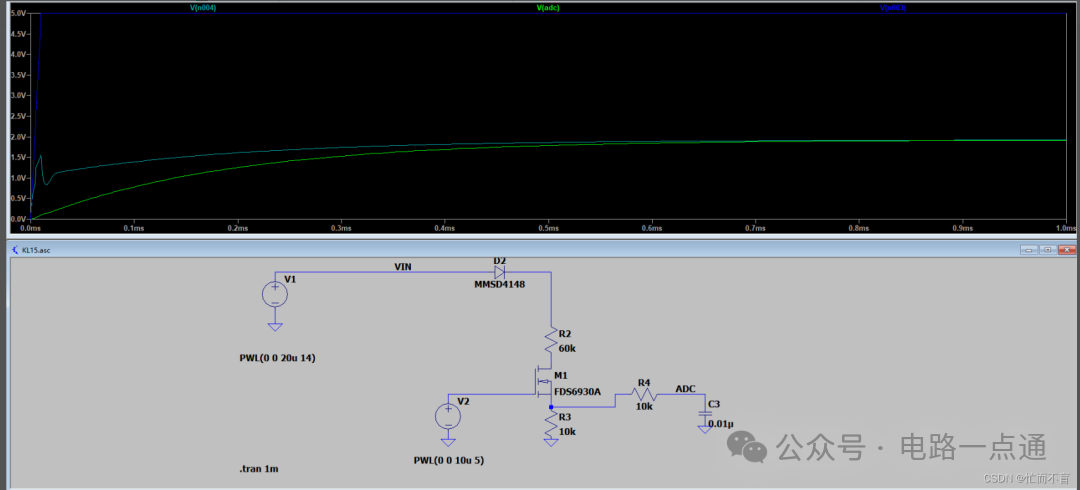

下图展示了一种在某些场景下(如电源电压监控)常用的ADC采样电路。这个电路用于精确检测电源电压值。你是否想过,图中的MOS管 M2 是否可以随意选择?本文将通过仿真计算来揭示,如果选择不当,会引发什么具体问题。

一、上电过冲问题

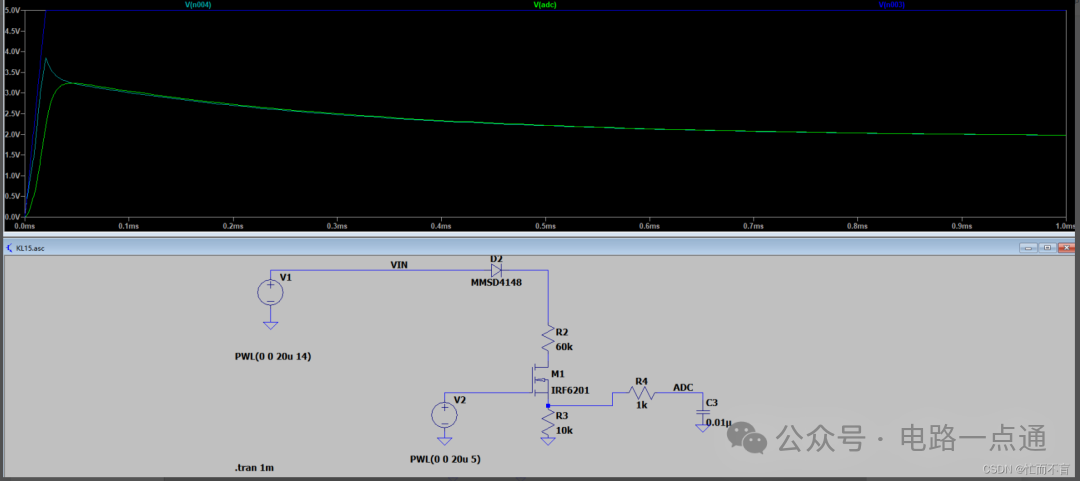

我们首先随意选择一个型号的MOS管进行仿真,例如 IRF6201(确保栅极驱动电压 V2 能使其饱和导通)。在下面的仿真图中,深蓝色曲线代表栅极驱动电压 V2,浅蓝色曲线是电阻 R4 左端的电压,绿色曲线则是 ADC 采样网络上的实际电压。

上图中,输入电源 V1 的电压为 14V。根据理想分压公式计算,ADC 采样点的电压应为 14V * R3 / (R3 + R2) = 2V。然而,从仿真波形可以清晰地看到,上电过程中 ADC 引脚上的电压最高上冲到了 3V 以上,经过接近 1ms 的时间后才逐渐稳定到 2V 左右。更值得注意的是,R4 左端的电压上冲幅度更大,接近 4V。

这个仿真结果揭示了两个潜在的风险:

- 电压过冲可能超过微控制器 ADC 引脚的绝对最大额定电压,导致引脚永久性损坏。

- 如果系统在上电后 1ms 内就进行 ADC 采样并做出判断,采集到的电压值将是错误的,可能导致系统逻辑误动作。

二、上电过冲产生原因

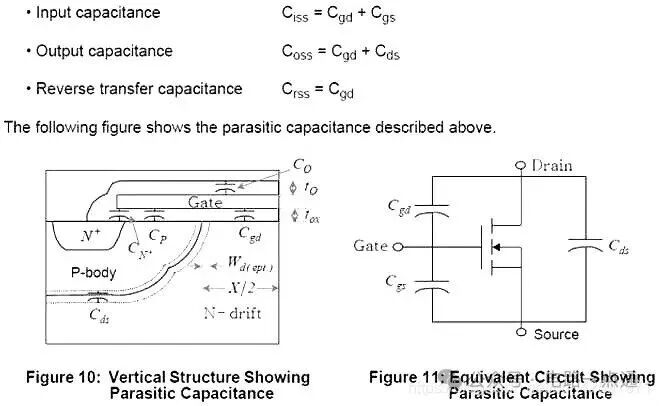

问题的根源在于MOS管并非理想开关。我们知道,MOS管的栅极(G)和源极(S)之间存在着固有的寄生结电容,其等效模型如下图所示:

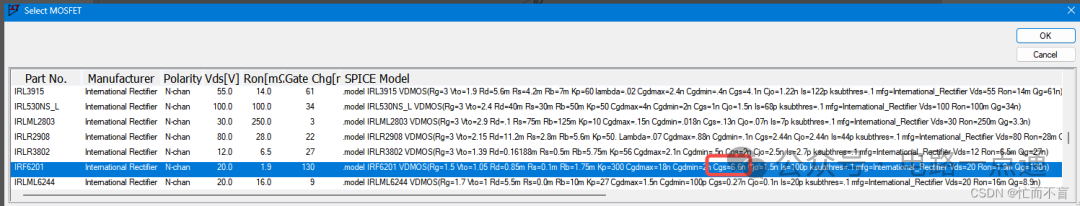

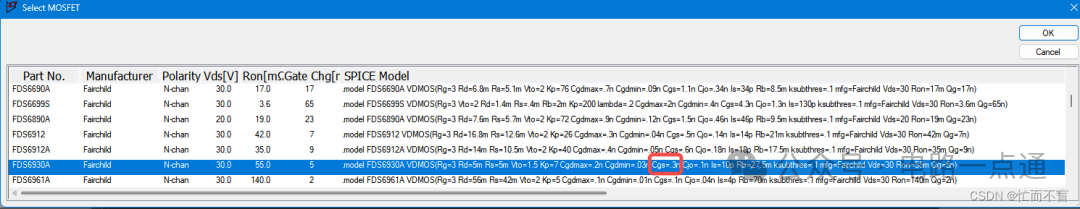

根据器件资料,我们可以查到具体的结电容数值。在 LTspice 等仿真软件的器件模型中,这些参数是直接给出的。例如,下图显示了我们最初选用的 IRF6201,其栅源电容(Cgs)约为 6.6 nF。

电容两端的电压不能突变,这是理解该现象的核心。在上电瞬间,由于 Cgs 的存在,源极(S)的电压会被“耦合”抬升,趋向于栅极(G)的电压。直到流经电阻 R3 的电流将 Cgs 充满电,源极电压才会遵循分压原理下降至稳态值。这个充电过程的时间常数大致为 τ = R3 * Cgs = 66 µs。如果栅极电压上升沿更陡,或者 MOS 管的结电容更大,源极电压的最大上冲值甚至可以接近栅极驱动电压(本例中为 5V)。

三、解决方案

既然找到了问题的根源——栅源结电容 Cgs 与分压电阻构成的 RC 延迟网络,我们就可以有针对性地提出解决方案。

-

减小串联电阻 R3:这能缩短 RC 时间常数,从而减缓上冲。但为了维持相同的分压比,R2 也必须同比例减小,这会直接导致从电源 V1 到地的静态漏电流增大,增加不必要的功耗,在电池供电等场景下不可取。

-

减小 Cgs,选择结电容更小的 MOS 管:这是更优的解决方案。例如,我们换用型号为 FDS6930A 的 MOS 管,其栅源电容仅为 0.3 nF,远小于 IRF6201。

使用 FDS6930A 进行替换后的仿真结果如下。可以明显看到,源极电压(浅蓝色曲线)的上冲被极大地抑制,未超过 2V。ADC 采样点电压(绿色曲线)的过冲也完全消失,仅在上升沿有一个微小的尖峰(这是 Cgs 充电完成前产生的),随后迅速稳定在 2V。这个结果完美解决了上电过冲的问题。

总结

本文深入分析了在电阻分压式 ADC 采样电路设计中,一个常被忽视的细节:MOS管作为开关时的栅源结电容效应。不当的选型会导致严重的上电电压过冲,其危害是双重的——既可能损坏ADC引脚硬件,也可能因采样值不准确引发软件逻辑错误。

解决之道在于优先选择栅源结电容(Cgs)小的 MOS 管型号,这比盲目调整电阻值更为有效和根本。在硬件设计,特别是涉及精密模拟电子技术电路采样和上电时序控制的场景中,此类寄生参数的影响必须纳入考量。希望这个案例能为大家在未来的电路设计与调试中提供有价值的参考。如果你有类似的设计经验或疑问,欢迎在云栈社区与更多硬件开发者一起交流探讨。 |