在车载、工控、智能硬件等涉及CAN总线的设计中,无论是TJA1042、TCAN1044还是SIT1051,CAN收发器都是核心器件。细心的你一定会注意到,这些芯片上总有一个标注为“VIO”的引脚。

很多刚入行的硬件工程师常会习惯性地给VIO引脚串一个1kΩ电阻上拉到电源,觉得“上拉一下更稳定”。但结果往往是:上电后CAN总线完全不通,RXD信号乱跳,芯片莫名发热,排查半天都找不到问题根源。

这篇文章就一次性讲透:VIO引脚到底有什么用?为什么上拉1kΩ到电源是个致命错误?新手看了能避坑,老工程师也能查漏补缺,避免不必要的PCB返工。

一、VIO引脚,并非“普通IO口”

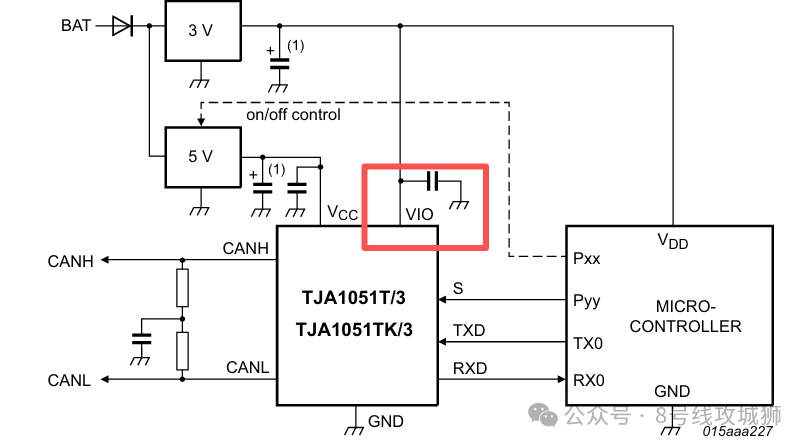

现在主流的CAN收发器几乎都采用双电源架构——一个是VCC,一个是VIO。两者分工明确,缺一不可:

- VCC:给CAN总线驱动电路供电(通常是5V),负责驱动CANH、CANL引脚的差分信号,是总线通信的“动力源”。

- VIO:数字IO电平基准兼内部数字电路供电脚。它为CAN收发器与MCU之间的通信提供电平基准。

二、VIO引脚的四个核心作用

VIO引脚远比你想象的要复杂,它主要承担了以下四个关键任务:

- 与外部MCU电平匹配:现在大部分MCU是3.3V内核,而CAN总线驱动需要5V。VIO就是用来“对齐”这两种电平的。VIO接3.3V,TXD、RXD等数字引脚就输出3.3V电平,直接匹配3.3V MCU;VIO接5V,就兼容老款5V MCU。这样就从硬件层面杜绝了电平不识别、通信丢包的问题。

- 给内部电平转换电路供电:CAN收发器内部存在两个电压域(VCC的5V域和VIO的1.8V/3.3V/5V域)。VIO负责给内部的电平转换模块供电,让两个电压域的信号能够正常“翻译”和互传。

- 欠压保护机制:芯片内部会实时监测VIO电压。一旦VIO低于阈值(通常为2.7~3V),就会自动进入保护模式——CANH、CANL呈高阻态,RXD固定为高电平,从而避免乱码干扰整个CAN总线网络。

- 支持低功耗与休眠场景:在车载、电池供电设备中,可以对VIO进行受控供电,在维持芯片唤醒检测功能的同时,显著降低整机功耗,满足严苛的低功耗设计需求。

三、典型误区案例分析:VIO上拉1kΩ导致CAN通讯失败

很多工程师习惯给STB、TXD等控制脚做上拉处理,就想当然地把这个习惯套用到了VIO上,直接串一个1kΩ电阻接到5V或3.3V电源。

这种接法是完全错误的,会引发一系列硬件故障,甚至损坏芯片。具体可以分为以下五点:

1. VIO电压被拉偏,电平彻底不匹配

VIO作为电源输入脚,工作时会有1~5mA的静态电流。根据欧姆定律,串入1kΩ电阻后,VIO的实际电压会被拉低:VIO = 电源电压 - 静态电流 × 1kΩ。

举个例子:在5V系统中,若静态电流为3mA,那么VIO ≈ 5V - 3mA × 1kΩ = 2V。这个电压远低于3.3V/5V的正常工作范围,将直接导致MCU与收发器之间的信号电平异常,CAN总线收发乱码、丢包,甚至完全不通。

2. 触发欠压保护,CAN直接“罢工”

大部分CAN收发器的VIO欠压阈值在2.7~3.0V(针对3.3V系统)或4.2~4.5V(针对5V系统)。上拉1kΩ后,VIO电压很容易跌落到这个阈值以下,芯片会立刻进入保护模式,导致总线通信中断。

3. 额外功耗飙升,电池设备“扛不住”

1kΩ上拉电阻会持续流过电流,产生额外的无用功耗:P = (电源电压 - VIO)² / 1kΩ。在5V系统中,这部分额外功耗可能达到10~20mW。对于车载终端或电池供电的便携设备,这直接导致待机时间缩短、功耗超标,甚至可能触发系统的低功耗保护机制。

4. 电源噪声增大,EMC性能变差

上拉电阻会削弱电源抑制比。外界的干扰信号更容易通过这个电阻耦合进VIO引脚,进而影响内部数字电路的稳定性。后果就是芯片抗干扰能力下降,更容易受到电机、继电器等强干扰源的冲击,导致EMC测试难以通过,增加产品整改成本和时间。

四、总结

说到底,VIO是CAN收发器的“数字电平电源脚”,其核心作用就是匹配MCU电平并为内部数字电路供电。绝对不能串接1kΩ电阻上拉到电源,否则必然导致电压拉偏、触发欠压保护,最终CAN通信失败。标准的接法其实很简单:直接连接到目标电压电源,并在引脚附近放置一个0.1μF的去耦电容。

CAN电路看似简单,但一个引脚的错误接法,就可能让整块板子调试半天、反复返工。希望这篇文章能帮你避开这个经典的硬件大坑,下次画PCB时一次成功。大家在设计CAN电路时,还踩过哪些意想不到的坑?欢迎在评论区分享交流。 |