在嵌入式系统里,SDIO接口或许不如USB或SPI那样广为人知,但它却是一个“低调的实力派”。手机中的Wi-Fi模组、SD存储卡、GPS芯片等,很多都依赖SDIO与主控芯片通信。

本篇将深入解析SDIO的硬件工作原理,涵盖以下几个核心问题:

- SDIO是什么?能接哪些设备?

- SD家族(SD/SDHC/SDXC/SDIO)如何区分?

- 引脚定义与功能详解。

- 1-bit与4-bit模式有何区别?速度差异多大?

- 命令如何发送,数据如何传输?

- 上电后如何完成初始化?

- 硬件设计中有哪些关键点与常见陷阱?

一、SDIO是什么?能接哪些设备?

SDIO,全称Secure Digital Input Output,可译为“安全数字输入输出”。它是在SD卡标准基础上扩展出的接口协议,不仅支持存储卡,还能连接各种外设模块。

一句话概括:SDIO是SD卡接口的“超级进化版”,功能从单纯存储扩展到了连接外设。

你可能并未意识到,以下这些嵌入式设备中,很多都采用了SDIO接口:

| 设备类型 |

常见芯片/模组 |

用途说明 |

| Wi-Fi 模组 |

RTL8189, AP6212, ESP8089 |

无线网络连接,最常见的SDIO应用 |

| 蓝牙模组 |

AP6255, BCM4345 |

蓝牙通信,常与Wi-Fi集成在同一模组 |

| SD存储卡 |

SD/SDHC/SDXC 卡 |

最原始的应用,文件系统存储 |

| GPS模块 |

部分u-blox系列 |

位置定位数据传输 |

| NFC模块 |

部分NXP系列 |

近场通信 |

| 相机模块 |

EyeFi等WiFi SD卡 |

无线图像传输 |

注意:并非所有Wi-Fi/蓝牙模组都使用SDIO,部分会采用USB或UART接口。选型时务必确认接口类型。

二、SD家族区分:SD / SDHC / SDXC / SDIO

SD卡标准版本繁多,通过下表可以快速理清:

| 名称 |

全称 |

最大容量 |

文件系统 |

最高速率 |

| SD |

Secure Digital |

2 GB |

FAT12/16 |

25 MB/s |

| SDHC |

Secure Digital High Capacity |

32 GB |

FAT32 |

104 MB/s |

| SDXC |

Secure Digital eXtended Capacity |

2 TB |

exFAT |

312 MB/s |

| SDIO |

Secure Digital Input Output |

—(非存储) |

—(非存储) |

视设备而定 |

关键点:SDIO本身并非存储卡规范,而是外设扩展接口规范。它复用了SD的物理接口,但用途完全不同。

此外,SD卡还有速度等级(Speed Class)的概念,这直接影响其能否流畅录制4K视频或满足嵌入式应用需求:

| 速度等级 |

标识 |

最低写入速率 |

典型应用场景 |

| Class 2 |

C2 |

2 MB/s |

普通拍照 |

| Class 4 |

C4 |

4 MB/s |

标清视频录制 |

| Class 10 |

C10 |

10 MB/s |

全高清视频、一般嵌入式应用 |

| UHS-I U1 |

U1 |

10 MB/s |

4K视频入门 |

| UHS-I U3 |

U3 |

30 MB/s |

4K视频、连拍 |

| V90 |

V90 |

90 MB/s |

8K视频专业级 |

选型建议:对于嵌入式项目,选择Class 10 / UHS-I U1及以上等级的SD卡通常足够,稳定性往往比极限速度更重要。

三、引脚全解析

标准全尺寸SD卡共有9个引脚,SDIO接口同样使用这些信号线:

| 引脚名 |

引脚编号 |

方向 |

功能说明 |

| VDD |

Pin 4 |

电源 |

供电,通常3.3V(部分设备支持1.8V) |

| VSS |

Pin 3/6 |

地 |

信号地 |

| CLK |

Pin 5 |

主→从 |

时钟信号,由Host提供,所有数据传输同步于此 |

| CMD |

Pin 2 |

双向 |

命令通道:主机发命令、卡回响应 |

| DAT0 |

Pin 7 |

双向 |

数据线0,1-bit模式唯一数据线;4-bit模式数据位0 |

| DAT1 |

Pin 8 |

双向 |

数据线1(4-bit模式使用);SDIO中断线(1-bit模式) |

| DAT2 |

Pin 9 |

双向 |

数据线2(4-bit模式使用) |

| DAT3 |

Pin 1 |

双向 |

数据线3(4-bit模式);卡检测(Card Detect) |

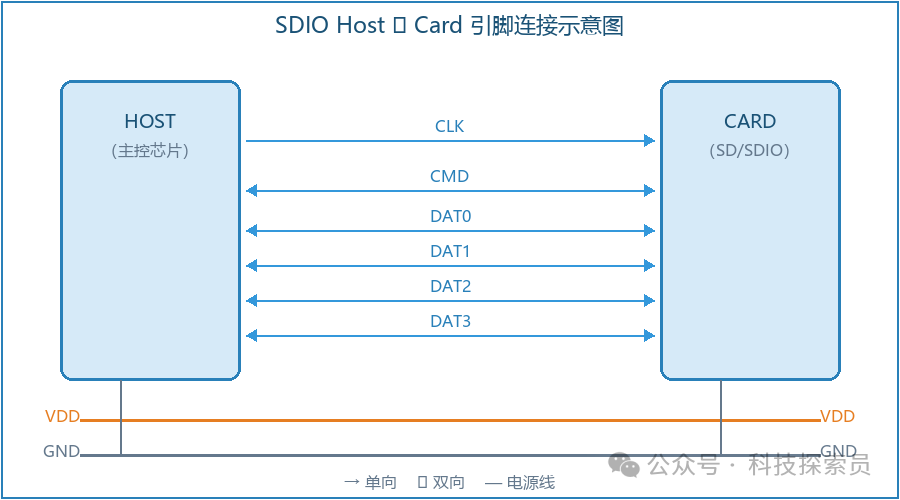

通过下图可以直观理解Host(主控)与Card(SD/SDIO设备)之间的连接关系:

核心特征:CLK始终由Host主动产生,Card永远不会自己产生时钟,这是主从架构的核心。

注意:DAT1在SDIO模式下兼作中断线(SDIO IRQ)。当设备有数据需要上报时,会通过DAT1拉低电平来通知主机。

四、1-bit vs 4-bit 模式

SDIO支持两种总线宽度模式,区别在于使用的数据线条数:

| 模式 |

使用数据线 |

典型时钟频率 |

理论峰值速率 |

适用场景 |

| 1-bit 模式 |

DAT0 × 1 |

25 MHz |

~3.1 MB/s |

资源受限、简单外设、调试阶段 |

| 4-bit 模式 |

DAT0~DAT3 × 4 |

50 MHz |

~25 MB/s |

Wi-Fi模组、高速SD卡、正式产品 |

| 4-bit SDR104 |

DAT0~DAT3 × 4 |

208 MHz |

~104 MB/s |

UHS-I高速应用 |

4-bit模式相比1-bit,速率提升显著(约4条数据线 × 时钟频率翻倍 ≈ 8倍),是绝大多数嵌入式产品的首选。

关键步骤:初始化阶段必须使用1-bit模式。待卡识别完成、进入数据传输状态后,再通过协商切换到4-bit模式。

硬件限制:如果PCB设计时只连接了DAT0,那么只能运行在1-bit模式下。硬件设计之初就需要规划好。

五、命令帧格式与响应类型

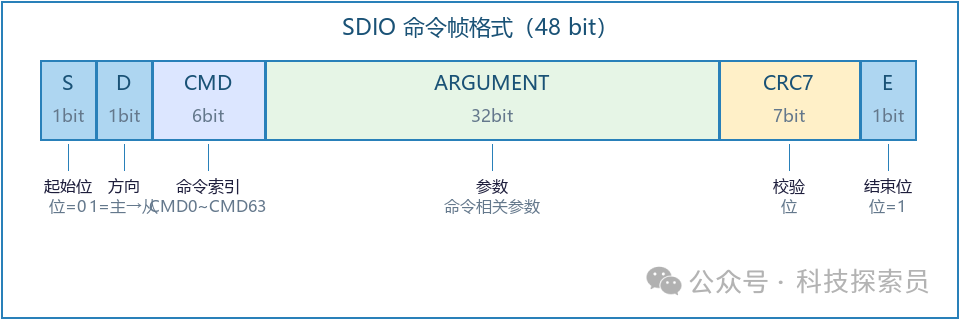

SDIO的“对话”依靠命令帧完成。每个命令帧格式固定,长度为48 bit,具体结构如下:

主机发送命令后,卡会返回一个“响应”。不同命令对应不同的响应类型:

| 响应类型 |

长度 |

典型用途 |

包含内容 |

| R1 |

48 bit |

大多数命令的标准响应 |

卡状态寄存器 |

| R2 |

136 bit |

CMD2(读CID)、CMD9(读CSD) |

128bit完整寄存器内容 |

| R3 |

48 bit |

ACMD41(OCR查询) |

OCR寄存器(操作条件) |

| R4 |

48 bit |

CMD5(SDIO专用) |

I/O OCR + Function数量 |

| R5 |

48 bit |

CMD52/CMD53(SDIO读写) |

SDIO状态 + 读取数据 |

| R6 |

48 bit |

CMD3(获取RCA) |

相对卡地址(RCA) |

| R7 |

48 bit |

CMD8(电压检测) |

电压范围确认 |

对于SDIO设备开发者而言,最常打交道的是R1、R4和R5响应,它们覆盖了90%以上的日常操作。

六、上电初始化时序

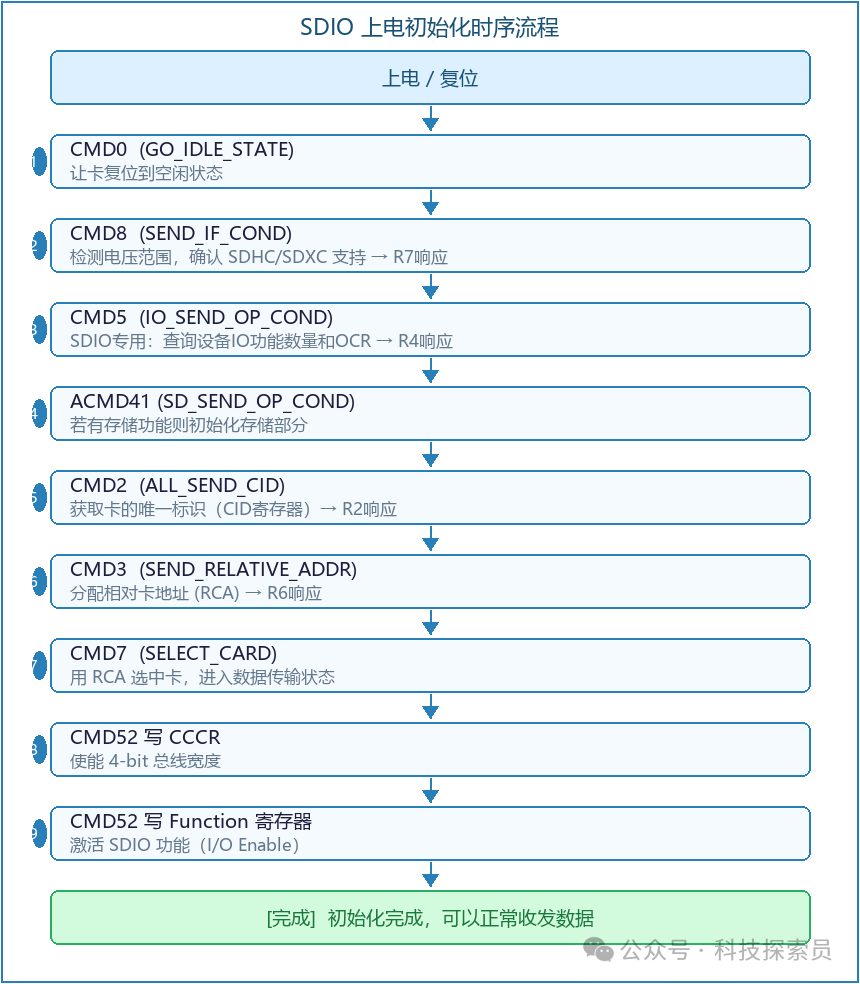

设备上电后,Host必须经过一系列命令“握手”,才能使其进入就绪状态。完整的初始化流程如下图所示:

流程核心:在整个初始化流程中,CMD5是SDIO独有的命令,纯SD存储卡没有这一步。这也是在软件层面区分SDIO设备与纯SD卡的关键。

重要参数:初始化期间时钟频率不能太高,通常需控制在400 kHz以内。初始化完成后再将时钟提升到25 MHz或50 MHz等正常工作频率。理解这一时序对计算机体系结构中的总线初始化逻辑很有帮助。

七、硬件设计关键点与常见问题

7.1 电源与电压

- 标准SDIO工作电压为3.3V,部分高速设备(UHS-I)支持1.8V信号电平以降低功耗和提升速度。

- VDD电源引脚附近需放置100nF + 10μF的滤波电容,并尽量靠近设备引脚。

- 若主控IO电平为1.8V而外设需要3.3V信号,必须增加电平转换芯片,不可直接连接。

7.2 上拉电阻

- CMD和DAT0~DAT3需要连接上拉电阻,典型阻值为10kΩ ~ 47kΩ。

- 上拉电阻应接到VDD(与信号电平保持一致,3.3V或1.8V)。

- CLK信号不需要上拉,保持推挽输出即可。

具体配置如下表:

| 信号线 |

是否需要上拉 |

推荐阻值 |

说明 |

| CLK |

❌ 不需要 |

— |

时钟线,推挽驱动 |

| CMD |

✅ 需要 |

10kΩ ~ 47kΩ |

空闲时保持高电平 |

| DAT0 |

✅ 需要 |

10kΩ ~ 47kΩ |

同上 |

| DAT1 |

✅ 需要 |

10kΩ ~ 47kΩ |

SDIO IRQ中断线,必须上拉 |

| DAT2 |

✅ 需要 |

10kΩ ~ 47kΩ |

4-bit模式使用 |

| DAT3 |

✅ 需要 |

10kΩ ~ 47kΩ |

卡检测/数据线双功能 |

7.3 走线与信号完整性

涉及高速信号时,良好的PCB布局布线至关重要,这与网络/系统设计中对信号完整性的要求类似。

- CLK走线应尽量短,避免不必要的过孔,并保持阻抗连续(建议50Ω)。

- DAT0~DAT3和CMD线应与CLK线做等长处理,长度差异建议控制在±5mm以内。

- 远离高频干扰源(如开关电源、晶振),必要时在信号线周围进行屏蔽地铺铜。

- SD卡座附近应添加ESD保护器件(如PRTR5V0U2X),防止热插拔时产生的静电损坏主控或设备芯片。

7.4 常见问题与排查

下表列出了一些硬件调试中常见的问题现象、可能原因及解决方法:

| 现象 |

可能原因 |

解决方法 |

| 设备识别失败 / CMD5无响应 |

时钟频率过高 或 没有上拉电阻 |

初始化时钟降至400kHz,检查CMD/DAT上拉电阻 |

| CRC 错误频繁 |

走线过长 / 阻抗不匹配 / 接触不良 |

检查PCB走线,优化等长,确认连接器接触良好 |

| 速率低,跑不到4-bit速度 |

驱动未切换总线宽度 或 硬件只接了DAT0 |

软件确认已发送CMD52配置总线宽度,检查DAT1~3物理连接 |

| SDIO中断不触发 |

DAT1没上拉 或 驱动未注册中断 |

检查DAT1上拉电阻,确认驱动中已调用sdio_claim_irq注册中断 |

| 热插拔后设备不识别 |

无卡检测电路 或 无ESD保护 |

连接DAT3/CD引脚实现卡检测,添加ESD保护器件 |

调试建议:硬件调试时,优先使用逻辑分析仪抓取CLK、CMD和DAT0这三根线的波形,90%的通信问题都能从中找到线索。

总结

回顾本篇的核心内容:

- SDIO是SD接口的功能扩展版,用于连接Wi-Fi、蓝牙、GPS等多种外设。

- SD家族:SD (≤2GB) → SDHC (≤32GB) → SDXC (≤2TB),SDIO是独立的功能扩展接口。

- 核心引脚:CLK(时钟)+ CMD(命令/响应)+ DAT0~DAT3(数据)+ 电源/地。

- 工作模式:4-bit模式速率约为1-bit模式的8倍,是产品标配。

- 命令帧:48bit固定格式(起始位+方向+命令索引+参数+CRC+结束位)。

- 初始化流程:CMD0 → CMD8 → CMD5 → ACMD41 → CMD2 → CMD3 → CMD7 → 配置4-bit → 激活功能。

- 硬件设计要点:上拉电阻、电源滤波、等长走线、ESD保护缺一不可。

掌握这些硬件原理是进行SDIO驱动开发和调试的基础。希望这篇详解能帮助你彻底理解SDIO总线。如果你对Linux内核中的SDIO驱动实现感兴趣,或在其他嵌入式系统开发中有更多疑问,欢迎在云栈社区交流探讨。