栅极漏电深度解析:隧穿效应、栅氧缺陷与热电子注入

在晶体管的微观世界里,栅极如同一个精密的阀门,理论上应该完全绝缘,在关断状态下不让任何电流流过。然而现实并非如此——总有一些“不听话”的电子会偷偷穿过那道看似坚固的绝缘墙,形成 栅极漏电流。这个小小的漏电,轻则增加芯片功耗,重则导致器件失效。那么,究竟是什么让栅极“关不紧”?我们从最基本的物理公式出发,一探究竟。

一、漏电的第一性原理:电子如何“穿墙”

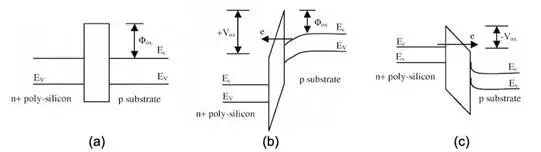

栅极漏电的本质是 量子隧穿效应。栅氧化层极薄(仅几纳米甚至亚纳米),对于电子来说,它不再是一堵不可逾越的墙,而是一道“薄纱”。根据量子力学,电子有一定概率直接穿透势垒。描述隧穿电流的基本公式是:

$$

J = A \times E^2 \times \exp(-B / E)

$$

其中,$J$ 是隧穿电流密度,$E$ 是栅氧化层中的电场强度,$A$ 和 $B$ 是与势垒高度和电子有效质量相关的常数。这个公式揭示了一个关键结论:电场越强,隧穿电流呈指数级增长。而氧化层中的电场 $E \approx (V_{gs} - V_{fb}) / T_{ox}$,其中 $V_{gs}$ 是栅压,$V_{fb}$ 是平带电压,$T_{ox}$ 是氧化层厚度。因此,$T_{ox}$ 越薄、栅压越高,漏电就越严重。

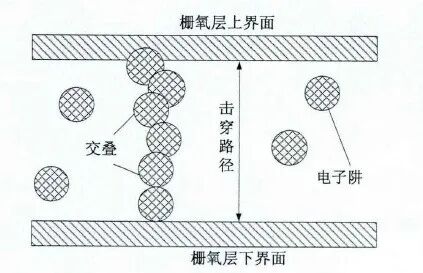

除了直接的隧穿,还有 福勒-诺德海姆隧穿(高电场下电子隧穿进入氧化层导带)和 陷阱辅助隧穿(电子借助氧化层中的缺陷能级“跳跃”通过)。后者与工艺缺陷密切相关。

二、栅氧缺陷:隧穿的“跳板”

理想氧化层中,电子只能靠直接隧穿。但实际氧化层存在大量 缺陷——氧空位、硅悬挂键、金属杂质等。这些缺陷在氧化层禁带中引入局域能级,成为电子的“跳板”。陷阱辅助隧穿的电流公式为:

$$

J \propto N_t \times \exp(-\alpha / E)

$$

其中 $N_t$ 是陷阱密度。缺陷越多,漏电越大。栅氧缺陷的来源很多:沉积或热氧化过程中的工艺波动、等离子体损伤、金属污染等。尤其在先进工艺中,高k介质(如 HfO₂)与硅界面处的缺陷密度远高于 SiO₂,必须通过界面层和退火来钝化。

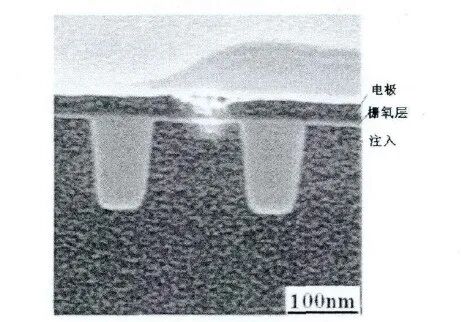

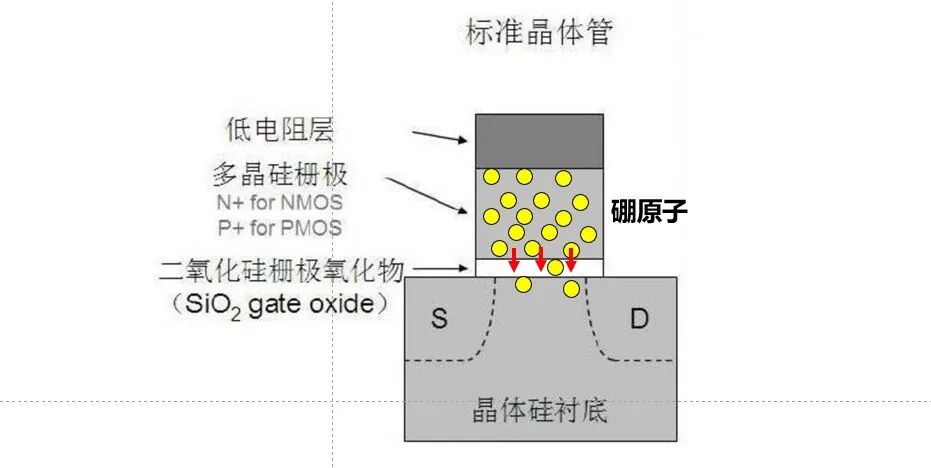

三、离子注入浓度:间接影响漏电

离子注入主要影响沟道掺杂浓度,进而影响阈值电压和栅氧化层中的电场分布。高掺杂沟道会使平带电压 $V_{fb}$ 发生偏移,从而改变栅氧化层中的有效电场。更关键的是,源漏区的重掺杂可能导致 栅极边缘电场集中,局部电场增强,使隧穿电流增大。此外,注入损伤若未完全退火修复,会在硅表面留下缺陷,这些缺陷可延伸至氧化层中,成为漏电路径。

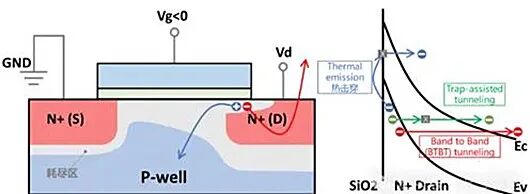

四、热电子效应

当晶体管处于饱和工作区时,沟道中的电子被强电场加速,获得高能量成为“热电子”。部分热电子会向栅极方向散射,撞击氧化层。如果能量足够高(大于 3.1 eV 的 Si-SiO₂ 势垒),就能注入氧化层,产生 衬底热电子注入 电流。更严重的是,热电子撞击会在氧化层中产生新的缺陷,导致 经时介电击穿——随着时间推移,漏电逐渐增大,最终栅氧短路。热电子效应与沟道电场强度、衬底电流、栅压密切相关。通过轻掺杂漏区(LDD)和侧墙结构,可以缓和沟道电场,抑制热电子产生。

五、其他制程因素

- 栅氧化层厚度均匀性:局部减薄区域电场集中,漏电呈指数增加。

- 退火温度与气氛:不适当的退火可能导致氧化层中氢原子扩散,形成缺陷。

- 刻蚀损伤:栅极刻蚀过程中的等离子体会损伤氧化层边缘,引入陷阱。

总结

栅极漏电是多因素协同作用的结果。从第一性原理看,隧穿电流对氧化层厚度、电场强度和缺陷密度极其敏感。栅氧缺陷提供陷阱辅助通道,热电子注入产生新缺陷并直接贡献电流,离子注入影响电场分布,栅极功函数决定势垒高度。在先进工艺中,工程师通过优化栅介质(高k+金属栅)、精细退火钝化缺陷、设计LDD抑制热电子、精确控制注入分布,将栅极漏电控制在皮安每微米量级。每一次漏电的降低,都意味着更长的待机时间和更可靠的开关——在纳米尺度的战场上,这堵“绝缘墙”的坚固程度,决定了整个芯片的功耗与寿命。 |