超结MOSFET(Super-Junction MOSFET,简称SJ-MOS)是一种在高压功率半导体领域中突破传统性能限制的关键器件。它通过在器件结构中引入交替分布的P型与N型柱区,实现了在高耐压下仍保持低导通电阻的特性,显著提升了功率转换效率与功率密度。

传统高压MOSFET的瓶颈与超结的提出

在高压(通常指600V以上)功率MOSFET中,导通电阻主要由低掺杂的漂移区贡献。为了提高器件的击穿电压,传统方法需要进一步降低漂移区掺杂浓度并增加其厚度,但这会导致导通电阻呈指数型上升。这种击穿电压与导通电阻之间的制约关系被称为“硅极限”(Silicon limit),严重阻碍了高压功率器件的发展。

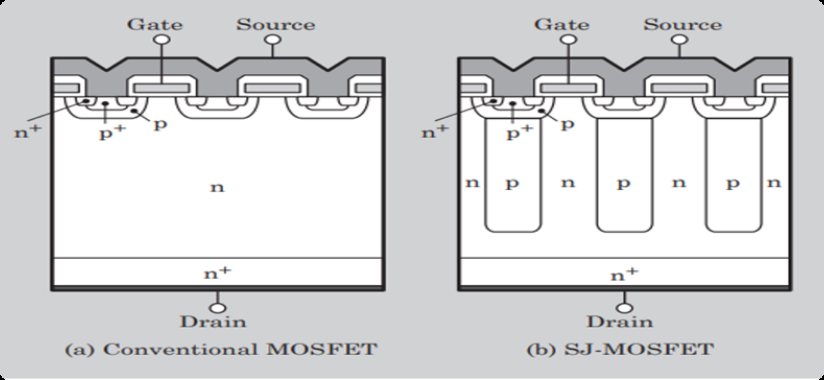

图1:常规MOSFET与SJ-MOSFET的结构剖面对比示意图

为解决这一矛盾,基于陈星弼院士提出的“复合缓冲层”理论,业界研发出了超结MOSFET。其核心思想是通过结构创新,在保持高耐压的同时大幅降低导通电阻,从而突破硅材料的理论极限。

超结MOSFET的结构与工作原理

超结MOSFET的基本结构是在传统VDMOS的漂移区中,制备出交替排列、垂直分布的P型柱和N型柱。从剖面看,这些P/N柱如同在漂移层中树立起的多个垂直PN结。

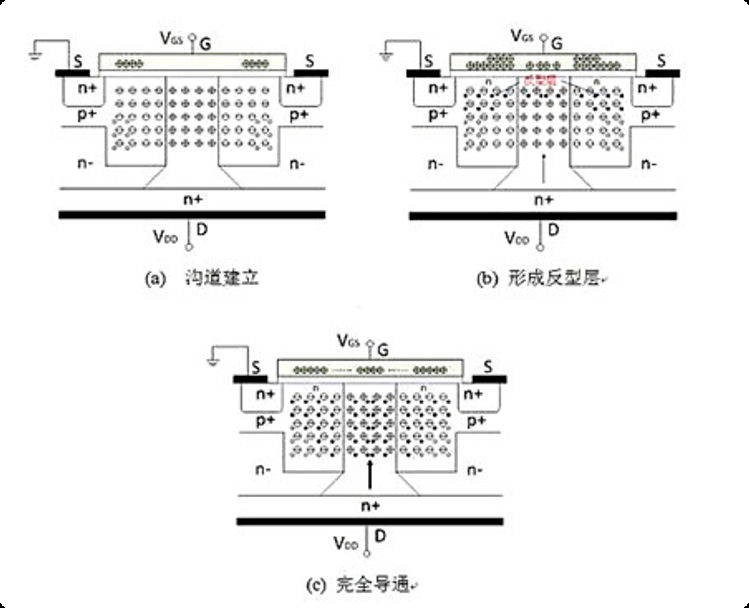

其工作原理的关键在于 “电荷平衡”与“横向耗尽” 。当器件处于关断状态并承受反向电压时,相邻的P柱与N柱之间会发生横向的相互耗尽。在理想电荷平衡状态下,整个漂移区可被完全耗尽,形成一个近似本征半导体(i区)的层。此时,器件的耐压机制转变为类似PIN二极管:由P体区、完全耗尽的漂移区(i区)和N+衬底共同承受电压,电场分布更接近理想的矩形,从而能在更薄的区域内实现更高的击穿电压。

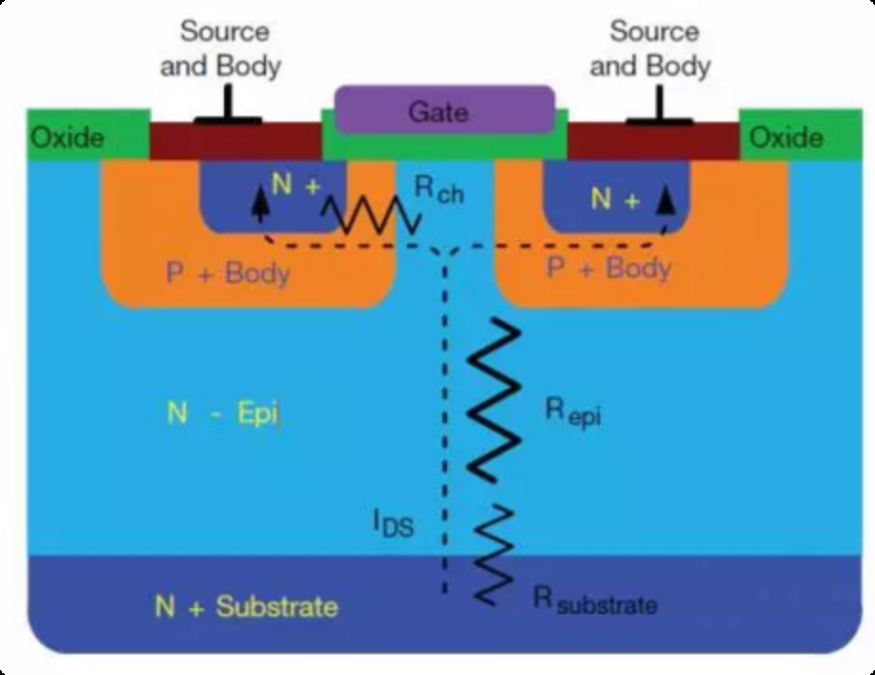

图2:PN结耗尽区形成的原理示意图

由于耐压不再主要依赖于低掺杂的N型漂移区,因此超结结构中的N柱可以大幅提高掺杂浓度。当器件导通时,高掺杂的N柱为电流提供了低电阻通路,从而显著降低了器件的比导通电阻。这种通过精巧结构设计来优化性能的思路,与计算机系统中通过架构优化来提升效率有异曲同工之妙。

主要制造工艺

实现超结结构对工艺制程要求极高,目前主流工艺有以下两种:

多次外延及离子注入法:该方法通过多次外延生长硅层并交替进行离子注入,形成多层交替的P/N型薄层,再经过高温推进使杂质纵向扩散连通,最终形成连续的P柱和N柱结构。该工艺成熟,设计灵活,每层剂量可调,所得器件可靠性高,动态特性好,但工艺步骤繁多,成本较高。

深沟槽刻蚀填充法:先在重掺杂衬底上生长低掺杂外延层,然后通过深反应离子刻蚀形成深宽比很高的沟槽,再在沟槽中外延填充P型硅,形成P柱。该工艺步骤相对简单,成本较低。但挑战在于沟槽刻蚀的形貌控制、填充完整性以及避免产生微观缺陷方面难度较大,可能对器件长期可靠性和动态特性产生影响。

图3:MOSFET从关断到完全导通不同阶段的沟道形成过程示意图

超结MOSFET的性能优势与应用

与传统VDMOS相比,超结MOSFET在多项关键性能上取得显著提升:

导通电阻显著降低:在相同的耐压和芯片面积下,超结MOSFET的导通电阻可比传统VDMOS降低50%-80%。这主要得益于其N柱区的高掺杂浓度。

开关速度更快:超结结构的特性使其开关速度比传统VDMOS快30%以上,有利于降低开关损耗。

芯片面积更小:由于比导通电阻低,实现相同额定电流所需的芯片面积更小,利于设备小型化。

工作效率与温升改善:更低的导通损耗和开关损耗直接提升了电源系统的整体效率,通常可带来1-2个百分点的效率提升,同时器件发热大幅降低。

正因具备“高耐压、低损耗、快开关、小体积”的核心优势,超结MOSFET成功解决了传统VDMOS在中高压领域(600V-1200V)的性能瓶颈,被广泛应用于对效率和功率密度要求严苛的场合,如服务器电源、工业电源、新能源汽车、充电适配器等。

超结MOSFET通过巧妙的电荷平衡原理和独特的纵向P/N柱结构,有效打破了高压硅基功率器件的“硅极限”,实现了导通电阻与击穿电压关系的优化。尽管其制造工艺复杂,面临成本与可靠性的平衡挑战,但其优异的综合性能使其已成为高压高效功率转换领域不可或缺的器件。随着工艺技术的持续进步,超结MOSFET将继续在推动电力电子设备向更高效率、更小体积、更优性能方向发展过程中扮演关键角色。

对半导体器件原理和工艺的深入理解,有助于我们把握硬件技术的核心。更多关于计算机底层原理和硬件架构的深度讨论,欢迎访问云栈社区进行交流。