做嵌入式开发,存储是绕不开的话题。从挂在 I²C/SPI 总线上的小容量 EEPROM,到运行 Linux 系统的 eMMC,再到高速的 NVMe SSD,不同应用场景下对存储器的选择和用法差异巨大。本文将从一个实战者的视角出发,系统性地梳理在嵌入式开发中最常打交道的几类存储接口,帮助你在项目选型和问题排查时做到心中有数。

我们首先需要明确一个基本分类:嵌入式系统中的存储,根据掉电后数据是否保留,可以分为两大类:

- 非易失性存储:掉电后数据不丢失。这是本文的重点,涵盖 SPI/QSPI Flash、EEPROM、eMMC、SD卡、NVMe SSD等。

- 易失性存储:掉电后数据清零。典型代表是 DDR SDRAM(包括 LPDDR),作为系统的运行内存。

1. SPI / QSPI Flash

1.1 基本概念

SPI Flash 是一种使用 SPI(Serial Peripheral Interface) 通信协议的非易失性存储器,通常特指 SPI NorFlash。它通过串行接口与处理器连接,具有成本低、封装小等优点。QSPI 则是基于标准 SPI 协议演进而来的四线增强版本,不仅增加了数据线数量,还引入了队列传输机制,是目前嵌入式系统中存放 Bootloader、固件、配置文件等关键数据的首选。

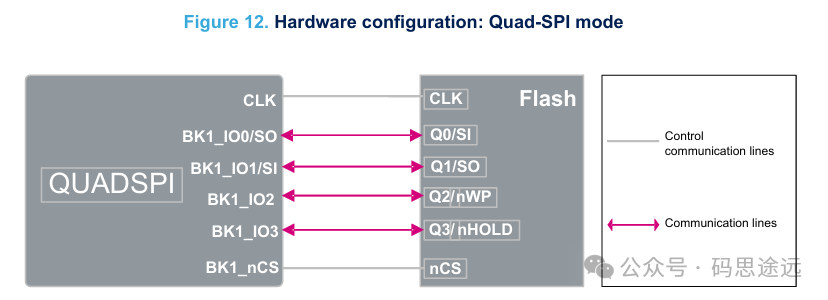

QSPI 在 MCU 上的典型连接引脚包括:CLK、CS#、Q0 (SI)、Q1 (SO)、Q2 (WP#)、Q3 (HOLD#)。

1.2 工作原理

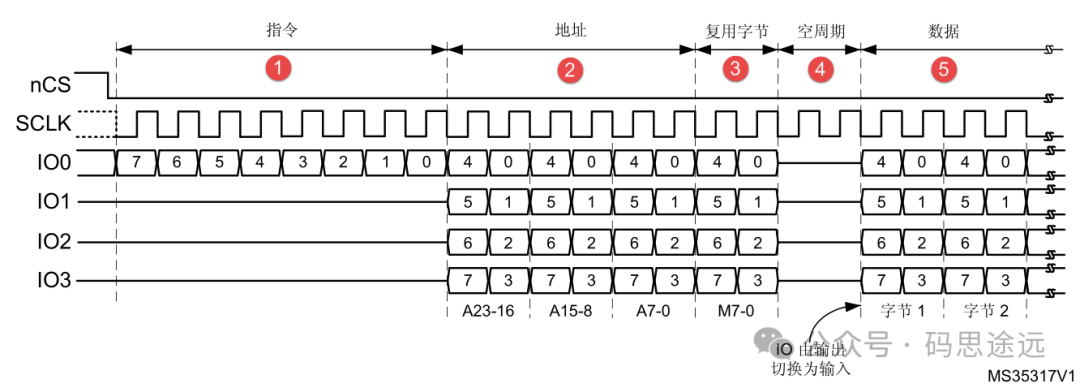

一个典型的四线模式读命令时序如下所示:

标准的 QSPI 读时序通常由以下5个阶段构成:

- 指令:定义要执行的操作命令。

- 地址:指定要操作的目标地址。

- 模式位:一般存在于 Nor Flash 设备中,用于标识是否支持 SIOO(连续指令输出)模式。

- 空周期:等待周期,为从设备的数据输出提供准备时间。

- 数据:传输的实际数据。

QSPI 接口的主要特点包括:

- 四线模式:使用四根数据线(IO0、IO1、IO2、IO3)进行数据传输,相比单线 SPI,理论传输速率提升四倍。

- DMA 支持:许多 MCU(如 STM32)的 QSPI 接口支持 DMA,可以进一步降低 CPU 负载,提高数据传输效率。

1.3 进阶用法

- XIP:很多微控制器(如 STM32, ESP32)支持直接在 Flash 上运行代码,无需将代码拷贝到 RAM。这要求驱动程序正确配置 Flash 的快速读取指令(如

0xEB)。XIP 对于资源紧张的微控制器尤其有用。

- SFDP:现代 Flash 芯片支持 SFDP 协议,驱动程序可以通过读取特定的寄存器来自动获取 Flash 的容量、页大小、擦除指令等参数,从而实现驱动的通用化,无需为每种 Flash 型号单独编写配置。

1.4 使用场景

- 固件/Bootloader 存储:最典型的用途,存放应用程序或 OTA 升级包。

- 外部日志存储:将系统运行日志循环写入 QSPI Flash,掉电不丢失。

- 图形资源存储:存储字库、图片等静态资源,通过 XIP 或 DMA 读取后送至显示屏。

- 配置参数持久化:存储设备出厂参数、用户配置等需要掉电保存的少量数据。

硬件设计注意:当 QSPI 工作频率过高时,若 PCB 走线不等长或阻抗不匹配,可能导致读取数据时发生位偏移,现象是系统随机崩溃或数据校验失败。

2. EEPROM

2.1 基本概念

EEPROM 是一种掉电后数据不丢失的存储器,支持字节级的随机擦写,是嵌入式系统中存储少量关键配置参数的首选。与 NOR Flash 相比,EEPROM 无需进行块擦除,可以直接按字节覆写,操作简单。但其容量通常较小(常见为 1 Kbit~4 Mbit),且单价较高,不适合存储大量数据。

2.2 接口类型

EEPROM 最常用的两种通信接口对比如下:

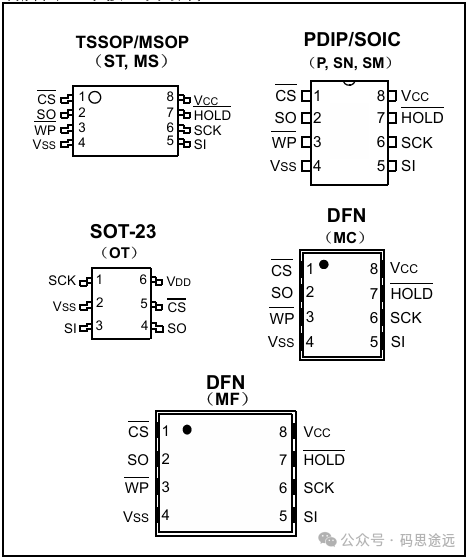

此外,部分型号还提供 1-Wire 接口,适用于线数极度受限的场合。常见的封装形式如下图所示:

2.3 核心特点

- 高耐久性:典型擦写寿命约为 100 万次(部分工业级产品可达 1000 万次),远超普通 NOR Flash 的 10 万次。

- 长数据保持期:数据保存时间通常 ≥ 10 年(25°C 条件),工业级产品可达 40 年或更久。

- 字节级寻址:可单独读写任意一个字节,无需进行块擦除操作。

- 写周期保护:写操作完成前,芯片会拉低 ACK(I²C)或 BUSY 信号,驱动程序必须轮询等待(通常为 1~10 ms)。

2.4 代表厂商与使用场景

代表厂商:

- Microchip:AT24Cxx / AT25Cxx 系列,市场占有率高,资料丰富。

- ST:M24C / M95C 系列,广泛用于工业控制和汽车电子。

- Rohm:BR24 系列,低功耗设计,适合电池供电设备。

- 聚辰半导体:GT24C / GT93C 系列,国产替代方案,性价比高。

典型使用场景:

- 设备序列号 / MAC 地址存储:出厂时烧录,运行中只读,防止意外篡改。

- 用户配置参数保存:如 PID 参数、校准系数、通信波特率等,设备重启后自动恢复。

- 运行时间 / 事件计数器:记录设备累计运行时长、故障次数等统计信息。

- 安全密钥存储:部分型号内置唯一序列号,可用于设备认证。

3. eMMC

3.1 基本概念

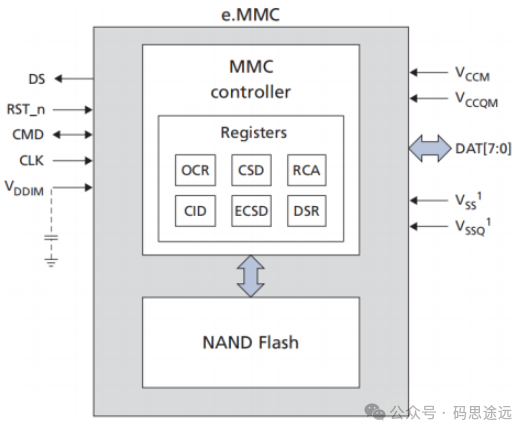

eMMC 是由 JEDEC 标准组织制定的嵌入式存储标准,它将 NAND Flash 存储阵列和专用控制器封装在同一颗 BGA 芯片中,通过统一的 MMC 协议对外提供块设备访问接口。这种集成方式对开发者屏蔽了 NAND Flash 底层的复杂细节(如坏块管理、位翻转纠错等),使其使用起来如同普通硬盘一样简单。eMMC 是目前消费电子和工业嵌入式 Linux 设备中最主流的主存储方案。

其核心是“主控制器 + NAND 闪存阵列”的集成方案,主控制器负责管理闪存读写、坏块管理、磨损均衡、ECC纠错、垃圾回收以及协议转换等任务。

3.2 接口与规格

eMMC 采用并行总线接口:

- 数据总线:1 位、4 位或 8 位(主流)。

- 控制信号:CLK(时钟)、CMD(命令/响应)。

- 封装形式:BGA,直接焊接在 PCB 上,不可插拔。

主流的速度等级演进如下:

| 模式 |

总线宽度 |

时钟频率 |

理论带宽 |

| HS(High Speed) |

8-bit |

52 MHz |

~52 MB/s |

| HS200 |

8-bit |

200 MHz |

~200 MB/s |

| HS400 |

8-bit DDR |

200 MHz |

~400 MB/s |

3.3 Linux 开发要点

在嵌入式 Linux(如基于 RK3568 的平台)中使用 eMMC,需要关注设备树的配置:

&sdhci {

bus-width = <8>;

max-frequency = <200000000>;

mmc-hs400-1_8v;

non-removable;

status = "okay";

};

关键属性解析:

bus-width:设置总线宽度。mmc-hs400-1_8v:使能 HS400 模式,并使用 1.8V IO 电压。non-removable:告知内核驱动此设备不可热插拔。

典型应用:智能手机、平板电脑、智能电视盒子、工业网关等产品的主存储。例如,搭载 RK3568 的商用设备,其 Android 或 Linux 系统通常直接运行在板载 eMMC 上。

4. SD / TF 卡

4.1 基本概念

SD 卡及其小尺寸版本 TF 卡(MicroSD)与 eMMC 使用相同的 SDMMC 协议,核心区别在于 SD 卡是可插拔的。在嵌入式系统中,SD 卡常作为辅助存储,用于数据导出、系统升级或备份。

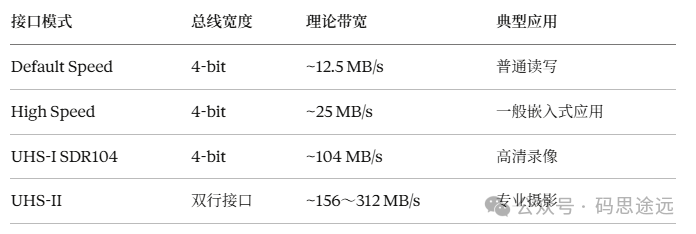

SD 卡的接口模式与速度不断演进,常见规格对比如下:

4.2 Linux 开发要点

SD 卡与 eMMC 通常共用 SoC 内部的 SDMMC 控制器驱动。设备树配置与 eMMC 类似,但需注意 SD 卡需要配置电源(vmmc-supply)并处理热插拔。

&sdmmc {

status = "okay";

vmmc-supply = <&vcc_3v3_sd_s0>; // 配置 SD 卡设备的 3.3V 电源

};

热插拔处理:内核 MMC 子系统通过 CD(Card Detect)引脚的中断来感知卡的插拔事件,驱动会自动完成设备的枚举和初始化。用户态程序可以通过监听 udev 事件或使用 inotify 监控 /dev/mmcblk* 设备节点的变化。

4.3 速度等级说明

SD 卡的速度标准有多套,容易混淆:

- Speed Class (C):早期的速度等级标准。

- C2 - 最低持续写入速度 2MB/s

- C4 - 最低持续写入速度 4MB/s

- C6 - 最低持续写入速度 6MB/s

- C10 - 最低持续写入速度 10MB/s

- UHS Speed Class (U):针对 UHS-I 总线接口。

- U1 - 最低持续写入速度 10MB/s

- U3 - 最低持续写入速度 30MB/s

- Video Speed Class (V):为视频录制设计的新标准,更严格。

嵌入式选型建议:用于存储系统日志或数据采集缓存,选择 U1 等级的卡即可;若用于视频录制或高频写入场景,建议从 U3 等级起步,并优先选用采用 MLC 颗粒的工业级 SD 卡,以避免消费级 TLC 颗粒卡在频繁写入下寿命过短的问题。

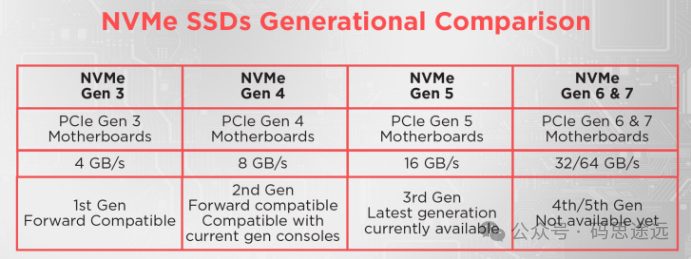

5. NVMe (M.2 接口)

5.1 基本概念

NVMe 是专为闪存存储设计的高性能协议,通过 PCIe 总线连接,彻底突破了传统 SATA 接口的带宽瓶颈。在需要高速录像、大数据处理或 AI 推理的嵌入式场景(如采用 RK3588、NVIDIA Jetson Orin 的平台)中,NVMe SSD 已成为标配。

连接方式:物理上通过 PCIe 总线连接,常见的物理形态是 M.2 接口(M-Key)。

开发重点:

- PCIe 链路训练:NVMe 设备驱动的第一步是 PCIe 链路的初始化。如果链路协商不到预期的 Gen3/Gen4 速度或 Lane 数量不对,性能会大打折扣。

- 电源与散热管理:NVMe SSD 功耗相对较大,在散热有限的嵌入式设备中,需要关注驱动中的

APST(自动电源状态转换)等节能机制,以防止设备过热。

硬件安装注意:在实际调试中,很多“系统找不到硬盘”的问题,根源在于 M.2 接口没有插紧,或者没有使用正确的 M2.5 螺丝 固定,导致 PCIe 差分信号质量差,链路训练失败。

各代 NVMe SSD 的性能对比如下图所示:

RK3588 设备树配置示例:

&pcie2x1l2 {

reset-gpios = <&gpio4 RK_PC1 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

status = "okay";

};

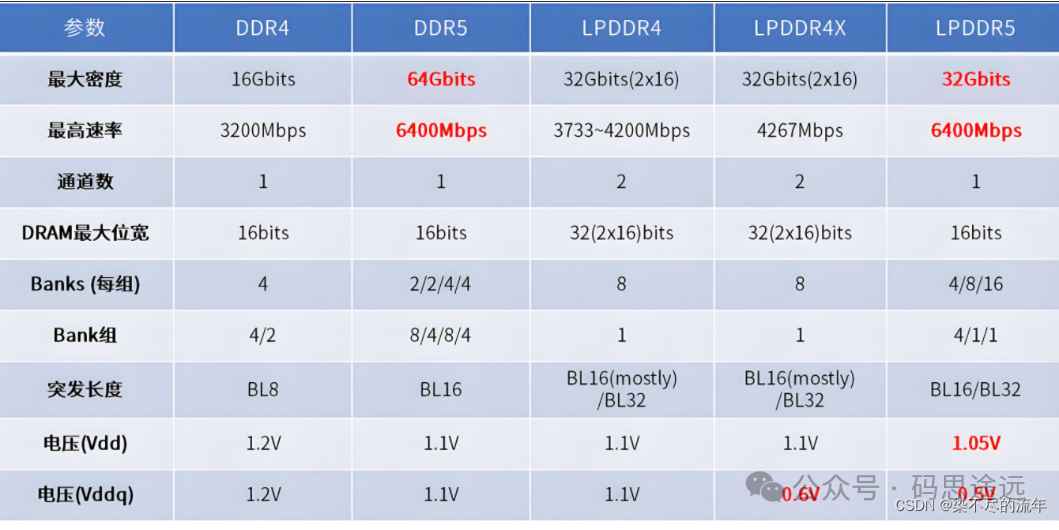

6. DDR (LPDDR4/5)

DDR SDRAM 是嵌入式系统的运行内存,属于易失性存储,但它是整个存储体系中速度最快、对系统稳定性影响最大的部分。LPDDR 是为移动和嵌入式设备设计的低功耗版本,目前主流为 LPDDR4/X 和 LPDDR5。

6.2 DDR Training(信号训练)

DDR Training 是系统上电时,由 Bootloader(如 U-Boot SPL 或芯片原厂提供的初始化代码)执行的一段自动校准流程。其目的是在当前的 PCB 布线环境下,找出最优的信号延迟参数,确保读写稳定。主要包括:

- Write Leveling:补偿 DQS 与 CLK 之间的时序偏差。

- Read/Write DQ Training:逐位调整数据线的延迟,确保建立和保持时间满足要求。

- Vref Training(LPDDR4/5):自动搜索最优的参考电压值。

6.3 调试经验

- 新板必跑内存测试:新硬件回来第一件事就是在 Linux 下运行

memtester 512M 5。如果出现位错误,说明 DDR Training 参数不准确或 PCB 走线存在信号完整性问题。

- 频率降级验证:当怀疑 DDR 稳定性时,可以在 Bootloader 或内核启动参数中临时降低 DDR 工作频率。若问题消失,则很可能是信号完整性或电源问题,而非软件 Bug。

- DFS:系统为了省电,会根据负载动态调整 DDR 频率。DFS 切换瞬间需要 DDR 控制器与电源管理芯片的精确配合,配置不当可能导致切换时系统卡顿甚至崩溃。

- ECC 支持:部分工业级 SoC 支持 DDR ECC 功能,可以自动纠正单比特错误,对于可靠性要求极高的场合建议启用。

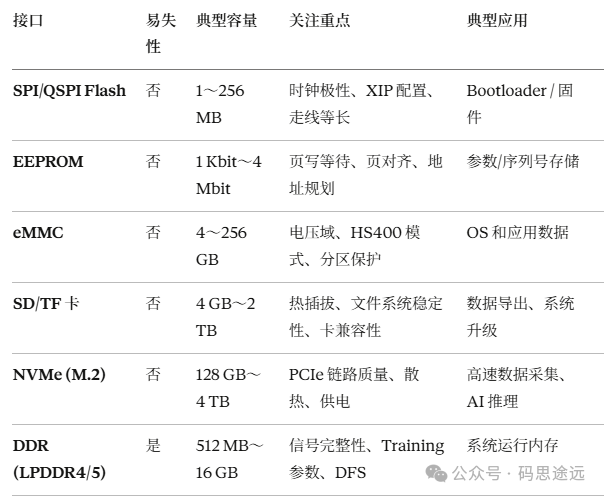

7. 总结与选型参考

为了更直观地进行对比和选型,我们将上述几种存储接口的关键特性总结如下:

实战排错建议:当遇到存储读写异常时,可以遵循以下排查顺序:

- 先看内核日志:执行

dmesg | grep -E "error|timeout|fail"。timeout 错误多半与时钟或电源有关;CRC error 则很可能是硬件信号干扰或布线问题。理解这些网络/系统层面的日志是诊断的第一步。

- 检查供电:使用示波器测量存储器的 VCC 和 VCCQ 等电源引脚,确认没有上电毛刺或欠压情况。

- 降频验证:将接口时钟频率降到规格允许的最低档,看问题是否消失。这能快速区分是硬件信号问题还是软件逻辑问题。

- 替换器件:尝试更换 Flash 芯片、SD 卡或 SSD,以排除器件本身存在缺陷的可能性。

- 查阅勘误表:许多奇怪的问题其实在芯片的官方勘误表中有记录和规避方案,不要一上来就怀疑自己的驱动或设备树(DTS)配置代码。

希望这篇关于嵌入式系统常用存储接口的梳理能对你有所帮助。如果你在实际项目中遇到了其他存储相关的疑难杂症,欢迎到云栈社区与更多开发者一起交流探讨。

参考链接: