硬件电路设计经过长期的实践积累,形成了许多经典且可靠的设计模块。深入理解并掌握这些模块,能够显著提升硬件系统设计的效率,并降低潜在的出错风险。

一次完整的硬件设计,其核心往往围绕着几个主要的功能模块展开:电源模块、存储模块、显示模块以及各类对外通信接口模块。下面我们将逐一解析其中9个关键的设计要点与电路模块。

1. 电源设计:系统的血脉与根基

电源是整个系统稳定运行的基石,值得在成本与设计上进行充分投入,这对于产品通过各项认证和保证长期稳定性至关重要。

- 采用∏型滤波:在电源路径上增加一个10uH电感,形成LC滤波网络,同时为每个芯片的电源引脚配置一个

0.1uF(104)的旁路电容。

- 抑制浪涌:在电源入口处使用压敏电阻或瞬态电压抑制二极管(TVS),以吸收瞬间的高压脉冲。

- 地平面分割:模拟地与数字地应分开布局;大电流与小电流的回流路径也应独立,可以使用磁珠或零欧电阻在单点进行连接。

- 散热余量:确保电源芯片不会过热,当功耗达到其额定值的50%时,就应考虑添加散热片。

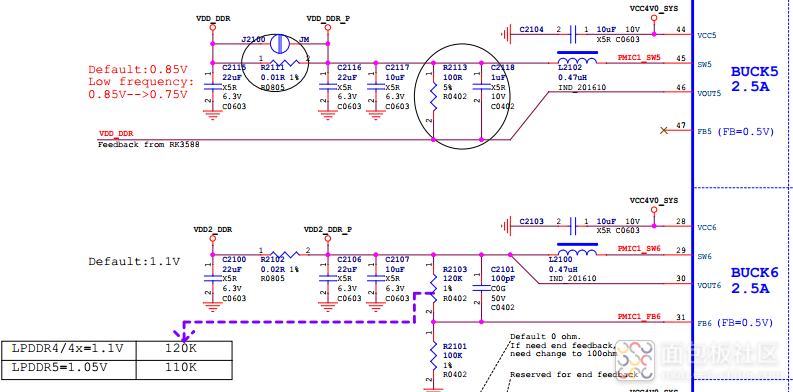

图:BUCK电源模块典型电路,涉及反馈电阻、电感和电容的配置。

2. 输入/输出(I/O)引脚处理

这是一个基础但易错点:输入型IO引脚必须根据芯片手册要求配置上拉或下拉电阻,以确保在悬空时有一个确定的电平状态。输出型IO引脚则需核算其驱动能力,看是否足以驱动后级的负载(如LED、继电器等)。

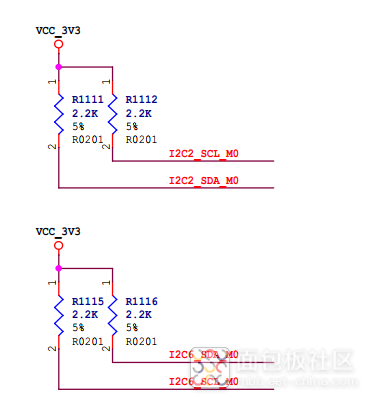

图:I2C总线标准的双线上拉电阻配置,确保信号在高电平时的稳定性。

3. 运算放大器输出端:谨慎对待去耦电容

在直流信号放大电路中,有时为了滤除噪声,会尝试直接在运放输出端并联一个去耦电容。这种做法存在风险:当输入阶跃信号或上电瞬间,运放会输出大电流,且电容会改变环路的相位特性,可能引发电路自激振荡。

正确的做法是构建一个RC滤波网络:在运放的输出端先串联一个小电阻(如几十欧姆),然后再并联去耦电容。这样可以有效限制瞬间电流,同时避免破坏环路的稳定性。

4. 高速信号线的端接匹配

对于布线较长的高速IO信号线(如UART、LVDS等),在驱动端或接收端串联一个33欧姆的电阻,可以有效抑制信号反射,改善信号质量。对于差分信号对(如USB、HDMI),在接收端并联一个阻值等于差分阻抗的匹配电阻(通常在90-100欧姆)是标准做法。

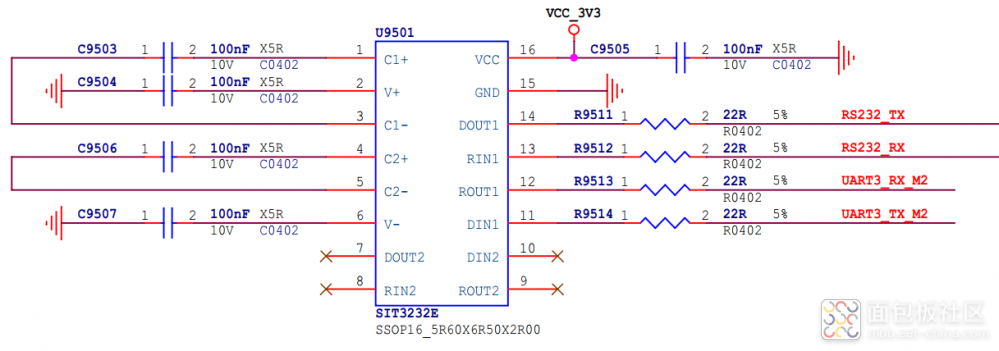

图:RS232接口芯片电路,注意信号路径上的串联匹配电阻。

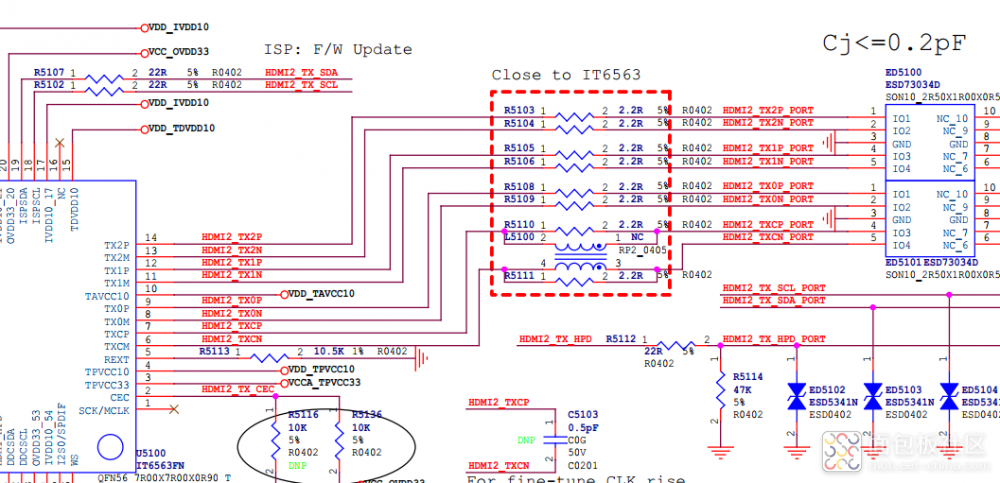

图:HDMI发射端芯片外围电路,包含差分对和电源去耦设计。

5. 确保芯片间电平匹配与完整回流路径

不同芯片之间的通信,必须确保其逻辑电平标准一致(如3.3V LVTTL与5V TTL之间需加电平转换器)。更重要的是,需要为信号电流提供完整的回流路径。根据基尔霍夫电流定律,当一块板卡(A板)向另一块(B板)输送信号或电源时,等量的电流必须从B板的地层流回A板。

因此,在板间连接的接口处,必须分配足够数量的地线引脚,以降低回流路径的阻抗,从而减少地噪声。对于大电流回路,应专门规划其回流路径,避免干扰敏感的模拟或数字信号。

6. 开关器件的过冲抑制

在使用MOSFET、BJT等开关器件时,其快速的开关动作会在寄生电感和电容上产生电压过冲和振铃。这可能导致器件承受超过其额定值的电压应力。设计中应考虑使用缓冲电路(Snubber Circuit),例如RC网络或TVS管,来吸收这部分能量,保护开关器件。

7. 单板可测试性设计

一块优秀的电路板应当具备独立测试其核心功能的能力。这意味着在设计之初就要考虑加入测试点、测试接口(如JTAG、SWD)或自检电路。确保在脱离整机系统时,也能对电源、时钟、核心芯片等进行基本的功能验证。

8. 合理布置测试点

为了方便生产测试和后期调试,应在关键信号网络和电源网络上添加测试点。原则是测试点越小越好(需满足测试探针的要求),其引出的分支线越短越好,以减少对原信号的影响。必须为重要信号(如时钟、复位、关键总线)和所有电源网络、地网络设置专用的测试点。

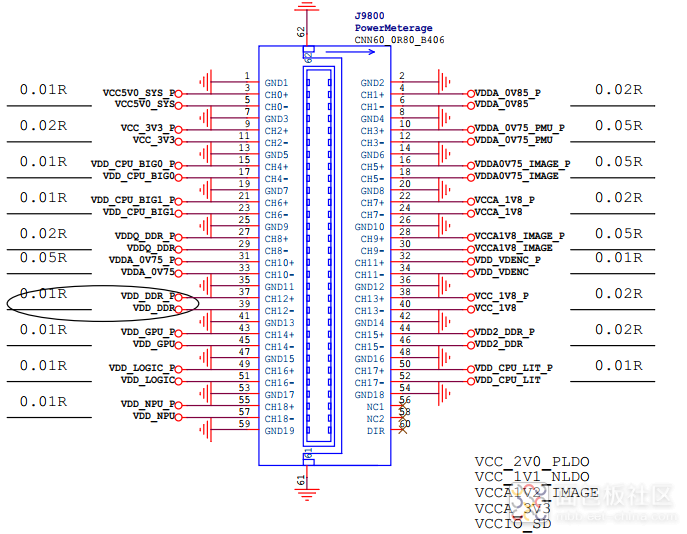

图:电源网络设计,展示了各电压域的分支及采样点,可用于测试。

9. 抑制高频干扰(串扰)

抑制高频干扰的核心思路是减小高速信号产生的交变电磁场对其他线路的影响,即控制串扰。具体措施包括:

- 拉大布线间距:尽可能增加高速信号线与模拟信号线、敏感低速信号线之间的物理距离。

- 使用地线隔离:在敏感的模拟信号线两侧并行布设接地线(Guard Trace),形成屏蔽。

- 处理好地平面:特别注意数字地噪声对模拟地的干扰,通常采用“分地-单点连接”的策略。

如果在每次的原理图与PCB设计中,都能系统地审视并应用以上九点,将极大提高产品设计的一次成功率,减少设计反复,有效缩短开发周期。

掌握这些经典电路模块和设计准则,是每一位硬件工程师快速完成高质量设计迭代的必备计算机基础。如果你对这类硬件设计实战经验感兴趣,欢迎来云栈社区与更多开发者交流探讨。