当地时间 22 日,美国加州圣何塞市圣克拉拉会议中心一早便人头攒动。台积电在全球七大核心地区巡回举办的开放创新平台(OIP)论坛,将半导体设计与制造上下游的合作伙伴汇聚一堂,分享前沿技术成果与协同研发进展。本届北美研讨会以“引领芯片创新,拓展 AI 边界”为主题,集中展示了面向 AI 加速器与高性能计算(HPC)深度优化的一系列创新技术。

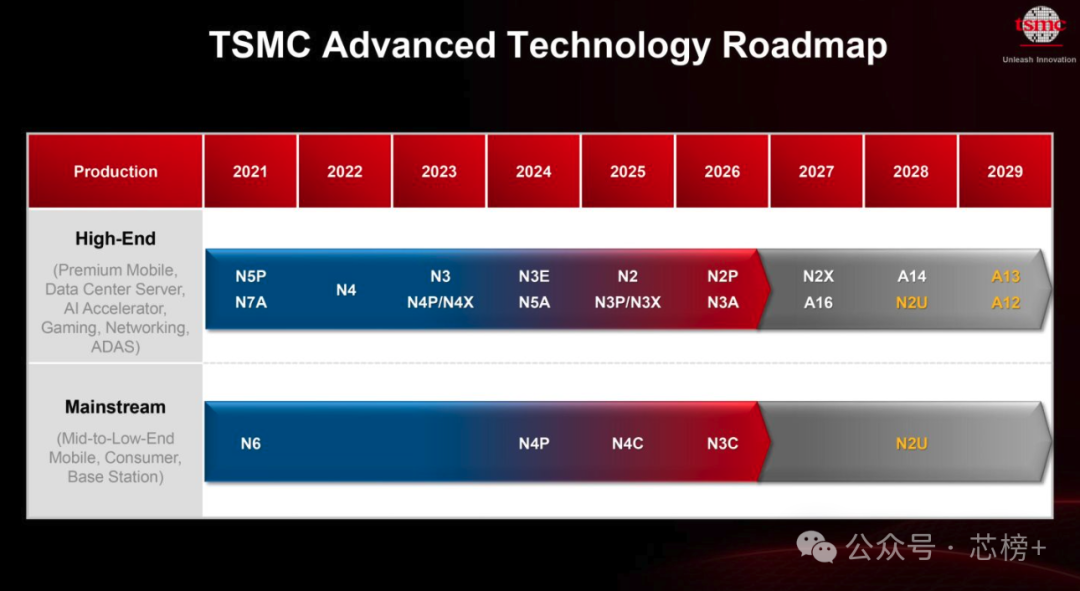

在逻辑芯片领域,大会的焦点无疑是 3 纳米以下的先进制程迭代。从 2 纳米开始,到 A16、A14 等新一代工艺,路线图规划得非常清晰。封装技术层面,台积电也亮出了 CoWoS、InFO、SoIC 等堆叠封装创新方案。依托这套“制程+封装”的组合拳,台积电明确了自己的战略方向:用高密度晶体管与低功耗架构深耕 AI 数据中心及云端市场,全面适配高性能计算、智能手机、自动驾驶等全场景 AI 应用的高速扩张需求。

为了让各位更清晰地理解这些关键技术,我们不妨拆开来看:

- A16 与 A14:A16 是台积电下一代 1.6 纳米级制程工艺;而 A14 则是紧随 A16 之后,规划落地的 1.4 纳米级先进制程。

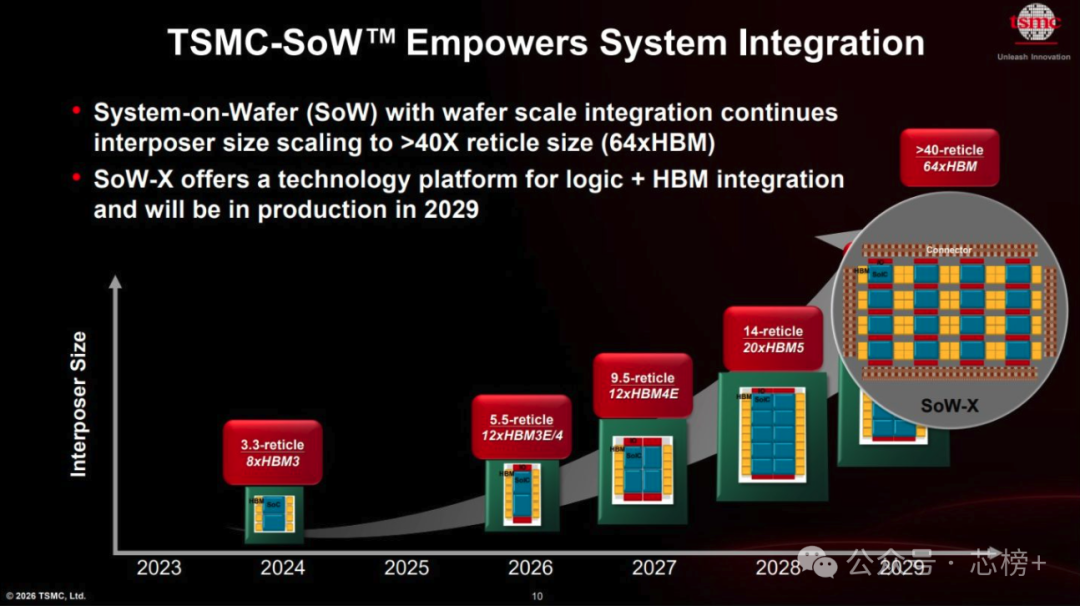

- CoWoS(晶圆基板集成封装):这是台积电知名的 2.5D 封装技术。它将芯片堆叠于晶圆上,再衔接基板,可在单一封装内并列集成逻辑芯片与高带宽内存。这能大幅提升数据传输速率,可以说是当前 AI 加速器与高性能计算的核心支撑技术。

- InFO(集成扇出封装):这项技术直接摒弃了传统封装基板,通过扇出工艺来拓展芯片外围电路。它兼具轻薄化与高能效的优势,目前主要应用于移动终端处理器。

- SoIC(集成芯片系统):作为前沿的 3D 堆叠封装技术,它能让不同芯片实现垂直键合。其中的无凸点混合键合工艺,能进一步拓宽数据传输带宽、缩小芯片体积,是决定下一代 AI 芯片能否顺利量产的核心关键技术。

路线图清晰地显示,台积电正沿着 High-End 与 Mainstream 两条产品线稳步推进。高端线瞄准旗舰手机、数据中心服务器、AI 加速器等场景,而主流线则覆盖中低端移动设备与消费电子。

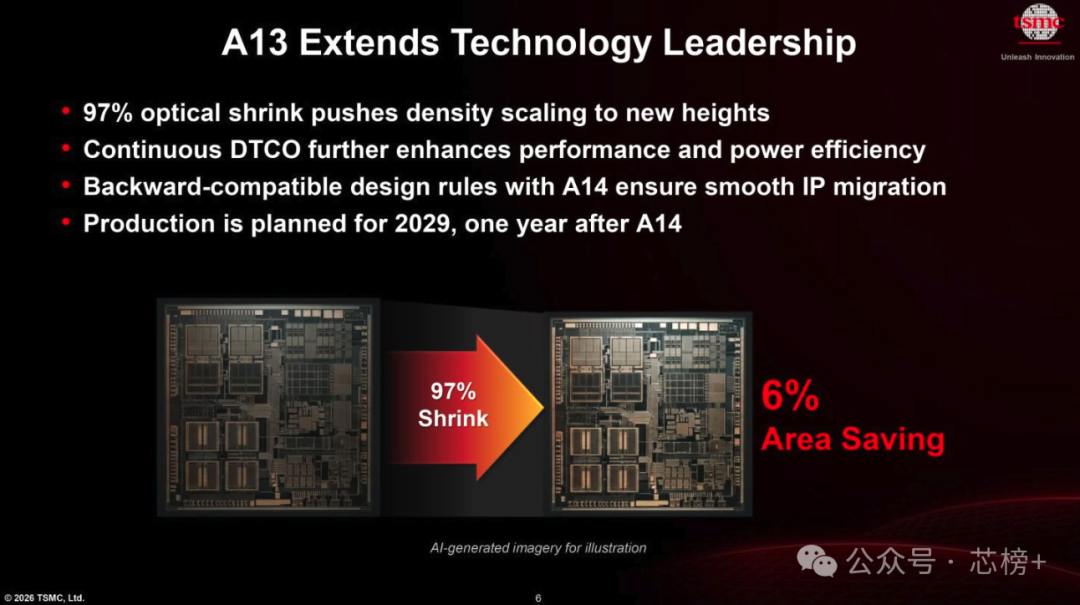

在后续的 A13 技术演示中,我们看到台积电通过 97% 的光学缩放将密度推向新高度,并利用持续的设计技术协同优化(DTCO)来增强性能与能效。特别值得芯片设计工程师关注的是,A13 提供了与 A14 向后兼容的设计规则,这意味着 IP 可以平滑迁移,大大降低了迭代成本。

面向超大规模数据中心,台积电还在 SoW(晶圆级系统集成)技术上持续发力。从 2024 年的 3.3 倍光罩尺寸、集成 8 层 HBM3,一路演进到 2029 年规划中超过 40 倍光罩尺寸、集成 64 层 HBM 的恐怖规格。特别是 SoW-X 平台,它提供了一种将逻辑单元与 HBM 深度集成的技术方案,量产时间定在 2029 年,这无疑是为未来的万亿参数级 AI 模型准备的算力底座。 |