在刚刚结束的IEDM 2025上,台积电首次证实了采用下一代晶体管技术——互补场效应晶体管(CFET)的集成电路的运行情况。

根据IEDM官方此前的预告,台积电在本届大会上宣布了两项重要里程碑:首款全功能101级3D单片互补场效应晶体管(CFET)环形振荡器(RO),以及全球最小的6T SRAM位单元。该SRAM位单元同时提供了高密度和高电流设计。

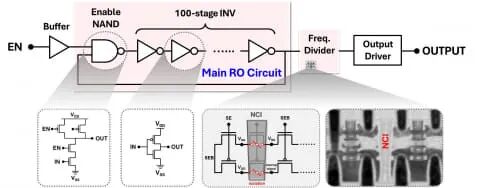

基于先前基于纳米片的单片CFET工艺架构,台积电的研究人员引入了新的集成特性,进一步将栅极间距缩小至48nm以下。他们在相邻FET之间采用了纳米片切割隔离(NCI)技术,并在6T SRAM位单元内采用对接接触(BCT)互连技术实现反相器的交叉耦合。电学特性分析对比了两种环形振荡器布局,重点展示了6T位单元对性能以及稳健SRAM器件指标的影响。

这些进展标志着CFET开发从器件级优化迈向电路级集成的关键性转变。

CFET技术:提升晶体管密度的关键

CFET是一种通过垂直堆叠n沟道FET和p沟道FET(CMOS器件的基本组件)来提高晶体管密度的技术。理论上,与目前最先进的纳米片FET(NS FET)技术相比,其晶体管密度可以提高近一倍。

然而,技术难度已接近极限。纳米片场效应晶体管本身的制造就十分困难,而CFET在此基础上,需要以单片方式垂直堆叠两种类型的晶体管,这自然进一步增加了制造复杂度。

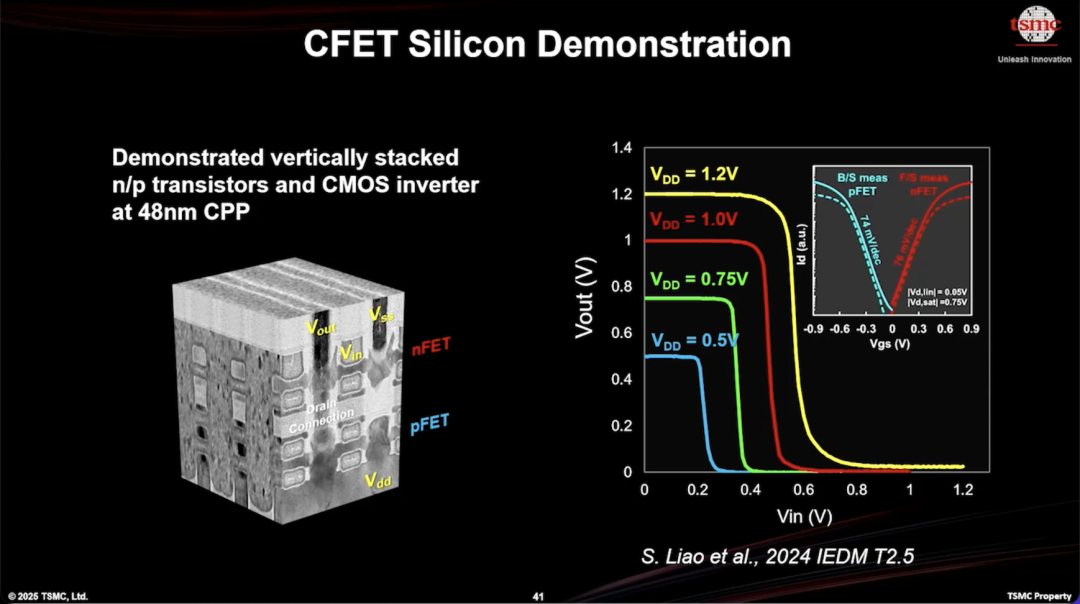

截至目前,CFET的研发成果多限于单个晶体管或由两个晶体管堆叠而成的简单结构。在去年的IEDM会议上,台积电公布了CFET反相器元件(一种用于反转逻辑值的元件)的原型设计和运行结果。

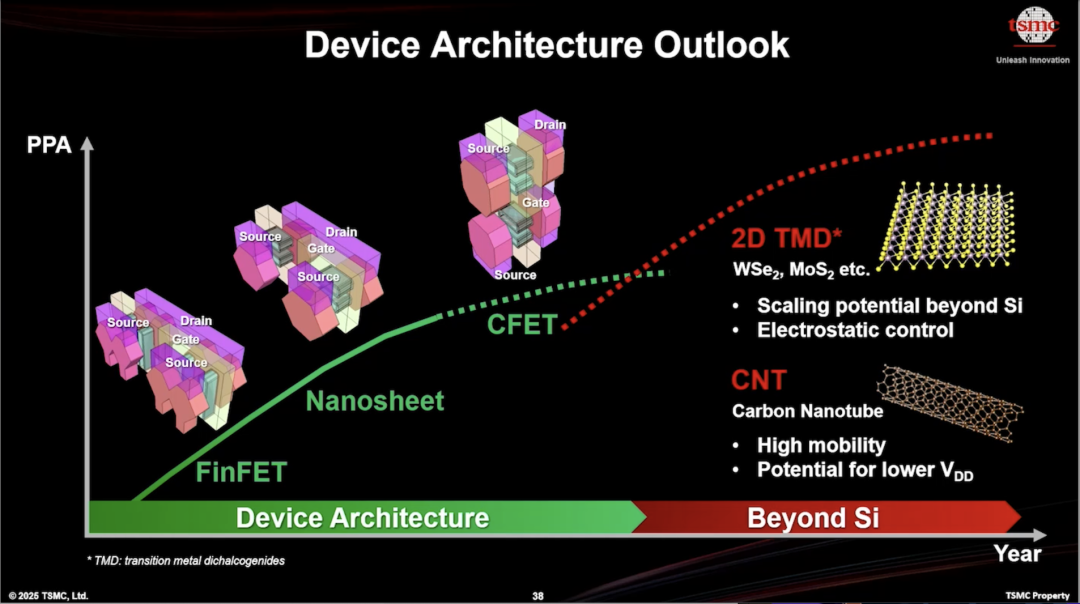

台积电的Yuh-Jier Mii博士在IEDM 2024的演讲中探讨了从FinFET到纳米片FET,再到垂直堆叠互补型CFET架构的演变。他解释说,与纳米片器件相比,CFET器件的密度提高了1.5到2倍,因此极有可能继续推动摩尔定律的扩展。当时,台积电展示了业界首款、也是最小的48nm间距CFET反相器。

Yuh-Jier Mii表示,台积电在IEDM 2024的演示是CFET技术发展的重大里程碑。而最新的研发成果正是在此基础上的延续。

最新成果:环形振荡器与SRAM单元

据悉,台积电制作了两种集成电路原型:一种是逻辑电路基础的“环形振荡器”;另一种是存储电路基础的“SRAM单元”。其中,环形振荡器的规模尤其大,包含了800到1000个晶体管,其设计复杂度和集成度体现了先进集成电路设计的挑战。

环形振荡器由一个使能NAND逻辑元件(环形振荡器输出的反馈元件)和100个反相器元件组成,从而形成一个101级环形振荡器。该原型的工作电压范围为0.5V至0.95V。随着电源电压的升高,振荡频率增大,频率的波动减小。具体振荡频率数值未予公开。

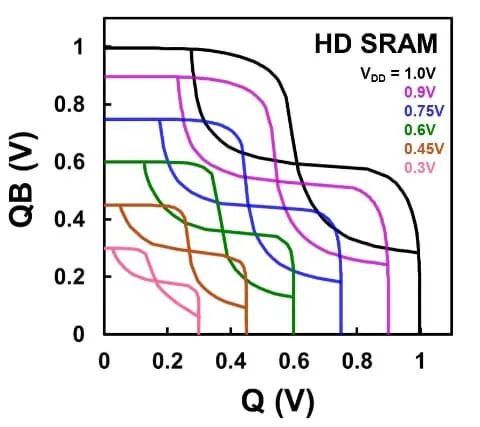

SRAM单元采用标准的六晶体管电路配置。台积电制作了两种类型的SRAM单元原型:一种是优先考虑存储密度的HD(高密度)型,另一种是优先考虑性能(驱动电流)的HC(高电流)型。两种类型均已验证可正常工作。

HD型单元的面积比采用几乎相同设计规则的纳米片FET单元小30%。如果采用CFET技术,则HD型单元的面积比HC型小20%。然而,HC型单元的读取电流是HD型单元的1.7倍。

SRAM单元电路具有一种称为“交叉耦合”的独特连接方式,需要对接触点(BCT)来互连上、下FET。原型HD型SRAM单元的工作电压范围为0.3V至1.0V。当电源电压为0.75V时,读取静态噪声容限(RSNM)为135mV,读取电流为17.5μA,写入容限(WM)为265mV。台积电表示,该SRAM单元参数尚未优化,仍有改进空间。

CFET技术在逻辑和存储器领域实现实际应用的目标时间是2030年代。目前开发的集成电路仍处于非常初级的阶段,距离实际应用还有很长的路要走。

材料与互连技术的未来布局

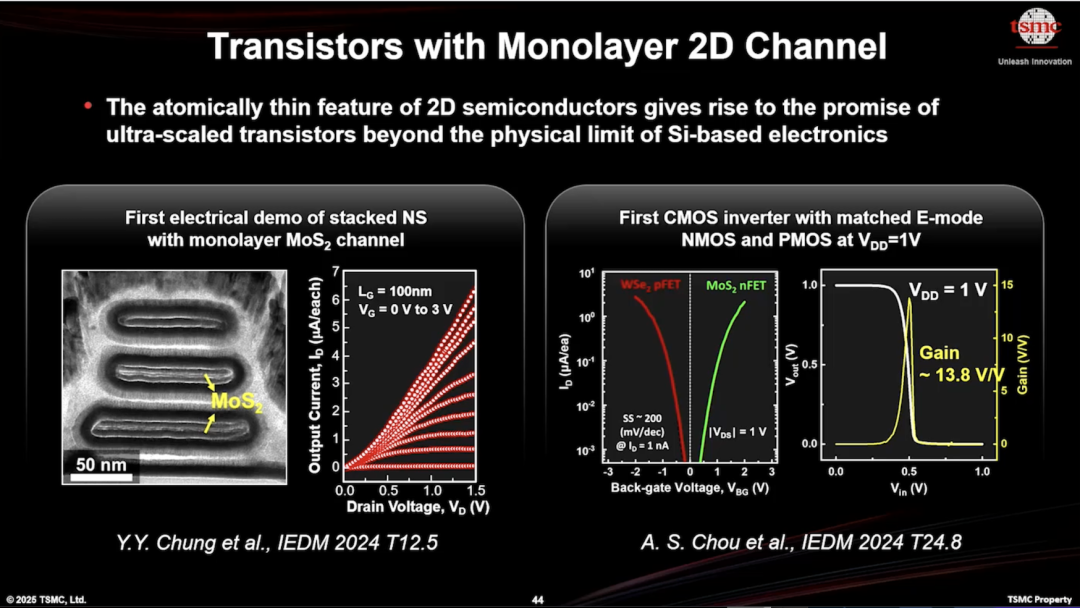

根据Yuh-Jier Mii在IEDM 2024年的报告,采用二维沟道材料的晶体管也取得了显著进展。台积电已首次展示了采用与N2技术类似的堆叠纳米片结构中的单层沟道晶体管的电性能,并开发了一种采用匹配良好的N沟道和P沟道器件、工作电压为1V的反相器。

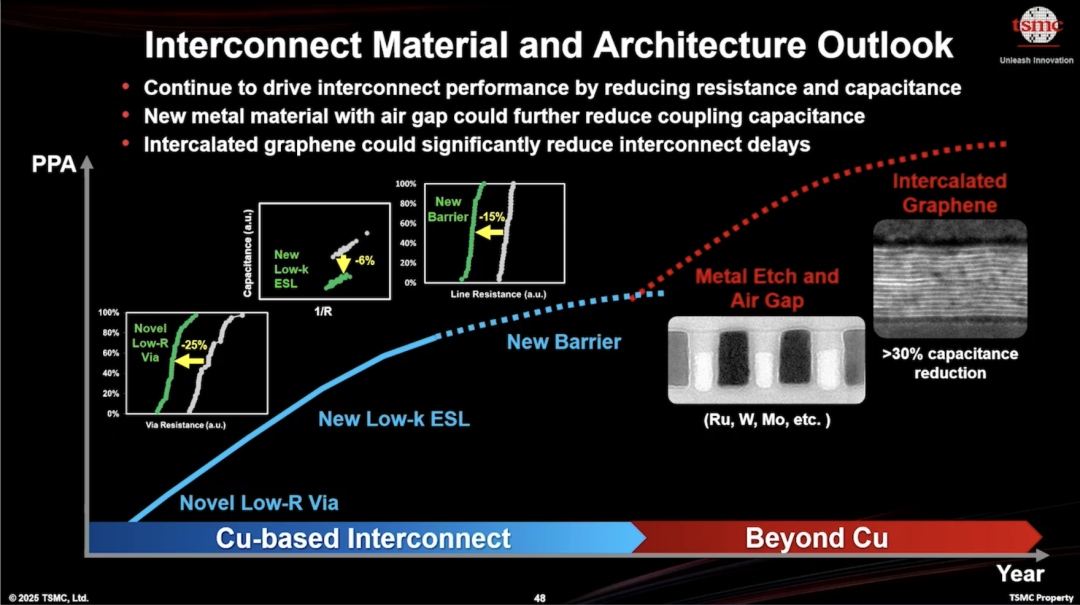

展望未来,台积电还计划继续开发新的互连技术以提升性能。对于铜互连,计划采用新的过孔方案来降低过孔电阻和耦合电容。同时,还在研发一种新的铜阻挡层以降低铜线电阻。

除了铜,目前正在研发具有气隙的新型金属材料,有望进一步降低电阻和耦合电容。插层石墨烯是另一种极具前景的新型金属材料,未来有望显著降低互连延迟。

行业竞争:三星与英特尔的进展

除了台积电,三星和英特尔也在积极布局CFET技术。

英特尔是三家中最早展示CFET的厂商,早在2020年的IEDM上就发布了早期版本。在2023年的IEDM上,英特尔宣布对CFET最基本的电路——反相器——进行了多项改进。通过采用背面供电技术从硅片下方连接底部晶体管,英特尔成功简化了电路,将反相器的接触多晶硅间距(CPP)缩小至60纳米。

三星则展示了更小的48纳米和45纳米CPP的CFET器件,尽管这些结果仅针对单个器件而非完整电路。三星成功的关键在于能够对堆叠式pFET和nFET器件的源极和漏极进行电气隔离,合格器件的良率提高了80%。与英特尔一样,三星也采用了背面接触技术,但在每个成对器件中只使用了一个纳米片。

在IEDM 2024上,IBM研究院和三星联合展示了一种名为“单片堆叠式场效应晶体管”的器件,该器件采用阶梯式沟道设计以降低堆叠高度和工艺难度。

CFET:延续摩尔定律的必经之路

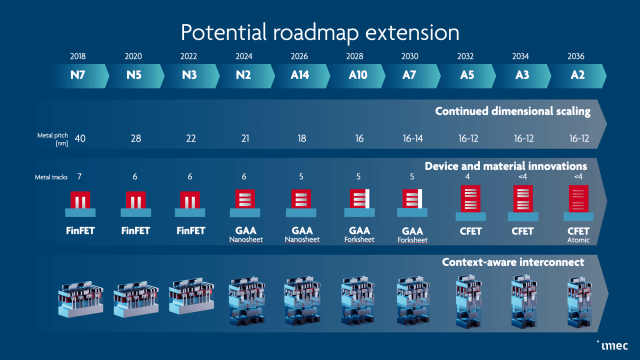

业界专家认为,在CFET时代到来之前,将经历数代纳米片架构,并可能面临CMOS元件尺寸缩小停滞的问题。据最早开发CFET概念的imec预测,尺寸缩小停滞将迫使高性能计算芯片的设计人员采用芯粒(Chiplet)和先进封装等方案进行功能拆分与集成。

imec认为,仅靠纳米片实现CMOS器件微缩非常困难。CFET是真正继续缩小器件尺寸、推动先进制程工艺发展的关键。它可以与其他技术(如芯粒和先进封装)相结合,共同提升芯片性能。imec预计,到2032年左右,CFET器件架构将超越1纳米节点。

挑战与展望

尽管CFET有望恢复工艺尺寸缩小的步伐,但在实现商业化之前,仍有多个障碍需要克服。例如,如何为更高的CFET三维结构高效供电是一个首要难题。结构纵横比的增加也给制造工艺带来了巨大挑战。

台积电也承认,CFET架构的“重大挑战”可能会导致工艺复杂性和成本增加。为了克服这些挑战,芯片制造商必须谨慎选择能够降低工艺复杂性的集成方案,并尽早开展EDA工具与设计流程的开发,为重大的设计变更做好准备。

总而言之,CFET作为延续摩尔定律的关键技术方向,其发展前景广阔,但走向成熟与大规模应用仍需时间。