随着半导体工艺进入3纳米节点,传统依靠尺寸微缩的发展路径遇到了瓶颈。当晶体管鳍片间距缩小至30纳米以下,甚至减少到单鳍结构时,工艺的波动性增大,驱动电流也变得不足。为应对这些挑战,台积电在2022年6月的北美技术论坛上正式推出了创新性的FinFlex架构,并将其作为其3纳米制程技术的关键突破。这项技术首次允许芯片设计者根据模块需求,在同一颗芯片上混合使用三种不同的鳍式晶体管配置,从而实现性能、功耗与芯片面积(PPA)的精准平衡。

FinFlex的三种核心配置与设计灵活性

FinFlex技术的精髓在于提供了三种量身定制的鳍片配置方案,分别针对极致性能、均衡表现和超高能效进行优化。

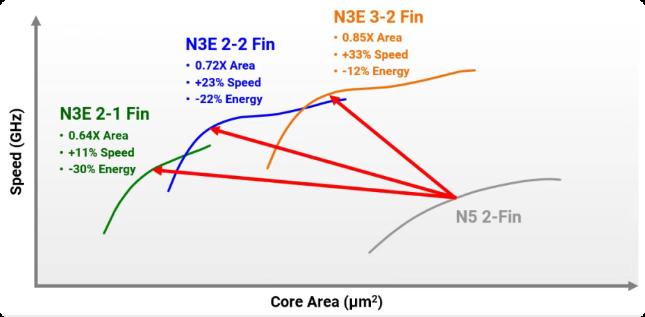

- 3-2鳍配置 (性能导向):采用3鳍NMOS和2鳍PMOS,能提供更高的驱动电流,非常适合CPU、GPU中的高性能核心。实测数据显示,相比前代工艺,它能带来高达33%的速度提升,同时芯片面积仅为5纳米工艺的0.85倍。

- 2-2鳍配置 (平衡导向):在性能、功耗和晶体管密度之间取得了最佳平衡,适用于中频操作的模块。它在实现23%速度提升的同时,功耗降低了22%,面积缩减至0.72倍。

- 2-1鳍配置 (能效导向):采用单鳍PMOS,可显著降低漏电流和动态功耗,专为移动SoC中的能效核心和待机电路设计。其功耗降低幅度高达30%,面积更是缩小到5纳米工艺的0.64倍。

这种前所未有的配置灵活性,使得现代采用异构集成理念的处理器(如大小核架构)能够为每一个功能模块选择最合适的晶体管结构,从而实现芯片级别的整体优化。

底层技术创新与协同优化

要实现FinFlex并达成相比5纳米工艺1.6倍的逻辑密度提升,离不开晶体管工程、互联技术和设计工具等多方面的协同创新。

- 晶体管工程:通过精细优化鳍片的宽度与三维轮廓,在缩减栅极长度的同时有效抑制短沟道效应,使FinFET架构在3纳米节点得以延续。特别对2-1鳍这类单鳍器件进行了工艺补偿,使其动态功耗相比双鳍器件降低了50%。

- 互联技术:台积电实现了业界最紧凑的23纳米金属间距,并引入了创新的铜衬垫技术与超低介电常数介质材料。这使得金属连线的电阻和电容降低了20%-30%,通孔电阻更是大幅降低了约60%,确保了信号传输的完整性。

- 设计工艺协同优化 (DTCO):台积电与EDA合作伙伴紧密协作,确保客户能够使用现有的设计工具集轻松实现混合鳍配置的设计。此外,还提供了跨度超过200mV的6种阈值电压选项,为设计人员提供了更精细的功耗与性能调节杠杆。

实测数据与可靠性验证

基于测试芯片的实测数据,充分验证了FinFlex技术的成熟度与可靠性。

- 高密度SRAM:面积为0.021μm²的6晶体管SRAM单元,在0.45V工作电压下静态噪声容限达到97mV,0.6V时提升至124mV,单元功能最低可稳定工作至0.3V。256Mb的高密度SRAM宏在0.5V低电压下仍保持完整的读写功能,满足移动设备待机功耗的严苛要求。

- 可靠性:SRAM宏通过了1000小时的高温工作寿命测试,逻辑测试芯片也完全满足高性能CPU对最低工作电压和功耗的规范。

- 晶体管性能:在相同功耗条件下,速度可提升18%;在相同速度条件下,功耗可降低34%。

产业应用与竞争格局

在产业应用端,FinFlex技术已成功实现商业化。苹果的A17 Pro和M3系列芯片是首批采用者,其中高性能核心使用3-2鳍配置,能效核心则采用2-1鳍配置。这项技术为芯片设计行业带来了范式转变,极大地提升了异构集成的自由度,允许设计人员像“挑选工具”一样为不同模块定制晶体管结构,从而缩短设计周期并增强产品差异化。

与竞争对手三星在3纳米节点转向全环绕栅极(GAA)架构的策略不同,台积电的FinFlex技术在逻辑密度、生产良率等方面展现了持续优势,不仅为FinFET架构成功续命,也为向下一代2纳米GAA纳米片架构的平稳过渡争取了宝贵时间。

展望未来,台积电已规划在2纳米工艺采用纳米片GAA架构,预计将在密度、性能与功耗上实现新的飞跃。FinFlex技术的成功实践,深刻证明了架构层面的创新与设计工艺协同优化在延续摩尔定律中的关键作用。随着5G、人工智能与高性能计算需求的爆炸式增长,FinFlex所提供的卓越设计灵活性,正推动整个行业的计算能效迈入新时代,并为后续更先进技术节点的开发积累了宝贵经验。 |