半导体产业正经历一场由消费电子向高效能运算(HPC) 驱动的深刻变革。在这场变革中,联发科总经理暨营运长陈冠州明确指出,公司正将硅光子与共同封装光学(CPO) 技术视为未来的核心战略投资方向,并已全力投入研发。

一、应用场景聚焦:攻克“XPU与XPU之间的连接”瓶颈

面对云端AI模型规模的指数级增长,数据中心内部数据传输的速率需求正以前所未有的速度激增。陈冠州指出,“由电转光”已是不可逆转的技术趋势。联发科在电互连领域已深耕多年,其SerDes技术目前正推进至200Gbps,预计到2026年将有400Gbps的IP方案问世。然而,业界共识是,400Gbps之后,传统的铜互连技术将面临物理极限,技术发展必须转向“光”的领域。

那么,硅光子的具体应用场景在哪里?陈冠州给出了清晰的答案:“目前焦点在于‘XPU与XPU之间的连接’”。 这成为联发科切入该领域最重要的突破口。他强调,CPO是确定的技术演进方向,通过将光引擎与运算芯片紧密封装在一起,能极大缩短信号传输距离,从而显著降低功耗、提升信号质量,这对于构建下一代高密度、高能效的AI数据中心至关重要。

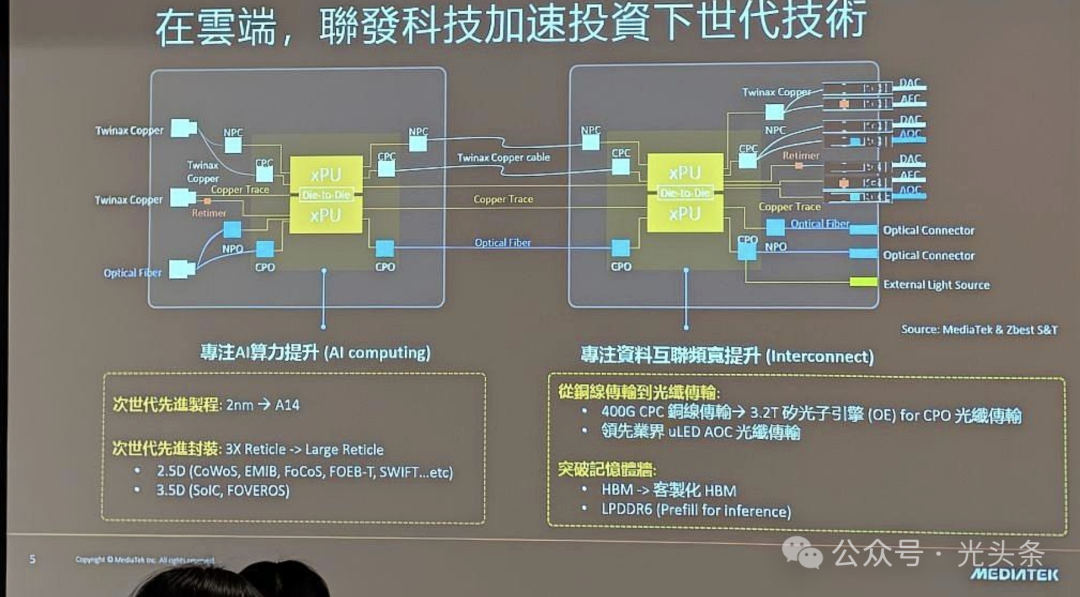

为了展示其技术路线图,联发科在近期披露了其面向云端的下一代技术投资架构。

根据架构图所示,联发科正从两个维度同步推进:其一是专注于AI算力提升,涉及2nm、A14等次世代先进制程,以及CoWoS、SoIC等先进封装技术;其二则是专注于资料互连带宽提升,核心路径正是从400G铜线传输向3.2T硅光子引擎(用于CPO)的光纤传输演进。

此外,联发科还预告了一项颇具前瞻性的技术展示:计划在2026年4月的OFC(美国光纤通讯展览会)上,展出基于Micro-LED技术实现的主动式光缆(AOC)解决方案,这被认为是其在光互连领域的又一重要布局。

二、携手台积电,攻坚硅光子整合工程挑战

硅光子技术的落地绝非易事,其核心挑战在于如何实现光集成电路(PIC)与电集成电路(EIC)的高效能、高可靠性的异质整合。芯片堆叠带来的电性干扰、散热等问题都是巨大的工程难题。

为此,联发科选择了与半导体制造巨头台积电进行深度绑定与合作。陈冠州透露,公司正利用台积电的COUPE(Compact Universal Photonic Engine)平台,共同实践并推进先进封装光学技术。这种紧密合作确保了从设计到制造环节的技术连贯性与可行性。

在技术路线上,联发科持开放态度,表示将根据客户产品的具体特性来协助设计方案,不会局限于单一技术选择。在备受关注的先进封装产能方面,陈冠州也给出了肯定的答复,称公司已确认能获得2026-2027年所需的关键CoWoS 产能。目前,其先进制程与封装的供应链核心仍是台积电,暂无新增其他主要合作伙伴的计划。

为了支撑上述前沿技术的研发,联发科已启动内部资源的调整,并将加大投资规模,同时面向全球(尤其是美国)招募HPC领域的顶尖人才。陈冠州预计,公司2026年在相关领域的投资将会有大幅增长。

尽管市场预测2026年手机业务可能面临挑战,但得益于数据中心、AI服务器等智能 & 数据 & 云 业务的强劲需求,联发科对整体运营前景保持信心。公司也表示会协助客户做好供应链的资源调配与风险规避。

总结:迈向以HPC为核心的全方位半导体领航者

陈冠州的阐述清晰地勾勒出联发科的战略转型路径:通过深耕SerDes、硅光子、CPO及先进封装等关键技术,公司旨在抢占未来AI数据中心基础设施的关键地位,并将由此产生的技术红利进一步延伸至边缘计算等领域。这一系列布局的最终目标,是帮助联发科逐渐摆脱对消费电子市场周期的过度依赖,转型成为以高效能运算(HPC)为核心的、技术驱动型的全方位半导体解决方案领航者。

对于关注半导体前沿技术、数据中心架构与AI算力发展的开发者与行业观察者而言,联发科在硅光子领域的全力投入,无疑是一个值得持续关注的重要产业信号。更多关于云计算、AI基础设施与前沿硬件的深度讨论,欢迎在云栈社区的技术板块中进行交流。 |