近日,英特尔发布了一则关于其“Unified Core”核心团队的招聘启事。随后,不少科技媒体在报道时添上了“Intel终于要放弃大小核”的猜测。然而,这真的会发生吗?结合现有的信息分析,可能性微乎其微。

综合多方爆料来看,英特尔提出的“Unified Cove”架构,其意图并非取消“大小核”设计。更可能的情况是,英特尔将放弃现有的Cove系列高性能核心(P-Core)架构,并在未来让P核心与能效核心(E-Core)都采用同源的、基于当前Atom产品线的核心架构。这意味着,“大小核”依然存在,甚至即使基于同源设计,只要它们在具体实现(如缓存大小、频率、执行单元规模)上存在显著差异,就依然可以被视为“异构”设计。从根本上说,要深入理解这一点,需要回归到现代CPU设计的底层逻辑。

单核与多核性能的博弈:鱼和熊掌?

一款处理器的性能可以大致拆解为单核性能和多核性能两部分。而多核性能的理论上限,又可以粗略地看作是“单核性能 × 核心数量”。

在理想情况下,芯片设计者只需专注于提升单核性能,然后尽力堆叠核心数量即可。然而,现实世界存在严格的物理约束,包括晶圆面积、晶体管预算和功耗限制。在这些约束下,提升单核性能(IPC和频率)往往意味着损害多核性能。

从“多核性能=单核性能×核心数目”这个公式可以推理出,在成本受限的情况下,提升单核IPC的代价往往是更大比例的核心数目缩减。单核心性能的提升并非遵循“一分投入、一分回报”的线性规则,往往需要数倍的投入才能获得一成的收益。

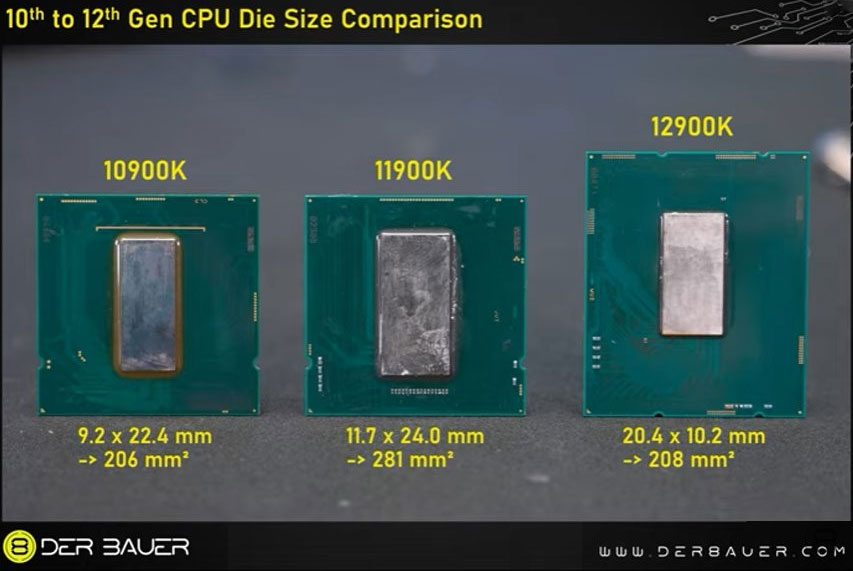

举例来说,一个核心若要提升20%的IPC,其所需的晶体管数量(面积)可能需要翻倍。那么,在总预算不变时,多核性能自然会下降。典型的例子是英特尔的第十一代酷睿Rocket Lake-S,其核心面积比上一代增加了约40%,核心数却从10核降至8核。虽然单核性能提升显著,但多核性能只是勉强持平。

因此,当单核与多核性能都面临提升压力时,如何分配资源就成为一个关键的博弈点。

但硬币的另一面是,单核性能提升的“低性价比”特性,反过来也能成为提升多核性能的突破口。用打造一个高性能核心所需资源的50%,去设计和制造一个规模更小、更精简的核心,其能产出的综合性能大概率会高于原大核的50%。

这正是英特尔自第十二代酷睿Alder Lake起,多核性能开始迅猛增长的根本原因。在其异构大小核设计中,一个包含4个能效核心(E-Core)的集群,其面积消耗约为一个性能核心(P-Core)的130%,却能提供接近200%的多核性能。

回到“Unified Cove”的话题,英特尔即便推出全新的架构,也无法从根本上解决单核性能投入产出比递减的物理规律。只要英特尔希望在有限的成本(面积、功耗)内,最大化产品的单核与多核综合性能,采用“异构大小核”设计就是一条高效且必然的路径。

为何“同构大小核”并非最优解?

前文反复强调了“异构大小核”的优势。很多人可能会问:英特尔不能效仿AMD,采用“同构大小核”设计吗?这个问题的核心在于,一个CPU核心的设计无法在所有目标上都做到极致。

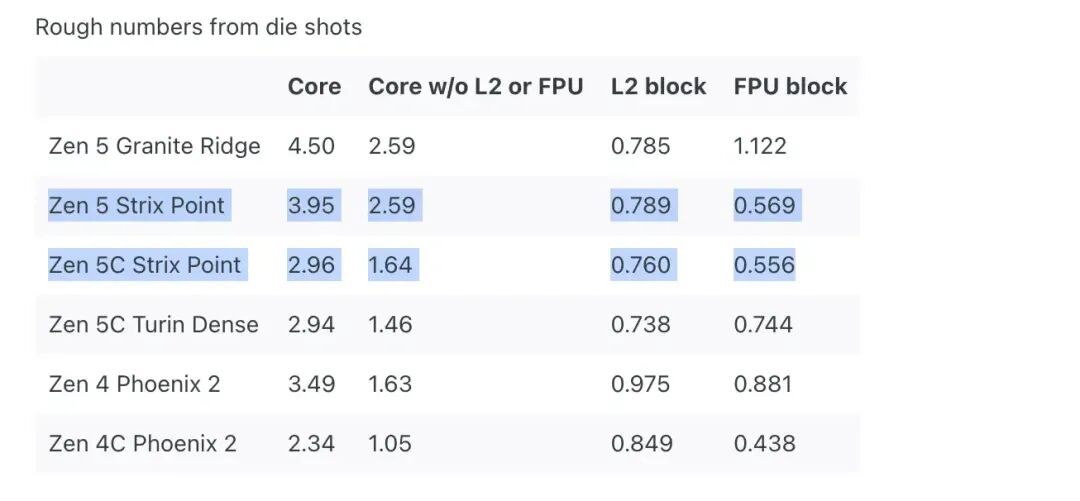

以AMD的Strix Point处理器为例(其Zen 5c核心本质上就是精简版的Zen 5)。Zen 5核心的面积(不含L3缓存)大约是Zen 5c的133%,但其峰值频率却是Zen 5c的157%。这意味着,在追求极限多核性能时,标准大核的面积效率(性能密度)反而可能更低。

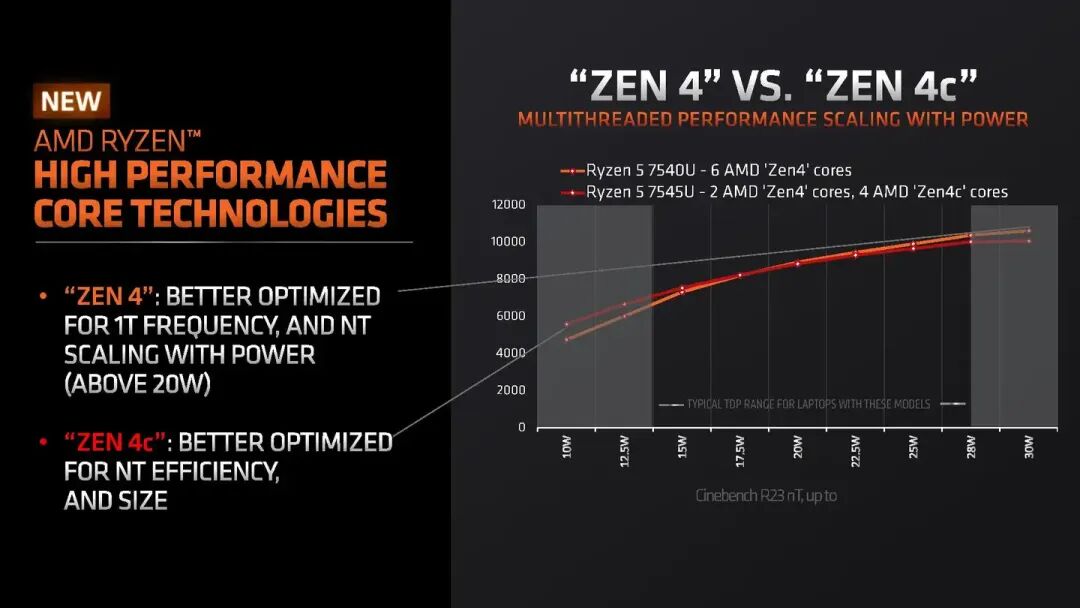

更值得注意的是,Zen 5c相对于Zen 5约33%的面积优势,是在未考虑相同容量L3缓存配比的前提下。若计入L3,密度优势将进一步缩小,甚至可能不如直接为Zen 5核心搭配更小的L3缓存来提升密度。同构大小核的优势,仅体现在特定的低功耗区间内,当标准大核因功耗墙限制而无法运行在高频时,才能显现出有限的价值。

此外,AMD这种“同构”小核心在高频段的能耗表现也存在问题。为了极大提升密度而设计的“Dense”核心,不仅牺牲了峰值频率,也牺牲了高功耗区间的能效。而在低功耗区间,其能效提升也相当有限,因为晶体管总量并未大幅减少。简而言之,同构大小核(或称密度优化核心)的主要价值,是在一定条件下,有限地提升特定低功耗场景下的多核性能密度。一旦脱离这个狭窄的功耗范围,其性能密度优势就可能丧失,甚至不如异构设计带来的提升显著。

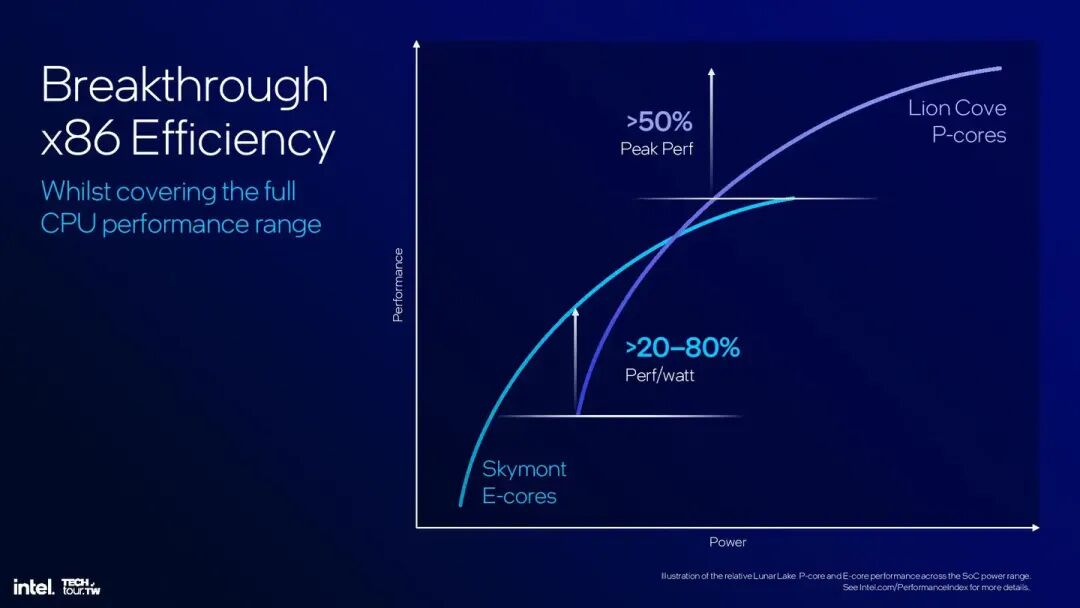

原生异构小核心的核心优势,在于其拥有与大核心截然不同的能耗曲线。由于规模更小,在极低功耗下,其能效比会显著优于大核心;反之,在较高功耗下,其能效比则迅速劣化。在大小核系统中,小核心并不需要承担与大核心同等功耗的任务。

以英特尔的设计为例,一个P-Core的面积大约等于三个E-Core的面积。那么,我们需要比较的就是:一个P-Core在全功耗下运行,与三个E-Core在各自1/3功耗下运行时,哪个组合能提供更高的多核性能。

仍以上图为例进行简化分析:假设三个Skymont(E-Core)的面积等于一个Lion Cove(P-Core)。当Lion Cove输出其峰值性能后(假设为100%性能点),我们找到Skymont曲线在1/3功耗点(对应于单个E-Core的功耗)对应的性能。然后将三个E-Core的性能相加,再计算达到该总性能所需的等效总功耗。通过这种估算可以发现,同面积的三个Skymont核心在输出与大核相近的多核性能时,所需功耗可能仅为一个Lion Cove核心的50%-60%,多核能效比几乎翻倍。

因此,原生异构的小核心在多核性能密度、多核能效比以及低负载能耗比方面都具有显著优势,远胜于同构设计。

Unified Cove 将如何演进“大小核”?

综上所述,英特尔在经历了数代产品的迭代,初步解决了计算机架构中最棘手的异构调度难题后,不太可能突然放弃已被证明高效的技术路线。“Unified Cove”更可能代表一种架构层面的统一与简化——即P核与E核基于同一套基础指令集和微架构蓝图进行设计,但在具体实现上(如执行端口数量、缓存层级与大小、频率与电压曲线等)进行深度定制,从而继续保持“异构”的高效特性。

这既能降低不同核心系列的设计与验证成本,又能保留异构大小核在性能和能效上的综合优势。未来具体如何实现,让我们拭目以待。对于这类前沿技术的深入探讨,也欢迎在云栈社区的技术板块进行交流。