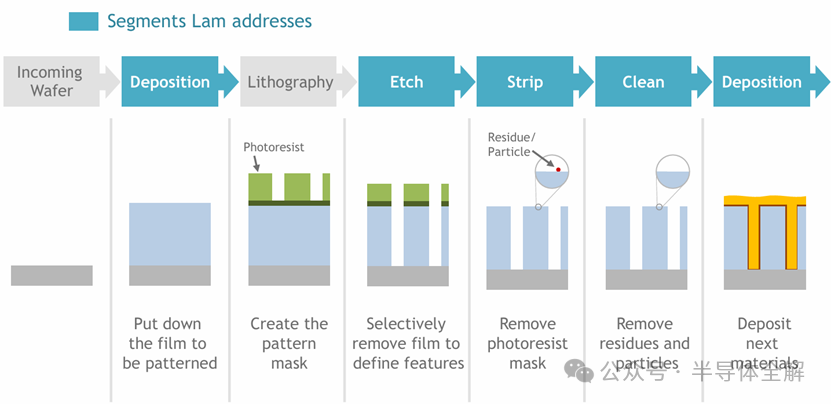

在芯片的制造流程中,光刻与刻蚀是定义电路图形的两大核心工序。典型的芯片制造过程主要包含多个循环的薄膜沉积、图形化与刻蚀步骤,其简化流程如下图所示。

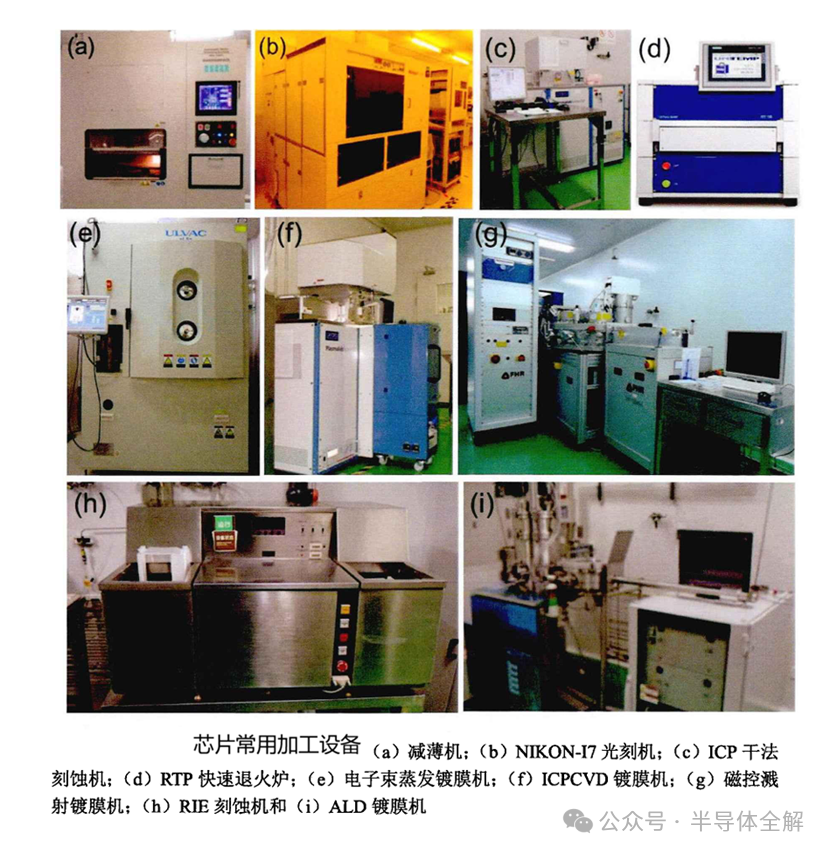

实现这些步骤需要一系列精密的加工设备。下图展示了芯片制造中常用的一些关键设备。

刻蚀技术本身可分为干法刻蚀和湿法刻蚀,两者各有其优缺点。随着芯片制程不断向更小节点迈进,干法刻蚀因其优异的各向异性(垂直刻蚀能力)而得到越来越广泛的应用。干法刻蚀本身又可以根据设备结构和原理的不同,细分为多种类型。

常见的干法刻蚀设备主要包括感应耦合等离子体刻蚀机 (Inductively Coupled Plasma, ICP)、反应离子刻蚀机 (Reactive Ion Etching, RIE) 和离子束刻蚀机 (Ion Beam Etching, IBE)。

依据刻蚀气体和反应原理的区别,这些设备被用于刻蚀不同的材料,例如 GaN、SiO₂、Si₃N₄ 以及各种金属材料。

ICP干法刻蚀介绍

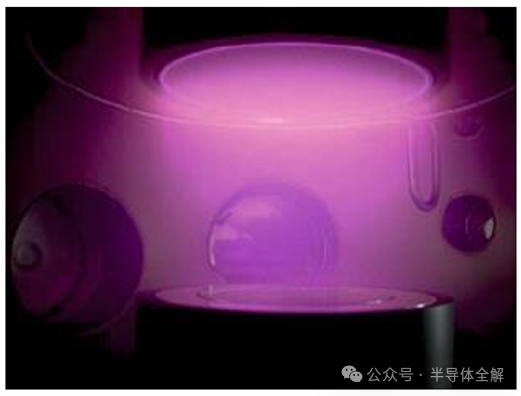

ICP刻蚀的基本原理是:ICP射频电源产生的射频信号输出到耦合线圈,使通入的刻蚀气体经过耦合后辉光放电,形成高密度等离子体。在另一个独立的RF射频偏置单元作用下,等离子体中的离子获得垂直方向上的能量,轰击样品表面,发生物理溅射和化学反应,从而实现刻蚀,反应生成的挥发性产物则由真空系统抽走。

进行ICP刻蚀时,常用的刻蚀气体包括 BCl₃、Cl₂、Ar、O₂、N₂ 和 CH₄ 等。

例如,刻蚀GaN基材料时,常使用含Cl的BCl₃、Cl₂气体。这主要是为了增大化学刻蚀的比例,从而减小高能离子物理轰击对GaN材料表面造成的晶格损伤。

相比之下,RIE刻蚀设备常用的气体有 SF₆、CHF₃、O₂ 和 He,通常用于刻蚀SiO₂和Si₃N₄薄膜。其基本原理是利用射频作用产生F基等离子体,对材料同时进行物理和化学刻蚀,其中化学作用往往占主导。

IBE刻蚀设备则主要用于金属材料的刻蚀。其原理是将Ar气电离形成Ar离子,Ar离子在电场加速下高速轰击样品表面,通过纯物理作用使材料原子溅射脱落,并被真空系统抽走。IBE刻蚀是纯物理过程,具备极好的各向异性,但缺点是刻蚀速率通常较慢。

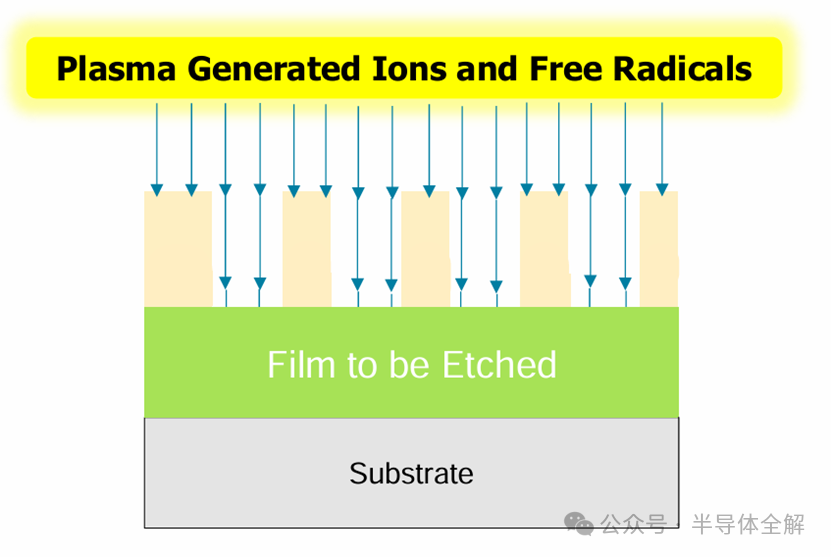

下图直观展示了等离子体中的活性粒子轰击薄膜表面进行刻蚀的过程。

反应离子干法刻蚀介绍

反应离子刻蚀 (RIE) 和感应耦合等离子体刻蚀 (ICP) 是两种核心的干法刻蚀技术。在实际工艺中,常先用RIE将光刻版上的图形转移到SiO₂掩膜上,再利用ICP的高效刻蚀能力来形成最终的台面结构。因此,理解等离子体刻蚀的基本原理以及这两种设备的特点至关重要。

(1)等离子体刻蚀原理

等离子体刻蚀是物理作用和化学作用协同的结果。

向反应腔内的气体施加高频电场,气体分子会被电离,形成由离子、电子、自由基和中性粒子组成的混合态,即等离子体。

在等离子体态下,气体分子被高度激发,产生大量高活性的自由电子和离子,这种状态非常适合进行精密的、各向异性的刻蚀。

等离子体中的活性粒子主要分为两类:

- 自由基:如 F、 Cl,它们是电中性但化学活性极强的粒子。它们吸附在材料表面,通过断裂化学键并重组形成挥发性产物(如 SiF₄)来实现化学刻蚀。

- 离子:带正电,在高能电场作用下被加速并垂直轰击带有负偏压的基板表面,通过物理碰撞使材料原子溅射出来。

化学刻蚀具有各向同性的特点,选择性高(即对目标材料刻蚀快,对掩膜材料刻蚀慢),但方向性差,容易产生横向钻蚀。物理刻蚀则具有高度的各向异性,方向性好(几乎垂直向下),但其选择性通常较低。

因此,在等离子体刻蚀过程中,通过精确调节腔压、ICP功率、RF偏置功率以及各气体的配比,可以控制自由基与离子的比例,从而实现化学刻蚀与物理刻蚀的协同优化,在保证高选择性的同时获得良好的各向异性轮廓。

(2)刻蚀设备与刻蚀步骤

在后续的工艺制备中,RIE主要用于将光刻胶的图形转移到SiO₂掩膜上。这是因为在刻蚀InP、InGaAs、InGaAsP等Ⅲ-Ⅴ族材料时,ICP刻蚀常需要较高温度(如180°C),而普通光刻胶在此高温下会变性并牢固地粘附在晶圆表面,难以去除。因此,必须使用耐高温且与目标材料刻蚀选择比高的SiO₂作为硬掩膜。

而ICP刻蚀则因其更高的刻蚀速率和优异的各向异性刻蚀效果,成为刻蚀Ⅲ-Ⅴ族化合物半导体材料的首选。

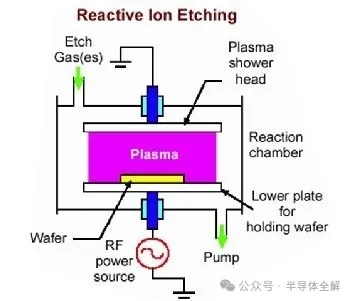

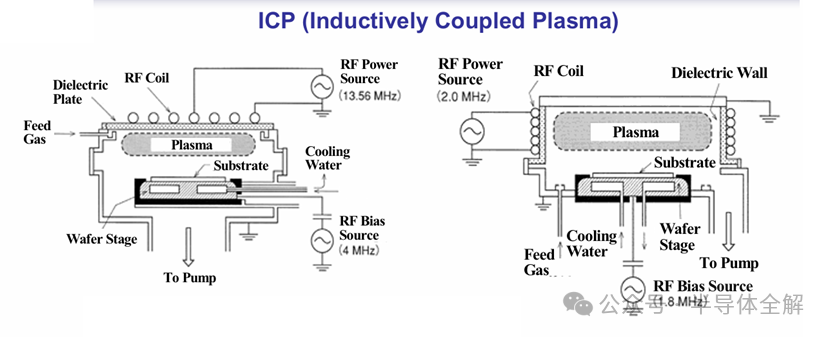

RIE与ICP设备的核心区别在于其结构设计,下图清晰地展示了这一点。

RIE设备通常只有一个位于刻蚀腔体下方的射频 (RF) 电源。这个RF电源既用于产生和维持等离子体,也用于在晶圆台(下电极)上产生直流自偏压,从而引导离子垂直轰击晶圆表面。

ICP设备则有两个独立的射频源:

- ICP源:位于腔体上方,由环形线圈组成,通过电感耦合方式高效电离气体,产生高密度的等离子体。

- RF偏置源:位于晶圆台下,主要用于控制离子轰击基片的能量。

这种设计实现了对等离子体密度(由ICP源控制)和离子轰击能量(由RF偏置源控制)的相对独立调控,工艺灵活性大大提高。

干法刻蚀工艺步骤

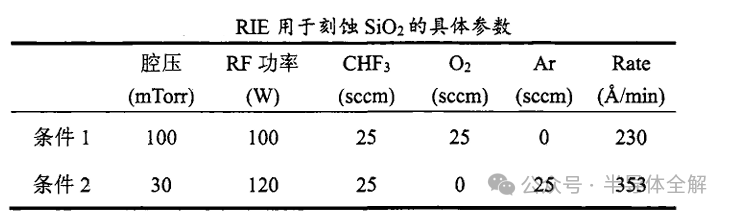

(1)RIE刻蚀SiO₂的参数与步骤

刻蚀SiO₂主要使用CHF₃与O₂组合或CHF₃与Ar组合的气体配方。具体刻蚀参数可参考下表。

从上表可以看出,条件2对SiO₂的刻蚀速率(353 Å/min)快于条件1(230 Å/min),并且与AZ5214E光刻胶的刻蚀选择比能达到约3:1,而条件1的选择比仅为1:1。

然而,使用CHF₃与Ar的组合进行刻蚀后,由于化学作用较强,容易在晶圆表面生成较多的氟碳聚合物残留,可能影响后续工艺。因此,在光刻胶厚度足够的情况下,通常会优先选用条件1的工艺参数。

使用RIE刻蚀SiO₂的标准步骤如下:

- 将晶圆放入反应腔室。

- 对腔室进行抽真空,以排除残留空气的污染。

- 运行刻蚀程序:首先按设定比例通入刻蚀气体(如CHF₃)和辅助气体(如O₂或Ar)。

- 启动RF射频电源,气体电离形成等离子体,开始计时刻蚀。

- 刻蚀结束后,关闭气体和RF电源,进行腔体清洗和晶圆取出。

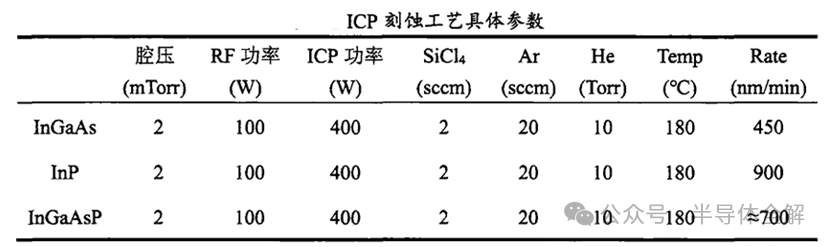

(2)ICP刻蚀Ⅲ-Ⅴ族材料的参数与步骤

ICP刻蚀光电探测器常用的InP、InGaAs、InGaAsP等材料时,常采用高温刻蚀工艺(例如180°C),并使用含氯(Cl)的气体进行刻蚀。

通常以SiCl₄作为主要的刻蚀气体。但在化学刻蚀过程中,容易产生难挥发的InClx等聚合物,沉积在表面会阻碍刻蚀的继续进行。因此,工艺中会通入一定流量的N₂、Ar等惰性气体,以增加腔体内的离子密度,增强物理轰击作用,从而帮助清除表面聚合物,获得更干净的刻蚀侧壁。

下表展示了一种典型的ICP刻蚀Ⅲ-Ⅴ族材料的工艺条件:

(3)典型刻蚀步骤详解

以使用SiO₂作为掩膜进行ICP台面刻蚀为例,典型步骤如下:

- 预处理:在已完成SiO₂掩膜图形化的晶圆背面涂抹少量导热脂(如栗油),以增强刻蚀过程中的散热效果,但需严格控制用量,避免污染。

- 装片与传送:将晶圆放置在4英寸的硅承载盘上,一同放入设备的Load Lock(装卸室)。关闭Load Lock后,对其进行抽真空。

- 进片与稳定:真空达到要求后,晶圆被自动传送至主反应腔室,并被压板固定。主反应腔室进一步抽至高真空,然后通入工艺气体(如SiCl₄、Ar等),等待气体流量稳定。

- 启动与刻蚀:通入用于背冷散热的氦气(He),待其流量稳定、射频功率稳定且反向功率降至安全范围后,启动ICP源和RF偏置源。气体起辉产生等离子体,按照预设的时间进行刻蚀。

- 清洗与取片:刻蚀程序结束后,反应腔室会进行多次“抽真空-充气”的清洗循环,以尽可能将反应副产物排入尾气处理系统。随后晶圆被传送回Load Lock腔。Load Lock腔经过清洗和充气,恢复至大气压后,即可开腔取出晶圆。

在工艺调试阶段,通常会先使用陪片(Test Wafer)进行刻蚀速率测试。正式刻蚀时,往往分两步进行:第一步先刻蚀目标深度的80%左右,然后测量实际台阶高度,计算材料与掩膜的实际刻蚀选择比;再根据计算结果进行第二步刻蚀,最终将刻蚀深度的误差控制在10%以内。

对于这些底层制造原理的深入探讨和更多技术细节的交流,可以在 云栈社区 这样的开发者社区中找到志同道合的伙伴。

参考文献:

(1) 董晓雯. 光载无线系统中高速高饱和光电探测器及光互连收发一体芯片研究[D].

(2) 闫书萌. NPN型GaN异质结双极型晶体管的研究[D].

(3) 杨鹏. 双层堆叠的三维相变存储器刻蚀工艺研究[D].

(4) 雷雨璋. 先进等离子体干法刻蚀工艺形貌效应仿真与验证研究[D].

(5) 宋昊宇. 基于CF₄等离子体二维流体模型的ICP刻蚀设备结构优化与工艺参数分析[D].