本文旨在系统性地介绍以太网的 MAC(Media Access Control) 和 PHY(Physical Layer) 这两个核心组件,以及连接它们的关键接口——MII(Media Independent Interface)及其各种衍生版本,包括GMII、SGMII、RMII、RGMII等。

简介

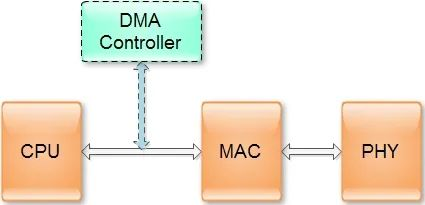

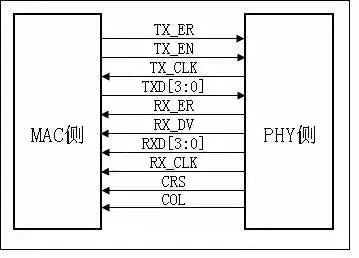

从硬件架构来看,一块以太网接口电路主要由MAC控制器和PHY物理层接口两大部分构成。其基本关系如下图所示:

注:DMA控制器通常集成在CPU内部,上图中用虚线表示其可能参与网口数据传输。

在实际芯片设计中,MAC、PHY和CPU的集成方式并非一成不变。由于PHY包含大量模拟电路,而MAC是纯数字电路,考虑到芯片面积和混合信号设计的复杂性,常见的方案有以下几种:

- CPU集成MAC与PHY:这种高度集成的方案目前较为少见。

- CPU集成MAC,外挂独立PHY芯片:这是非常常见的架构,尤其在微控制器(MCU)中。

- CPU不集成MAC与PHY,使用独立的MAC+PHY集成芯片:同样是一种主流方案。

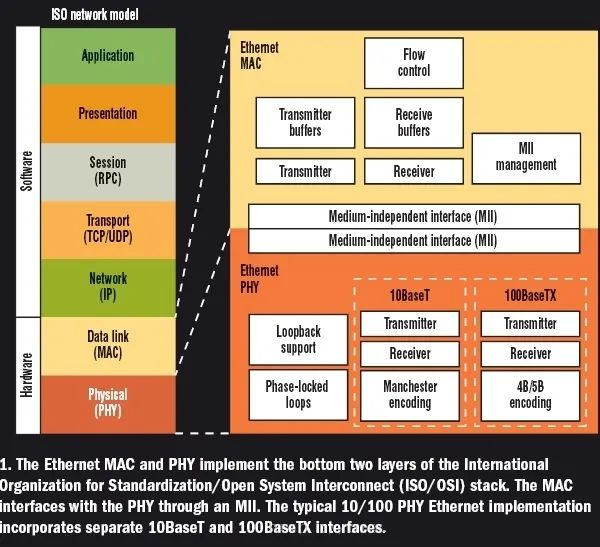

从网络协议栈的角度看,MAC和PHY分别工作在OSI七层模型的数据链路层和物理层。

什么是MAC?

MAC(媒体访问控制子层协议) 具有双重含义:它既是一个硬件控制器,也是一套通信协议。该协议位于数据链路层的下半部分,主要负责控制与连接物理层的物理介质。

MAC控制器的主要功能如下:

- 发送数据时:判断信道状态,在数据帧上添加目标/源MAC地址、帧类型等控制信息,并组装成规定格式(64-1518字节)发送至PHY。

- 接收数据时:校验帧是否传输错误,无误则剥离控制信息,将数据上交至LLC(逻辑链路控制)层。

MAC地址的获取依赖于ARP协议。首次与目标IP通信时,主机会发送广播ARP请求包,目标主机回应其MAC地址,此后双方便可在数据链路层直接寻址。IP与MAC的映射关系存储在本地ARP表中。

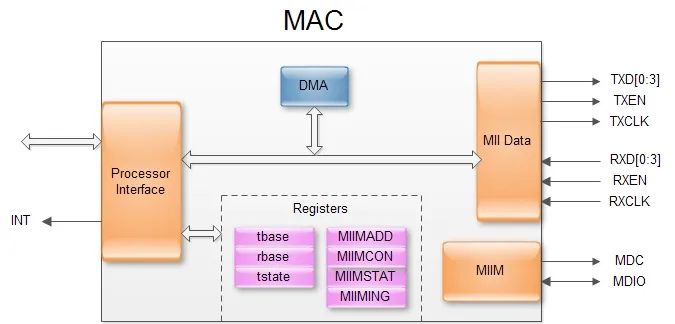

MAC控制器一端通过PCI等总线与主机相连,另一端则通过MII接口与PHY芯片连接。

什么是PHY?

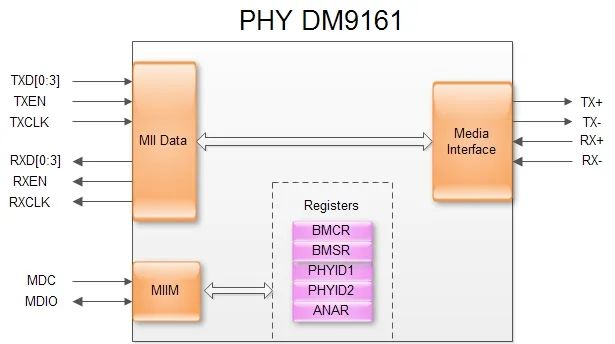

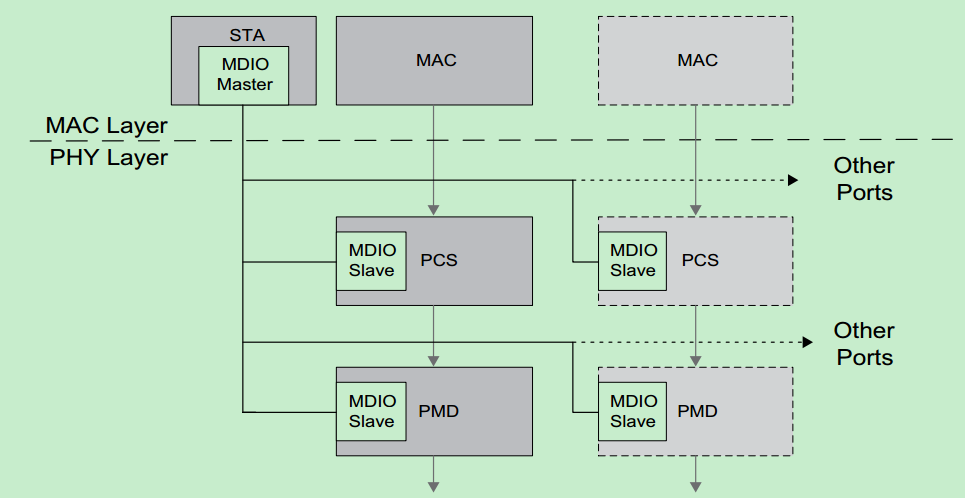

PHY(物理层接口收发器) 是实现OSI模型物理层的标准模块。它由IEEE 802.3规范定义,STA(管理实体,通常为MAC或CPU)通过SMI(串行管理接口) 读写PHY内部的寄存器,从而管理和控制其工作状态(如速率、双工模式等)。

一个PHY芯片内部通常包含MII/GMII接口子层、物理编码子层(PCS)、物理介质附加子层(PMA)和物理介质相关子层(PMD)等。

什么是MII?

MII(媒体独立接口) 是连接MAC与PHY的标准并行接口,支持10Mbps和100Mbps速率。其数据位宽为4位。

MII接口主要包含两部分:

- 数据接口:负责数据的发送与接收。

- 管理接口(MDIO):负责PHY的寄存器配置与状态读取。

主要信号线说明:

- TXD[3:0]/RXD[3:0]:4位发送/接收数据总线。

- TX_CLK/RX_CLK:发送/接收参考时钟(100M时为25MHz)。

- TX_EN/RX_DV:发送使能/接收数据有效指示。

- TX_ER/RX_ER:发送/接收错误指示。

- MDC/MDIO:管理接口的时钟与双向数据线。

MII接口的缺点是信号线数量较多(共16根),在需要多端口的交换机设计中会占用大量引脚,因此衍生出了多种简化版本。

什么是RMII?

RMII(简化媒体独立接口) 在MII的基础上将数据线从4位减少到2位。为了实现相同的吞吐量,其时钟频率需要加倍(100M时为50MHz)。RMII接口信号线少,更节省引脚资源。

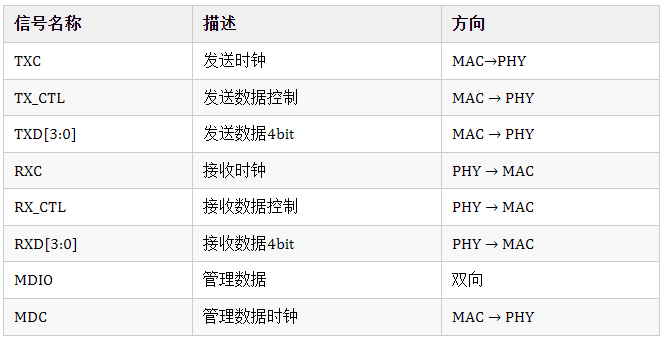

什么是GMII与RGMII?

- GMII(千兆媒体独立接口):用于千兆以太网,数据位宽扩展至8位,时钟频率为125MHz,同时向下兼容MII。

- RGMII(精简千兆媒体独立接口):GMII的简化版。它将数据线从8位减至4位,在125MHz时钟的上升沿和下降沿都传输数据,从而实现千兆速率。控制信号TX_CTL和RX_CTL分别复用了TX_EN/TX_ER和RX_DV/RX_ER。这使得RGMII在性能和引脚数量间取得了良好平衡,成为千兆应用中非常流行的接口。

什么是SMI(MDIO)?

SMI,通常直接称为MDIO接口,是一个两线制(MDC时钟线和MDIO双向数据线)的串行管理接口。MAC(作为STA)通过它读写PHY(作为MMD)的内部寄存器,实现链路状态查询(如连接速率、是否联通)和功能配置(如开启流控、设置工作模式)。这是管理PHY芯片的核心通道。

常见问题解答(Q&A)

1. 网卡的MAC和PHY之间是什么关系?

网卡工作在物理层和数据链路层。PHY对应物理层,负责数模转换、编码解码等;MAC对应数据链路层下半部分,负责帧封装、寻址、差错校验等。二者通过标准接口(如MII)协同工作,共同完成网络数据的收发。

2. MAC和PHY之间如何通信?

它们通过两个通道协同工作:

- 数据通道:通过MII/GMII/RGMII等标准接口传输网络数据帧。

- 管理通道:通过SMI(MDIO) 接口,MAC读取PHY的状态寄存器以获取链路信息,或写入控制寄存器以配置PHY的工作模式。

这种基于标准接口和寄存器的设计,使得不同厂商的MAC和PHY芯片能够互联互通,这在网络协议和硬件设计中被广泛遵循。 |