不少朋友在组装新电脑时可能会发现一个现象:以前的老机器插满4根DDR3内存条似乎稳稳当当,但到了DDR4时代,插4根内存主板自检时间就明显变长,而到了DDR5时代,插满4根有时甚至会出现蓝屏或死机。

这背后究竟是为什么呢?核心原因可以归结为两点:一是主板内存的布线拓扑结构发生了根本性改变;二是内存频率的飙升与日益复杂的信号环境,使得物理布线的局限性被放大,系统对信号干扰更为敏感。

我们可以用一个简单的比喻来理解:DDR3内存频率较低,例如1600MHz,就像一支车速较慢的车队(通信信号)。即使道路(主板布线)有些弯曲或稍长,车队也能较好地保持队形,准时到达目的地。而DDR5内存频率动辄达到8000MHz或更高,这无疑是“速度与激情”级别的竞赛。此时,路面上的一颗小石子(信号损耗或干扰),或者一个设计不佳的岔路口(拓扑结构),都可能导致严重的通信问题,进而引发系统不稳定。

具体来说,导致DDR5插满4根稳定性下降的物理和技术原因主要有以下几个方面:

1. 频率越高,信号完整性挑战越大

随着频率的几何级数增长,电信号在PCB走线上传输时更易发生衰减和畸变。这意味着系统允许的时序容错窗口(Timing Margin)变得极其狭窄,任何微小的信号质量问题都可能导致数据传输出错。

2. 内存控制器负载与子通道管理压力剧增

插满4根内存对内存控制器的驱动能力和管理能力提出了极高要求。信号的纯净度和各通道间的时序同步必须做到近乎完美。

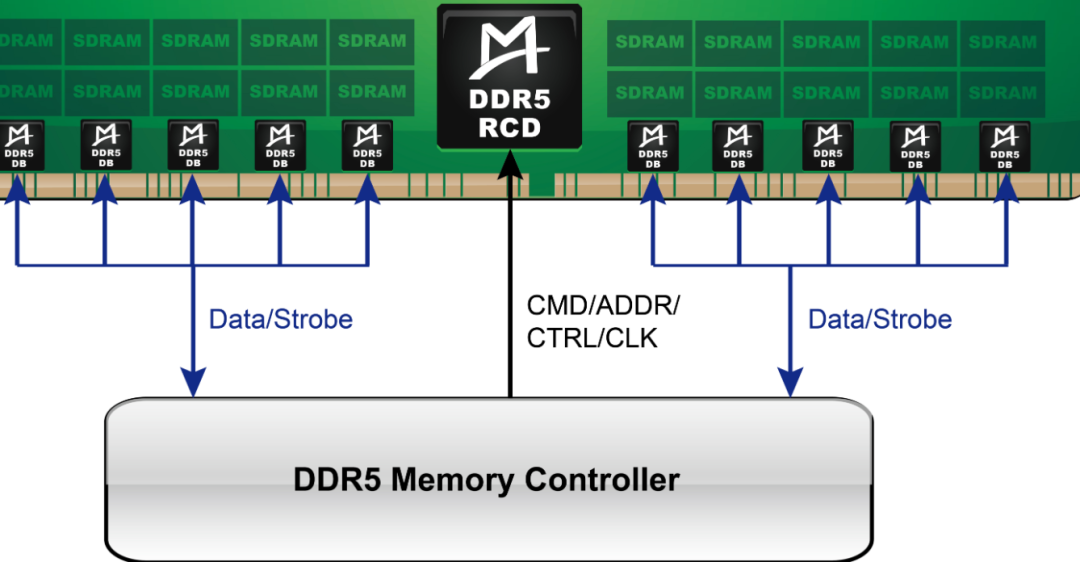

- DDR5内存内部将传统的64位数据通道拆分为两个独立的32位子通道,旨在提升并发效率。因此,仅插两根DDR5内存,内存控制器实际上就需要管理4个子通道。

- 当插满四根DDR5内存时,内存控制器需要同时管理和同步8个子通道的高频信号。这对于控制器本身的“体质”和主板供电设计都是巨大的考验。

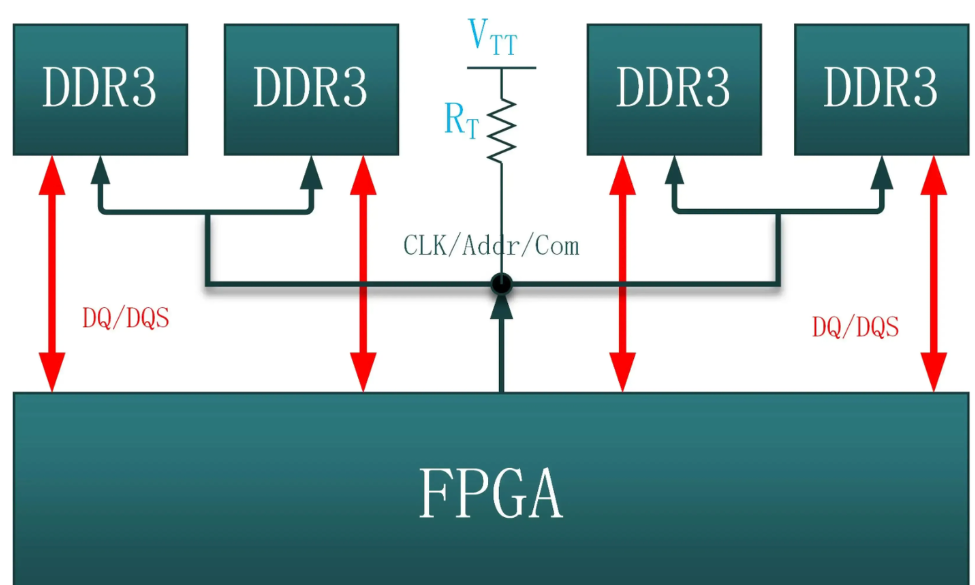

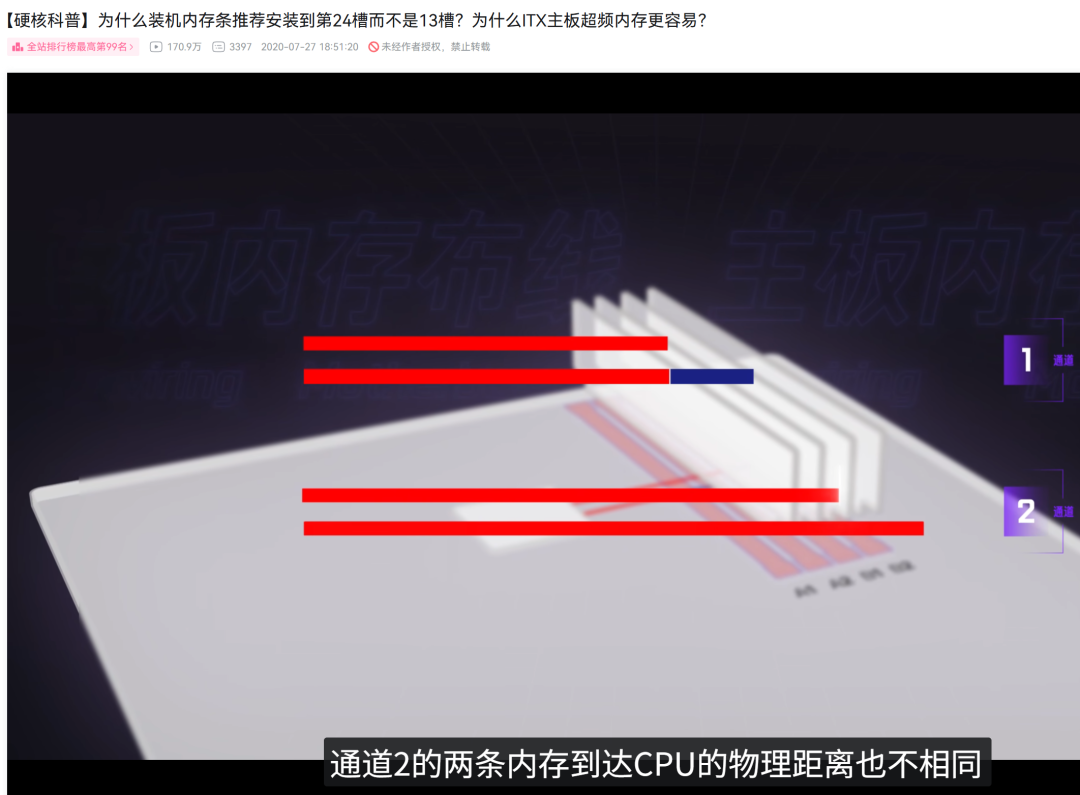

3. 菊花链拓扑结构带来的信号衰减

现代主板为了追求更高频率的支持,普遍从DDR3时代的T型拓扑转向了菊花链拓扑。在菊花链布局下,信号从CPU出发,依次经过第一个内存插槽(A2/B2),再到第二个内存插槽(A1/B1)。这导致信号到达远端插槽(A1/B1)时,质量会出现明显下降。当四个插槽全部插满时,所有内存模组都需要通过这条长且信号质量不均衡的路径进行通信,协同稳定工作的难度自然大大增加。

关于T型拓扑与菊花链拓扑的详细工作原理与差异,有非常专业的视频进行过图解分析,下图便源于此类内容的示意图,清晰地展示了布线差异对信号路径的影响。

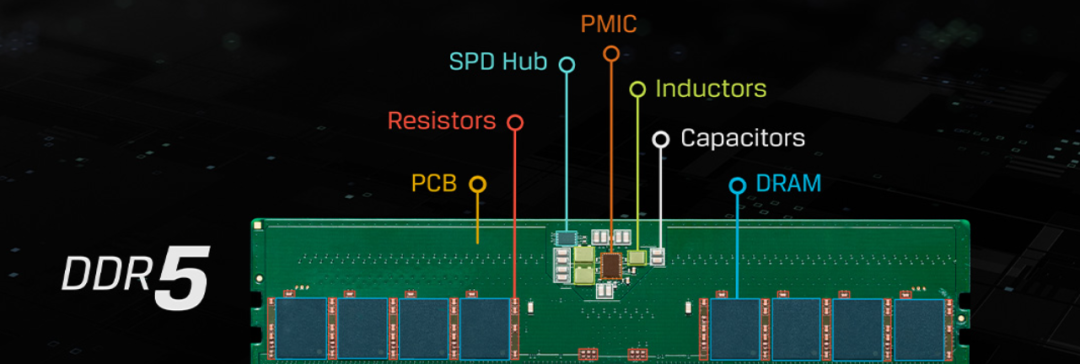

4. 独立的PMIC可能引入电源噪声

DDR5内存条的另一大革新是在模组上集成了PMIC(电源管理芯片),用于独立管理内存电压。这带来了更精细的电压调节能力,但也带来了新的挑战。当四根DDR5内存同时高负荷工作时,四个独立的PMIC之间可能产生细微的、不同步的电压波动或噪声,这些噪声叠加后可能干扰到本就脆弱的高频信号完整性,从而增加系统的不稳定因素。

简单总结一下,在DDR5时代,由于主板布线转向了菊花链拓扑、内存频率极高、内部通道拆分以及集成了独立电源管理芯片等多重因素叠加,使得插满4根内存对系统稳定性的要求变得极为苛刻。

因此,对于大多数追求极致性能和高稳定性的用户(尤其是超频玩家),目前业界普遍推荐使用两根内存组成双通道的模式。如果确实有工作负载需要超大内存容量,且对内存带宽性能不敏感,那么选择较低频率(如JEDEC标准的4800MHz)的DDR5内存,其插满4根的稳定性会相对更好。

理解这些硬件层面的底层逻辑,能帮助我们在装机时做出更合理的选择,避免潜在的稳定性问题。如果你对这类计算机硬件的深度原理感兴趣,欢迎在云栈社区与其他技术爱好者一起交流探讨。 |