在电源输入前端加入防反接保护,是许多电子硬件设计中不可忽视的一环。传统方案通常直接串联一个普通二极管,利用其正向导电特性来实现保护。然而,这种方法会引入一个明显的缺点:二极管本身的正向导通压降(通常为0.3V至0.7V)会导致负载端电压低于电源电压,造成不必要的功耗损失,在低电压或低功耗应用中尤为致命。

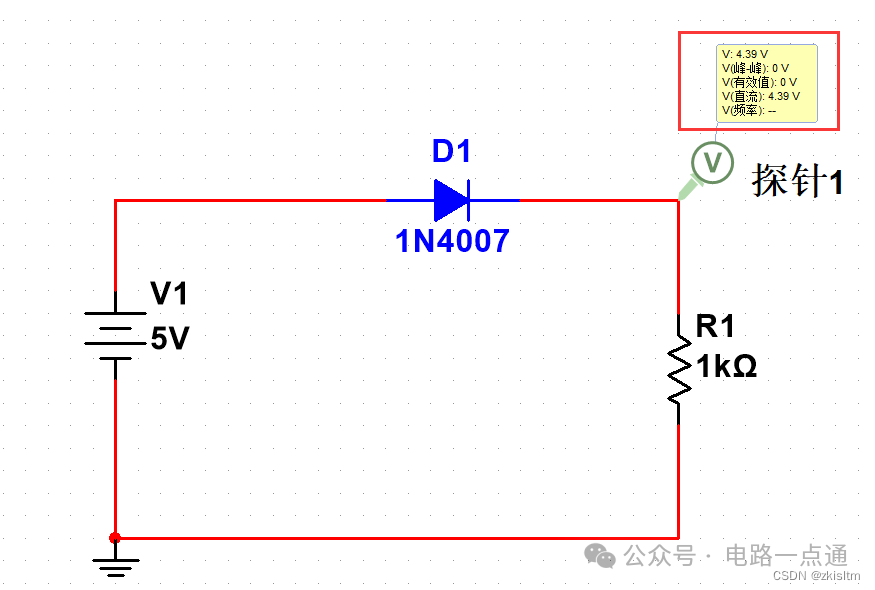

例如,在一个简单的5V电源串联二极管给1kΩ电阻供电的电路中,实测电阻两端的电压会下降约0.61V。

为了解决压降问题,本文将介绍一种基于背靠背PMOS管构成的“理想二极管”电路。该方案不仅能有效防止电源反接和电流倒灌,更能显著降低导通压降,非常适合对效率和电压精度有要求的电源管理应用。

电路原理与设计

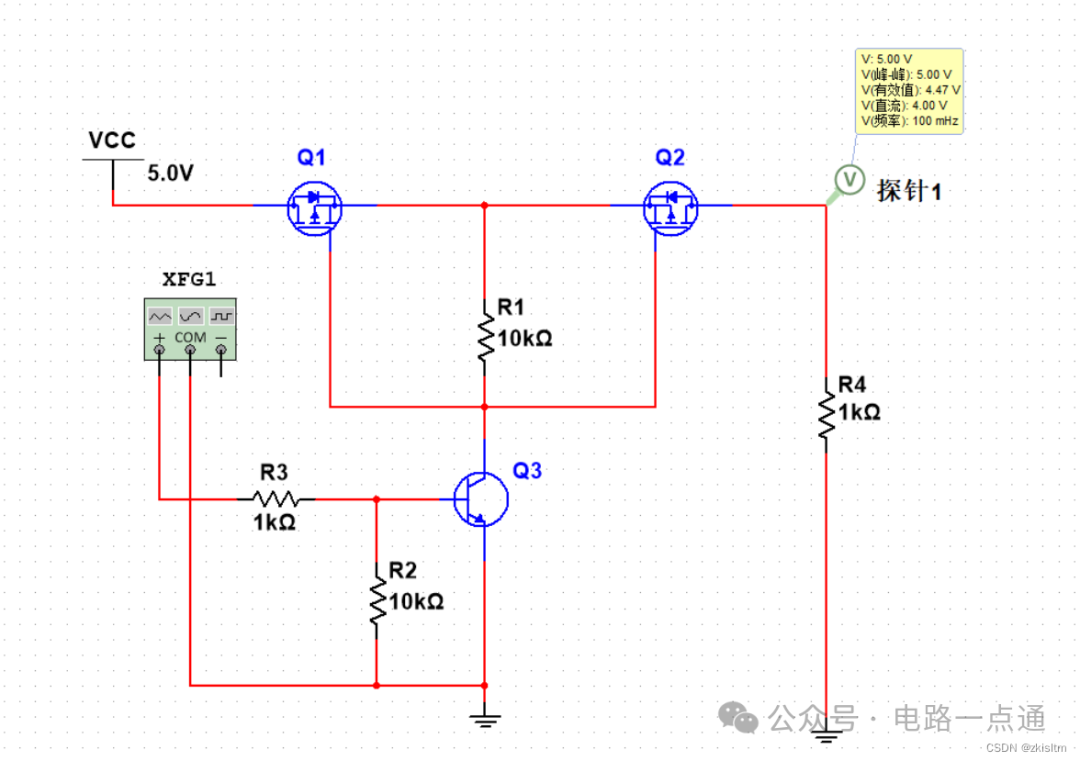

核心电路如下图所示,由两个PMOS管(Q1, Q2)背靠背串联,并通过一个NPN三极管(Q3)来控制它们的导通与关断。图中使用一个0.1Hz的方波信号源来模拟MCU的IO控制电平。

工作原理分析:

- 正常导通状态:

当控制信号(Q3基极)为高电平时,三极管Q3导通。此时,Q1和Q2的栅极(G)电位被拉低至接近0V。对于PMOS管而言,当源极(S)电压高于栅极(G)电压,即Vgs < 0时,管子导通。

- 首先,Q1通过其内部的体二极管形成通路,使其源极电位升高,满足Vgs<0的条件而率先导通。

- Q1导通后,其漏极(D)电压升高,这使得Q2的源极(S)电压也高于其栅极(G)电压(此时栅极仍为低电平),因此Q2也随之导通。

- 最终,两个PMOS管均完全导通,负载端获得几乎与电源VCC(5V)相等的电压,压损极小。下图的仿真显示了负载端电压为5.00V。

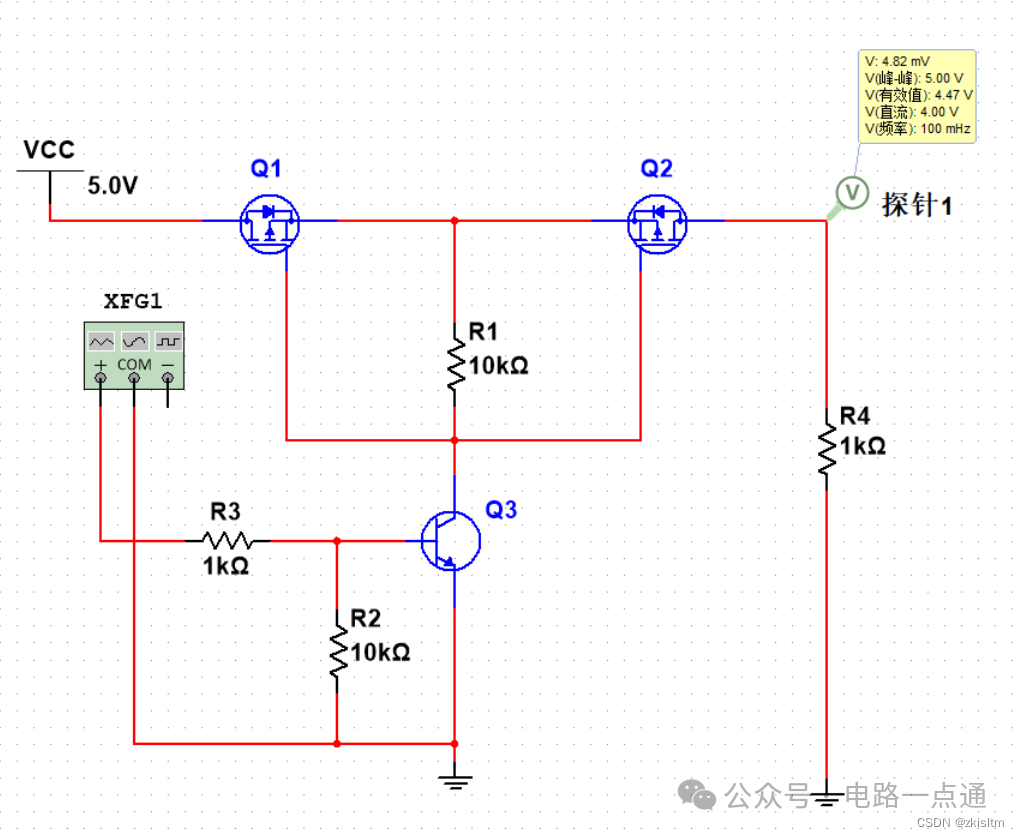

- 关断与保护状态:

当控制信号为低电平时,三极管Q3截止。Q1和Q2的栅极通过上拉电阻恢复到高电位,Vgs ≈ 0,不满足导通条件,因此两个MOS管均关断。

- 同时,由于Q1和Q2是“背靠背”连接,它们内部的体二极管方向相反、串联在一起。这意味着无论从输入端到输出端,还是从输出端到输入端,电流都无法通过这两个反向串联的二极管。

- 因此,该电路可以同时实现电源防反接和防止负载端电流倒灌的功能。仿真中,此时负载端电压仅为4.82mV,接近0V。

方案优缺点

优点:

- 极低的导通压降:PMOS管在导通时的导通电阻(Rds_on)很小,因此其上的压降远小于普通二极管,效率更高。

- 双重保护:有效防止电源反接,并能阻断电流从负载端(如电池、大容量电容)倒灌回电源。

- 可控性强:通过一个IO口即可控制整个电源路径的通断,便于实现软开关或电源时序管理。

缺点:

- 需要控制信号:必须占用一个微控制器或逻辑电路的IO口来提供控制电平,无法像无源二极管那样即插即用。

- 电路稍复杂:相比单个二极管,需要额外的三极管和电阻等外围元件。

总结与拓展

这种背靠背PMOS理想二极管电路,在需要高效、可控电源路径的硬件设计中是一个经典且实用的选择。它完美解决了传统二极管方案的压降痛点,特别适用于电池供电设备、精密模拟电路或需要对上下电进行严格管理的系统。在实际选用PMOS管时,需要根据电路的工作电流、电压来选择合适的器件,并确保其Vgs阈值电压与你的控制逻辑兼容。如果你想深入讨论更多关于电子设计的实战技巧,欢迎在技术社区交流。 |