做硬件设计的工程师,常常面临既要性能达标又要控制成本的双重压力。特别是在高速板卡设计中,阻抗匹配是绕不开的技术门槛,但多层板的成本高昂,而使用成本更低的两层板,又似乎难以实现有效的阻抗匹配。面对这种两难局面,真的没有解决方案吗?

在高速设计中,阻抗匹配是保证信号质量的关键。多层板(通常四层及以上)因其具备完整的内电层作为参考平面,实现阻抗匹配相对容易。然而,对于成本敏感的两层板设计,由于缺乏专属的参考层,传统的设计与计算方法不再适用,这难道意味着两层板注定与“阻抗匹配”无缘?

无需担心!本文将深入探讨如何在两层板上实现有效的阻抗匹配,分享一套平衡性能与成本的实用方法。

一、核心难点:两层板实现阻抗匹配的挑战

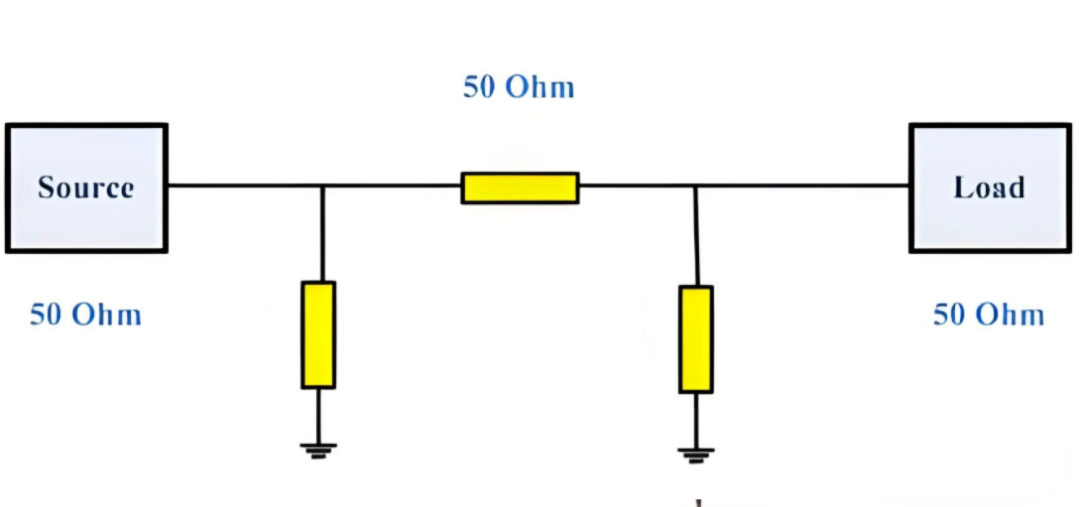

首先明确基本原理:阻抗匹配的目的是确保信号能完整地传输到接收端,减少反射与损耗。多层板的优势在于其拥有稳定的“参考平面”,这为精确计算和控制特性阻抗提供了明确的依据。

两层板设计的根本挑战恰恰在于缺少这个专用的参考平面,从而引发三个核心问题:

- 信号传输缺乏稳定的参考基准。

- 基于多层板结构的传统线宽、板厚计算公式失效。

- 设计不当极易导致信号完整性恶化,影响产品性能。

二、解决方案:构建完整的信号返回路径

实际上,两层板可以实现阻抗匹配,关键在于转变设计思路。经过大量工程验证,其核心在于:为信号提供一条低阻抗且不间断的电流返回路径。

通俗地说,这就是“包地”技术,但必须遵循一个铁律:用作包地的地线必须保持连续,绝不能被人为或过孔打断。从传输线理论角度,这种设计对应的模型是“共面波导”或“共面阻抗”,它是两层板实现可控阻抗的唯一可行途径。

三、实测参数与设计参考

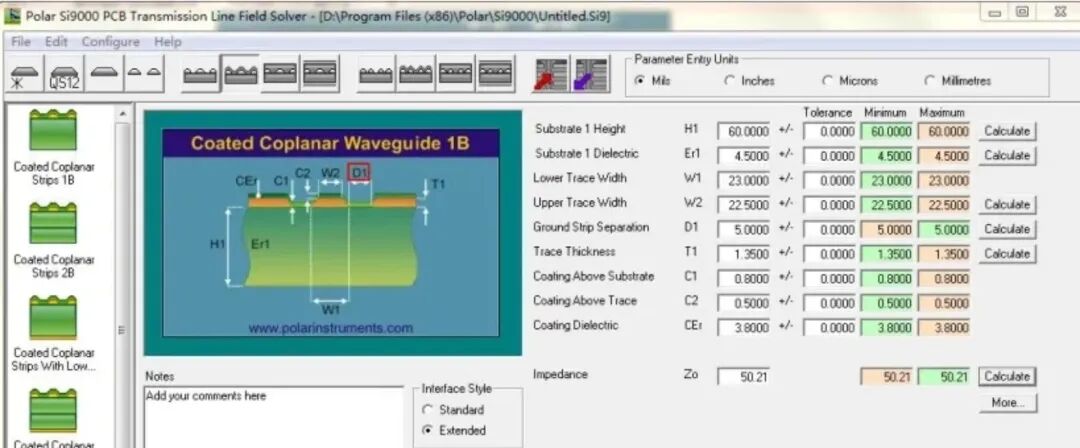

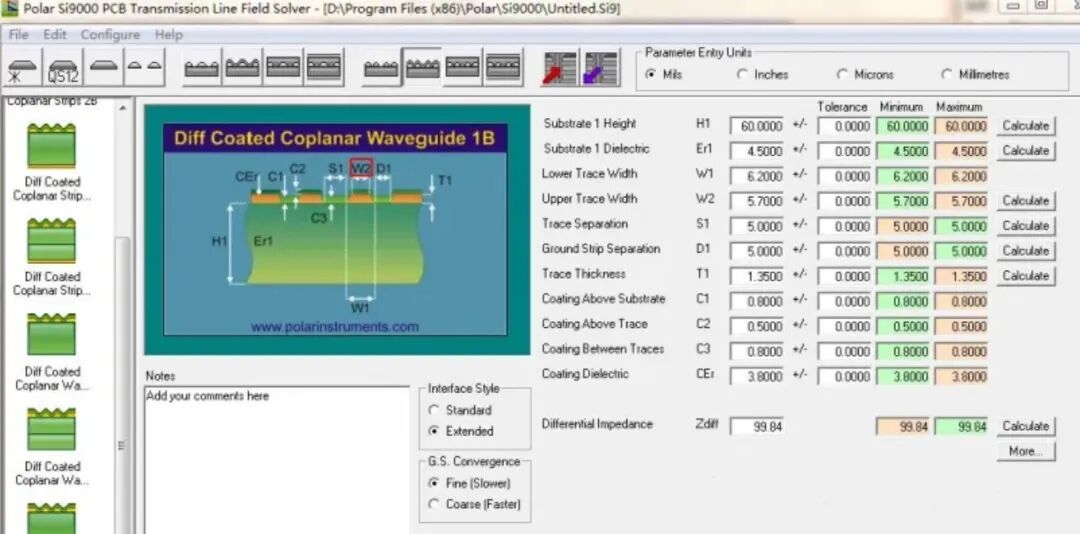

理论需要数据支撑。我们使用业界通用的阻抗计算工具SI9000进行仿真,整理了三种常见阻抗值(50Ω单端、90Ω差分、100Ω差分)的详细设计参数,并附上计算截图,可供设计时直接参考。

1. 50Ω(单端信号)

- 核心参数:下层线宽 23.0000 mil,上层线宽 22.5000 mil,地线间距 5.0000 mil,介质厚度 60.0000 mil。

- 计算结果:特性阻抗 50.21 Ω(误差极小,可直接应用)。

2. 90Ω(差分对)

- 核心参数:下层线宽 9.3000 mil,上层线宽 8.8000 mil,线间距 5.0000 mil,地线间距 5.0000 mil。

- 计算结果:差分阻抗 89.96 Ω(接近标准值,性能稳定)。

3. 100Ω(差分对)

- 核心参数:下层线宽 6.2000 mil,上层线宽 5.7000 mil,线间距 5.0000 mil,地线间距 5.0000 mil。

- 计算结果:差分阻抗 99.84 Ω(精度高,适用于对信号质量要求严格的场景)。

四、量产案例:电信机顶盒的降本实践

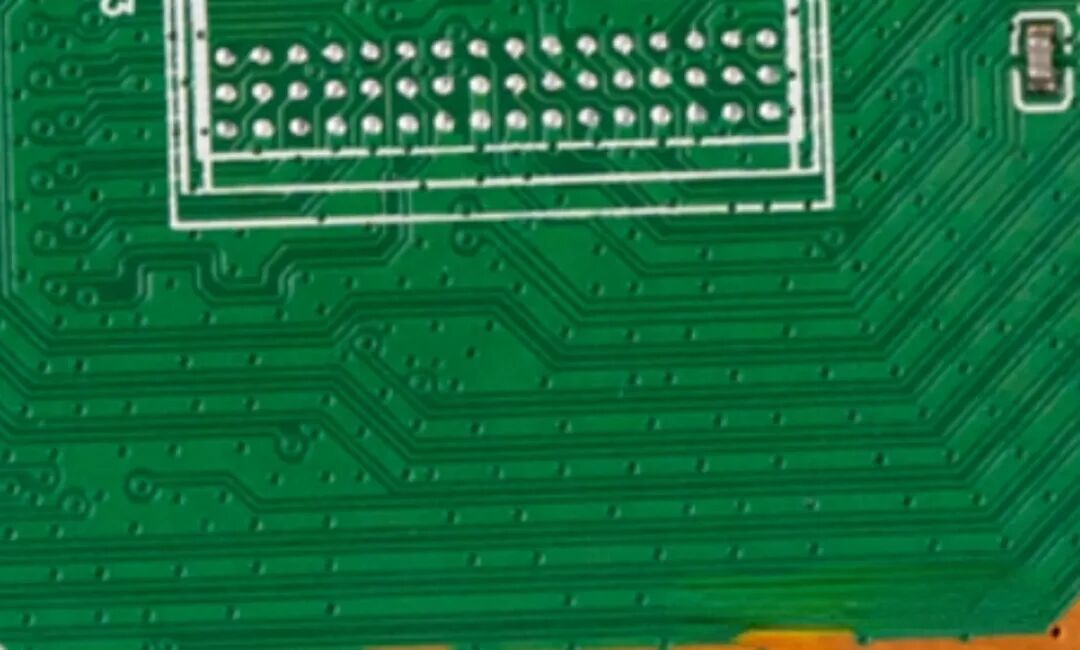

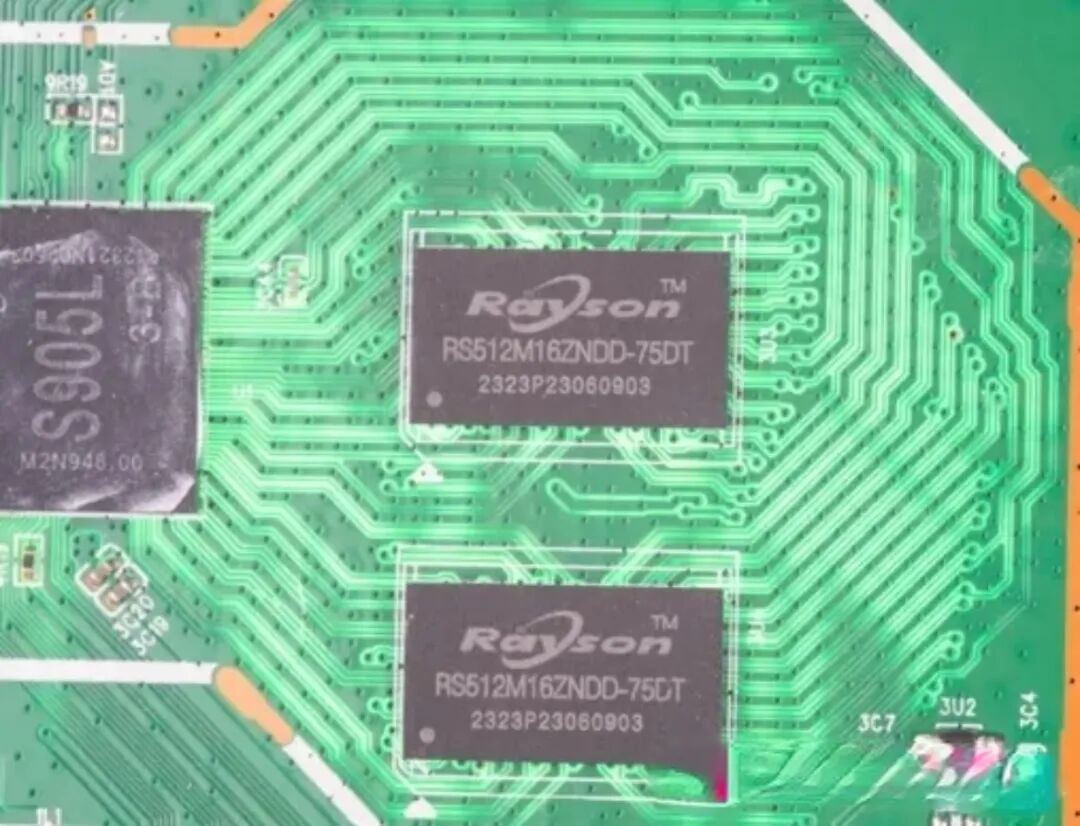

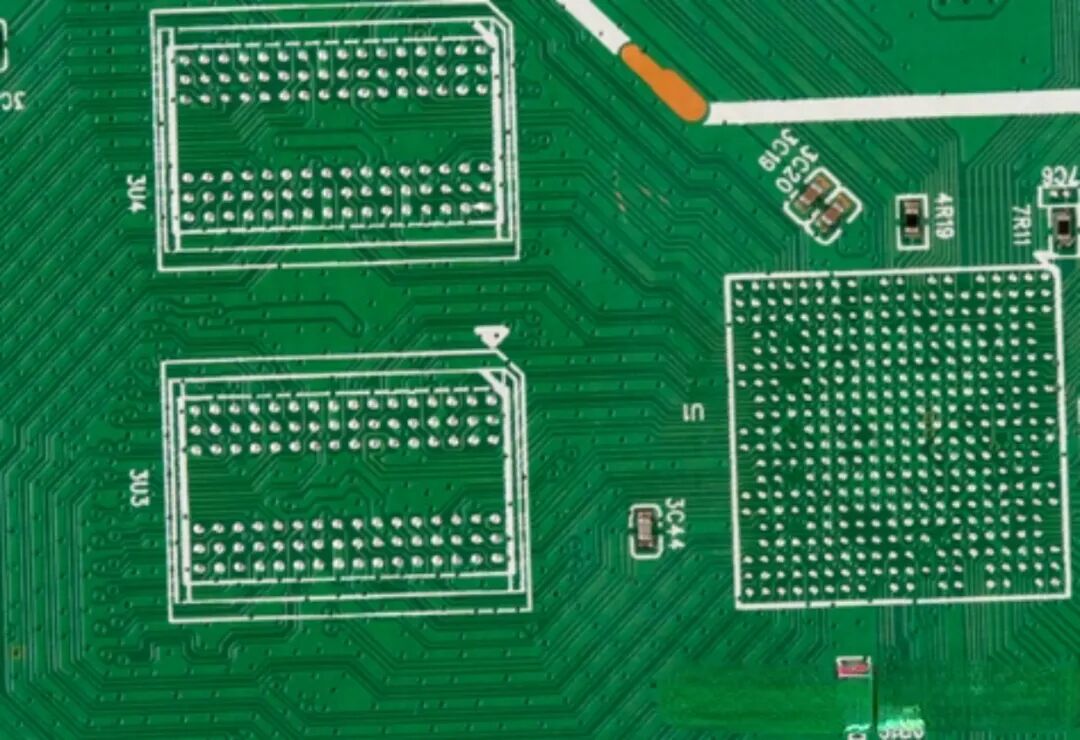

理论结合实践才最具说服力。以某款电信机顶盒为例,其为了极致成本控制,采用了双层板设计并成功实现了阻抗匹配。

如何判断其为两层板?从拆机图的背面打光可见,光线能够完全穿透板体,这是多层板无法达到的透光率。其实现阻抗匹配的核心技巧正是前述的“包地”设计,具体表现为:

- 单侧包地:在信号线一侧铺设连续的地铜皮,确保电流返回路径连贯。

- 保持间距:信号线之间留有足够距离,以减少串扰。

- 两两隔离:对关键信号线采取两两包地的形式,进一步增强隔离度与稳定性。

这种设计在信号质量上做出了合理妥协,但完全满足了机顶盒的功能需求,同时相比四层板方案,成本降低了30%以上,是成本控制的优秀范例。

五、实战避坑指南:布线可行性的权衡

需要注意的是,前述参考参数中存在一个现实矛盾:为实现50Ω单端阻抗所需的23mil线宽,在实际PCB设计中(尤其是像DDR内存这类布线密集的区域)往往难以实现。

行业内的通用应对策略是:在成本优先的前提下,对阻抗精度进行适度放宽。

- 放宽阻抗容差:将严格的50Ω要求放宽至60-70Ω范围重新计算,在保证基本信号完整性的前提下,显著减小所需线宽,解决布线难题。

- 优先保证布线:在满足产品性能要求的前提下,不必追求极致的阻抗精度,优先确保所有线路能够合理布局。

- 贴合量产设计:借鉴前述案例,采用单面包地、加大线距、关键信号两两包地的组合策略,在成本与性能间找到最佳平衡点。

六、总结:硬件设计的平衡艺术

在两层板上实现阻抗匹配,其核心思想始终是:为信号构建一个完整的返回路径(连续包地),并依据实际应用场景灵活调整设计参数。这或许不是性能上的“最优解”,但往往是成本效益上的“最佳解”。

为硬件工程师总结几个关键点:

- 需求先行:根据产品的具体应用场景确定可接受的阻抗标准,避免过度设计。

- 方案择优:多层板性能更优,但两层板通过合理利用共面阻抗模型,同样可以满足多数需求。

- 细节制胜:地线的连续性与信号间距的合理性,直接决定了最终阻抗控制的效果。

- 平衡之道:优秀的硬件设计在于精准匹配需求,在成本控制与技术创新之间找到最优的平衡点。

|