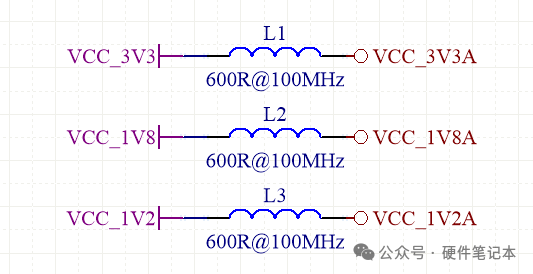

前段时间评审一块主板PCB时,layout工程师指着一颗有三组供电(3.3V、1.8V、1.2V)的芯片问我:“王工,为什么给每一路电源进来都要串一颗磁珠呢?我看你们好多项目都是这样的,确认是这样设计的吗?”

这个问题问得特别好,也比较典型。很多硬件工程师在平时工作中,也经常遇到类似的场景——看到参考设计用了磁珠,就照着画上去;别人问起,回答最多就是“为了抑制干扰”或者“参考设计就是这么做的”。可如果再往下问:磁珠到底是怎么抑制干扰的?具体该怎么选型?万一用不好会出什么问题?……可能一下子就难以说清了。

为了把这件事搞明白,也为了下次能更有底气、有依据地回答同事的疑问,今天我们就结合项目经验,把磁珠这件事好好梳理一下。网上的资料不少,重点强调几个实战中真正关键的点。

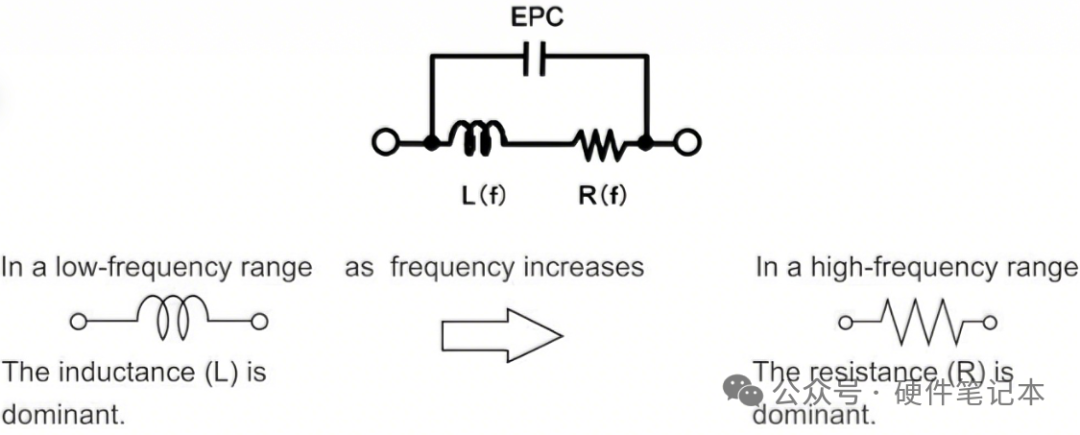

01 磁珠等效为电阻串联电感

这是最重要、也最基础的认知起点。很多人把磁珠和电感搞混,甚至直接替换,这是很多坑的根源。

一个理想的功率电感,它在高频下的阻抗主要是感抗(XL = 2πfL),它会把噪声能量存储在电感的磁场中,通过电路路径返回电源、流向地,或以电磁波形式辐射出去。

而磁珠的等效模型,是一个电阻R和一个电感L串联。它发生在高频段:磁珠内部的铁氧体材料,会像一块吸音海绵,将高频噪声的能量吸收进来,转化成微不足道的热量消耗掉。

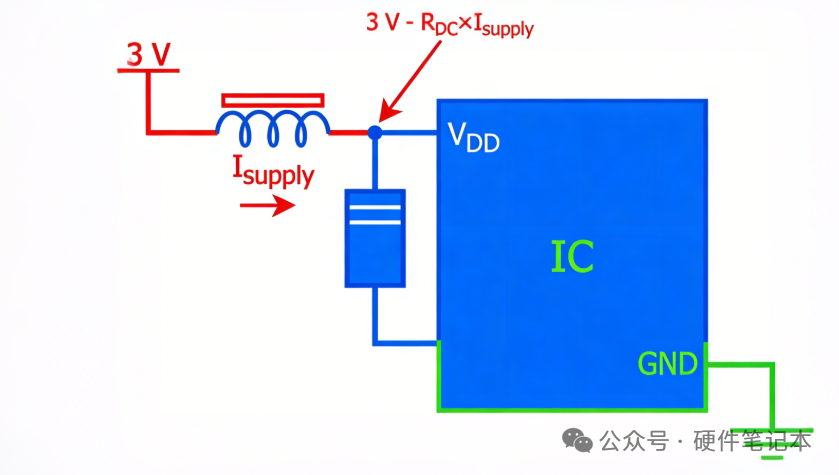

所以,回到开头的问题:为什么要在三组电源入口都放磁珠?核心目的就是起到隔离和抑制干扰的作用。如果这三路电源是给同一个芯片内部不同模块供电的(比如一个芯片里同时有模拟电路、数字核心和PLL锁相环),那么每一路都可能产生特定的噪声。如果不加隔离,这些噪声就会顺着共用的电源网络到处串,相互干扰。磁珠的作用,就是给每一路电源建立一个本地化的能量吸收器,让各自产生的高频噪声在自家门口就被消化掉,防止去污染其他干净的电源轨,尤其是对噪声极其敏感的模拟或射频电路。

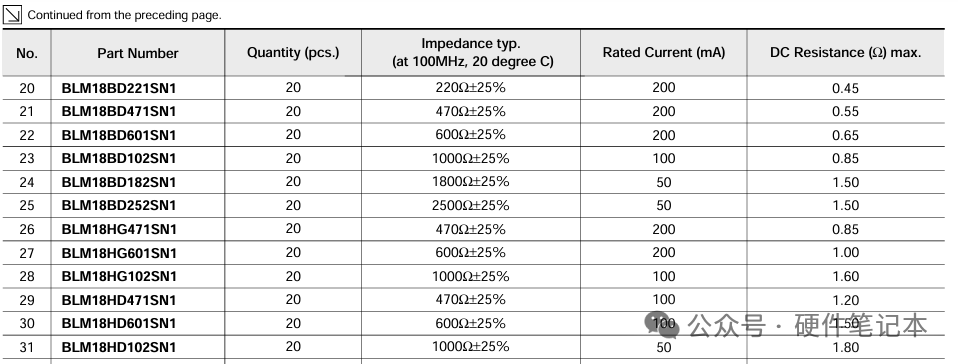

02 看曲线,别光看那个600R

打开任何一份磁珠的数据手册,最醒目的位置通常会标着600R@100MHz。这个600R是它在100MHz测试频率下的阻抗模值。但请注意,这是结果,不是原因。直接根据这个数字选型,是新手最容易踩的坑。

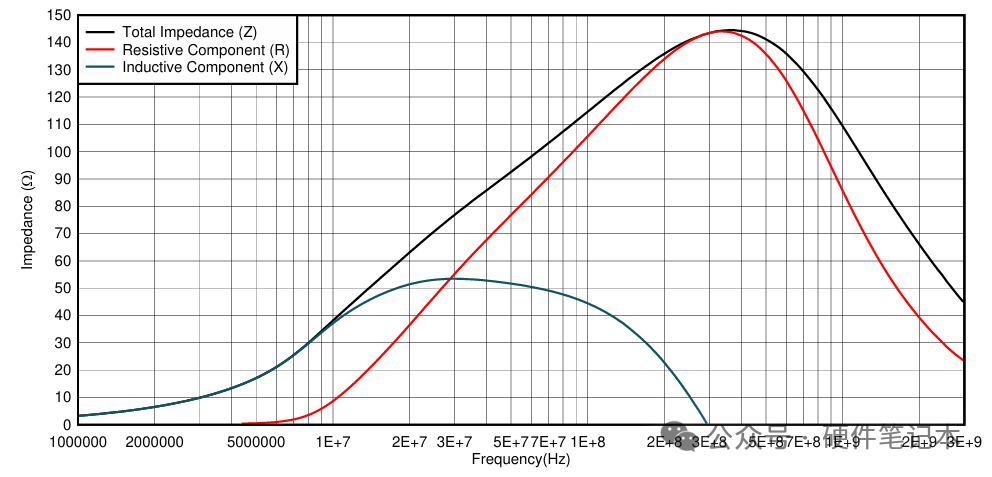

因为,你的噪声频率不一定是100MHz。磁珠的阻抗-频率曲线(Z-f曲线)是一条有起有落的山丘状曲线,每颗磁珠的山峰位置和高度都不同。

这就引出一个关键问题:你必须先知道你想对付的敌人,也就是噪声主要在哪个频段。 是几十MHz的CPU开关噪声?还是几百MHz的DDR时钟谐波?或者是GHz级别的无线干扰?

假设你需要抑制的主要是50MHz的噪声,那么你应该去Z-f曲线上找它在50MHz时的阻抗值,而不是盲目相信那颗标称600R@100MHz的磁珠在50MHz时也表现良好。很可能另一颗标称300R@100MHz的磁珠,其阻抗峰值恰恰在50MHz附近,实际效果反而更好。选磁珠,本质是用它的阻抗峰值去对准你的噪声峰值。

03 小心,电流会让磁珠失灵

这是硬件老手也可能疏忽的深水区。磁珠的吸收能力,和流过它的直流电流大小直接相关。

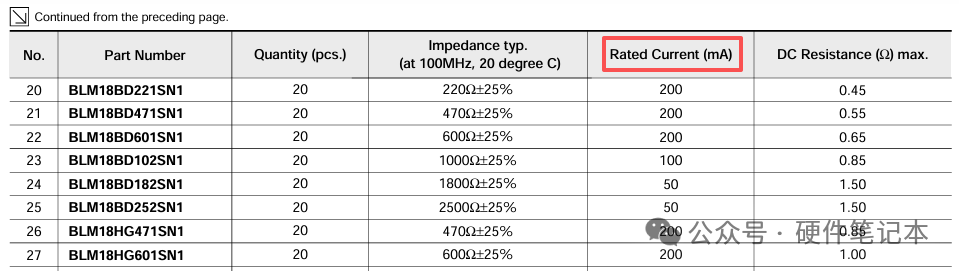

所有磁珠都有一个额定电流,但请注意,这个参数通常只保证它不被烧坏,不保证它性能完好!真正决定性能的是直流偏置特性。

当较大的直流电流(比如给你的CPU核心供电的1.2V/2A)流过磁珠时,其内部的铁氧体材料会发生磁饱和。饱和的直接后果,就是等效电感量骤降。反映在Z-f曲线上,你会看到一个悲剧的现象:随着电流增大,那座阻抗山峰不仅高度降低了,也就是峰值阻抗变小,整个山头还向更高频率方向移动了。

这意味着什么?意味着你为抑制100MHz噪声精心挑选的磁珠,在通上满载工作电流后,它的最佳抑制频率可能跑到了200MHz,在100MHz处的阻抗已经塌方,滤波效果大打折扣。

因此,选型时必须查阅手册中的阻抗-频率-直流偏置曲线图。在你的最大工作电流对应的那条曲线上,确认在你关心的噪声频率点,阻抗值仍然满足要求。一个好的经验法则是:所选磁珠的饱和电流,至少是线路最大直流电流的1.3倍。

04 算算账,DCR带来的副作用

磁珠的直流电阻DCR通常很小,是毫欧级别,但绝不能忽略不计。

当你为大电流电源路径,比如给射频功放PA供电的路径选择磁珠时,为了追求极致滤波,可能会选阻抗很高的型号。但高阻抗往往伴随更高的DCR。这会带来两个现实问题:

1、电压跌落IR Drop

功耗 P_loss = I² * DCR。

例如,2A电流流过一颗50毫欧DCR的磁珠,会产生0.1V的压降和0.2W的发热。这可能让后级芯片供电电压跌出容限范围。

2、自身发热与温升

0.2W的功耗在小体积磁珠上可能导致显著温升,而高温又会进一步改变其磁性能,形成恶性循环。

所以,滤波效果、电压裕量和热稳定性,三者必须考虑权衡。

05 小结

把以上内容搞清楚,你就能从“参考设计这么用的”跟随者,变成“我基于这些理由选择它”的设计者。硬件设计的功底,正是在这种对基础元件的深度理解中,一点点扎实起来的。

1、射频RF走线,请慎用磁珠

在50欧姆的射频主路径上,我们通常使用高频电感进行匹配或滤波,而几乎不用磁珠。原因很简单:磁珠在射频频段,如900MHz的阻抗往往高达数百欧姆,会直接堵死射频信号,造成严重的反射损耗,信号根本过不去。当然,像FM收音机75欧姆系统这种低频射频有特例。

但通用原则是:信号线优先考虑电感,电源线优先考虑磁珠。

2、换个思路,治本优于治标

所有通过磁珠、电容进行的滤波,都是在噪声传播的路径上设卡拦截,属于治标。而最有效、最高级的方法,永远是直接从噪声来源着手,也就是治本。比如优化芯片的电源去耦网络、对高速时钟信号进行适当的端接和屏蔽、改善板级的电路设计以增强电磁兼容性。在源头把噪声降到最低,后面的滤波压力就会小很多。

希望这次的分享,能让你在和磁珠打交道时,心里更有底。更多深入的硬件设计讨论,也欢迎你来云栈社区交流。