对于硬件工程师而言,静电放电(ESD)测试无疑是电磁兼容性(EMC)认证中最具挑战性的环节之一。ESD现象本质上是两个具有不同电位的物体表面之间发生的瞬时电荷转移,其瞬间产生的强电流足以对芯片的栅极氧化层、金属化层乃至PN结构成致命威胁。

传统上,我们只能在PCB打板完成后,前往昂贵的专业EMC实验室使用静电枪进行实测。想必许多同行都有过类似经历,实验室按小时计费,成本不菲。一旦测试失败,就意味着要重新设计、添加防护器件如TVS管,不仅耗费资金,项目周期也被严重拖长。那么,一个更高效的问题随之而来:我们能否在电路设计的早期阶段,就借助仿真工具来预先评估ESD防护方案的有效性呢?

答案是肯定的。来自意大利马尔凯理工大学的Luca Buccolini研究员便提供了一个基于IEC 61000-4-2标准的实用SPICE模型,让我们在设计阶段进行ESD仿真成为可能。

理解标准ESD波形:IEC 61000-4-2

在系统级ESD测试领域,业界广泛遵循的是国际电工委员会(IEC)发布的IEC 61000-4-2标准。该标准定义的静电放电强度远高于器件级的HBM(人体模型)或CDM(带电器件模型)测试要求。

标准的接触放电电流波形具有两个显著特征峰:

- 初始峰值:由放电枪的手臂等效网络产生,电流极大且上升沿极陡,通常在0.6至1纳秒内达到峰值。

- 第二峰值:由人体躯干等效网络产生,电流幅值较低但持续时间较长,形成一个较为宽缓的波峰。

IEC 61000-4-2标准依据严酷等级规定了不同的测试电压与对应的初始峰值电流:

| 等级 |

测试电压 |

初始峰值电流 (典型值) |

| Level 1 |

2 kV |

7.5 A |

| Level 2 |

4 kV |

15 A |

| Level 3 |

6 kV |

22.5 A |

| Level 4 |

8 kV |

30 A |

标准文档中虽然给出了一个简化的ESD发生器电路原理图,但如果直接将其用于SPICE仿真,往往无法复现出标准所描述的理想“双峰”波形。

构建精准的SPICE仿真模型

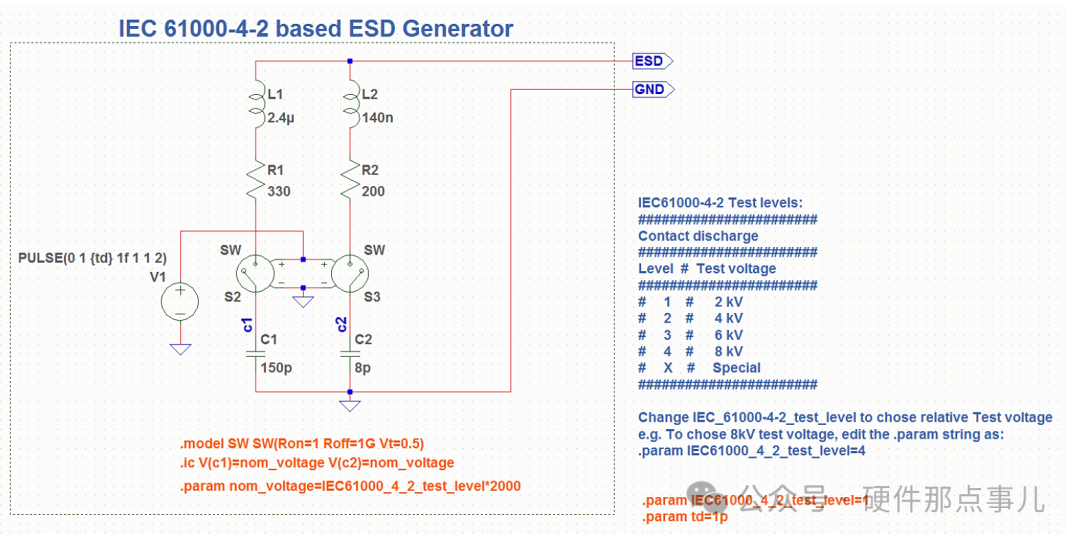

为了在仿真中精确复现标准波形,Luca Buccolini提出了一个利用两个并联的R-L-C网络来模拟不同放电路径的改进模型。该模型通过调整寄生参数,能够较好地还原实际的尖端放电与接地回路效应。

你可以在LTspice等SPICE仿真软件中搭建如下电路:

模型包含两个主要分支:

-

主体与接地带网络:模拟静电枪主体及长约2米的接地电缆。

- 电容

C1 = 150 pF

- 电阻

R1 = 330 Ω

- 电感

L1 = 2.4 μH

-

枪头寄生网络:塑造上升沿极快的初始电流峰值。

- 电容

C2 = 8 pF

- 电阻

R2 = 200 Ω

- 电感

L2 = 140 nH

关键设置步骤:

- 初始充电:使用

.ic(初始条件)命令将电容C1和C2充电至目标测试电压。例如,对于4kV测试,应设置为:

.ic V(c1)=4kV V(c2)=4kV

- 放电控制:在电容网络与输出端之间串联一个电压控制开关(SW)。通过一个脉冲电压源

PULSE 来控制开关在预设延迟时间 td 后闭合,从而将储存的高压电荷瞬间注入到待测电路(DUT)中。

模型验证与仿真结果

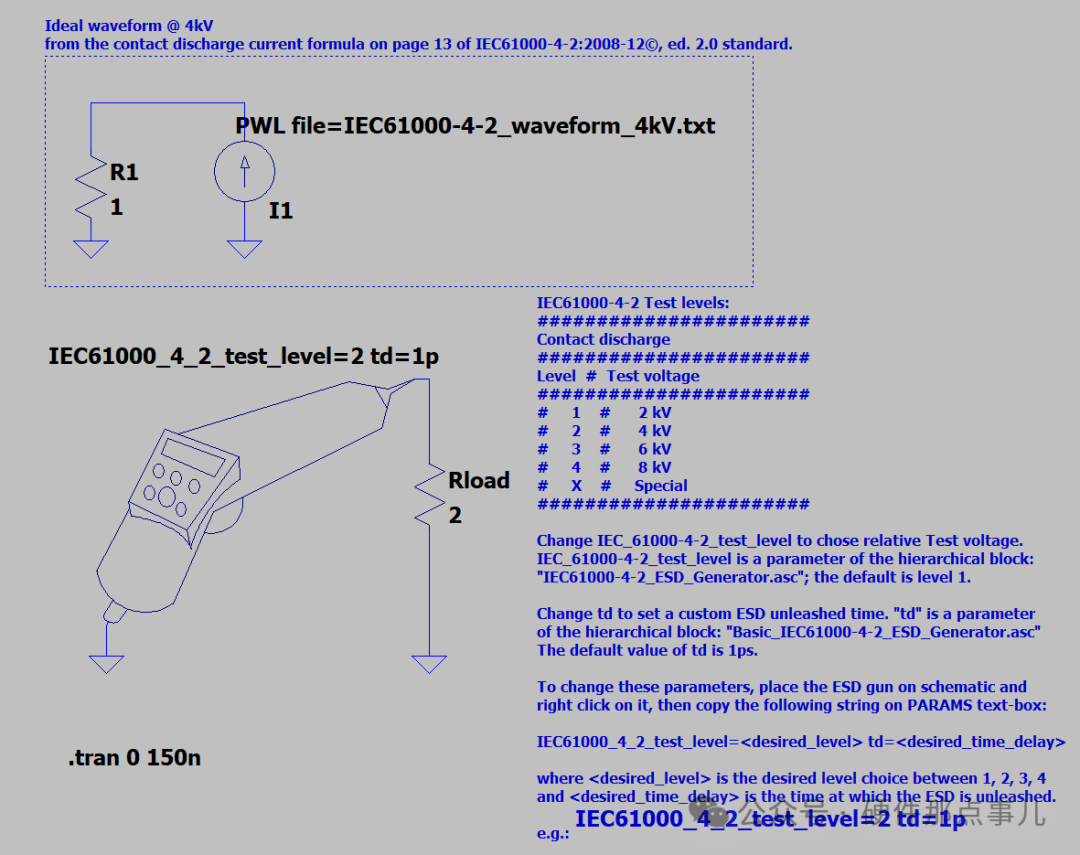

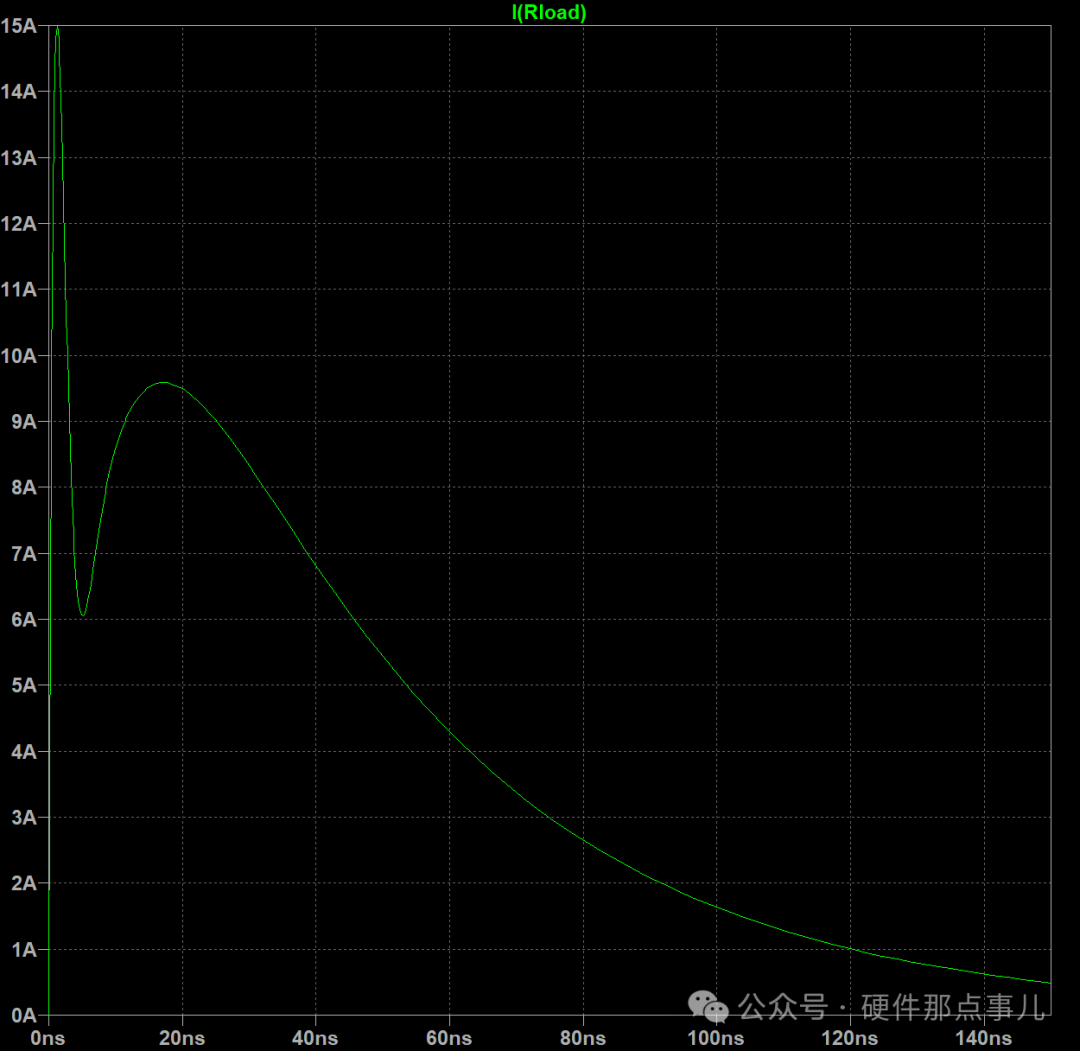

这个模型的准确性如何?我们可以依据IEC标准中的验证方法进行测试。标准要求测量放电电流时,使用的电流靶在直流下的输入阻抗不应超过2.1Ω。因此,在仿真中,我们将ESD发生器模型连接到一个2Ω的负载电阻上进行放电测试。

运行瞬态分析后,得到的负载电流波形与IEC标准中通过数学公式计算的理想波形高度吻合。无论是初始峰值电流、30纳秒时刻的电流值还是60纳秒时刻的电流值,都完全满足标准规定的容差要求。

工程应用:量化评估防护方案

拥有了这个可靠的ESD发生器模型,你可以在绘制PCB版图之前,就将接口电路(如USB、RS-485、CAN等)在SPICE中搭建出来。将ESD发生器的“枪头”接在需要保护的接口端子上,并在接口线路与地之间并联你计划选用的TVS管(可导入厂商提供的SPICE模型)。

运行瞬态仿真,关键观测点是经过TVS管钳位后,到达核心MCU或敏感芯片引脚上的残留电压。你需要确保这个残压值低于芯片数据手册中规定的“绝对最大额定值”。这种方法不仅能大幅降低因ESD问题导致的反复打板试错成本,更能帮助你客观、量化地比较不同型号TVS管的钳位性能,从而选出最优的防护方案。

通过将SPICE仿真引入ESD防护设计流程,工程师可以在虚拟环境中预先“经历”雷击考验,让硬件设计变得更加稳健可靠。这正是深入理解并应用计算机基础与电路原理,来解决实际工程问题的价值体现。我们也可以在云栈社区等技术论坛交流更多硬件设计与仿真的实战经验。 |