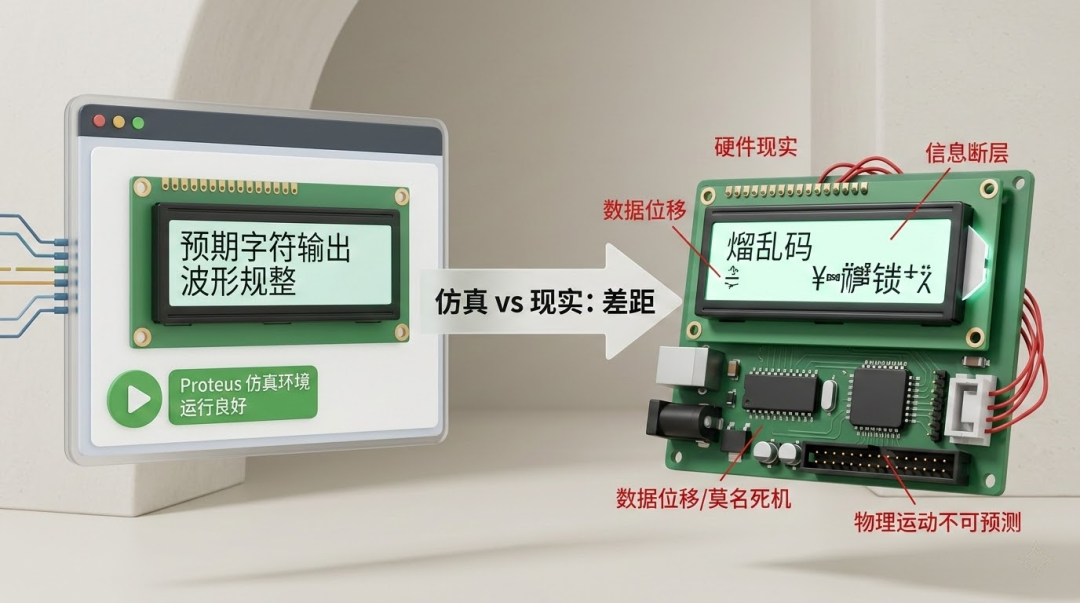

对于许多嵌入式工程师而言,在项目初期使用Proteus进行电路与代码仿真,几乎成了一种标准操作。在软件界面中连接好虚拟导线,点击运行,LCD1602立即显示出预定字符,示波器波形完美得像从教科书里复制出来一样。然而,当相同的代码被烧录进真实的PCB板后,故事往往急转直下:屏幕可能出现乱码,串口数据莫名位移,甚至单片机在某个逻辑点毫无征兆地死机。这种“仿真绿灯行,硬件红灯停”的强烈反差,其根源在于Proteus仿真引擎对物理世界的数学抽象,与真实电子运动之间存在一道难以逾越的信息断层。

一、Proteus混合仿真引擎的底层架构分析

要客观评价Proteus是否可靠,我们必须先剖析它的核心——混合信号仿真引擎(ProSPICE)。该引擎基于伯克利大学的SPICE3F5工业标准构建,将电路模型划分为两个并行处理平面:模拟平面和数字平面。

在模拟平面上,Proteus采用节点电压分析法来求解基尔霍夫电流定律方程。对于每一个时间步长,仿真器都会构建一个大型的非线性代数方程组,并利用牛顿-拉夫逊迭代算法进行求解。这意味着,当你仿真一个电容充电过程时,Proteus实际上在后台反复计算 $V_{out} = V_{in}(1 - e^{-t/RC})$ 的数值解。

在数字平面上,Proteus采用的是基于事件驱动的仿真机制。它并不实时计算电平的连续变化,而只在信号发生0到1或1到0的跳变时,才更新逻辑状态。这种设计效率极高,足以支持复杂单片机的运行。

然而,其致命局限也在于此:混合模式仿真必须在模拟和数字这两种完全不同时间步长逻辑之间进行同步。当一个数字引脚驱动一个模拟负载(例如GPIO驱动带寄生电感的继电器)时,仿真器必须在“逻辑状态”与“电压曲线”之间进行极其复杂的插值计算。如果时间步长设置过大,这种跨平面同步就会产生舍入误差,导致仿真结果偏离物理现实。

二、MCU模型对指令集执行的抽象等级

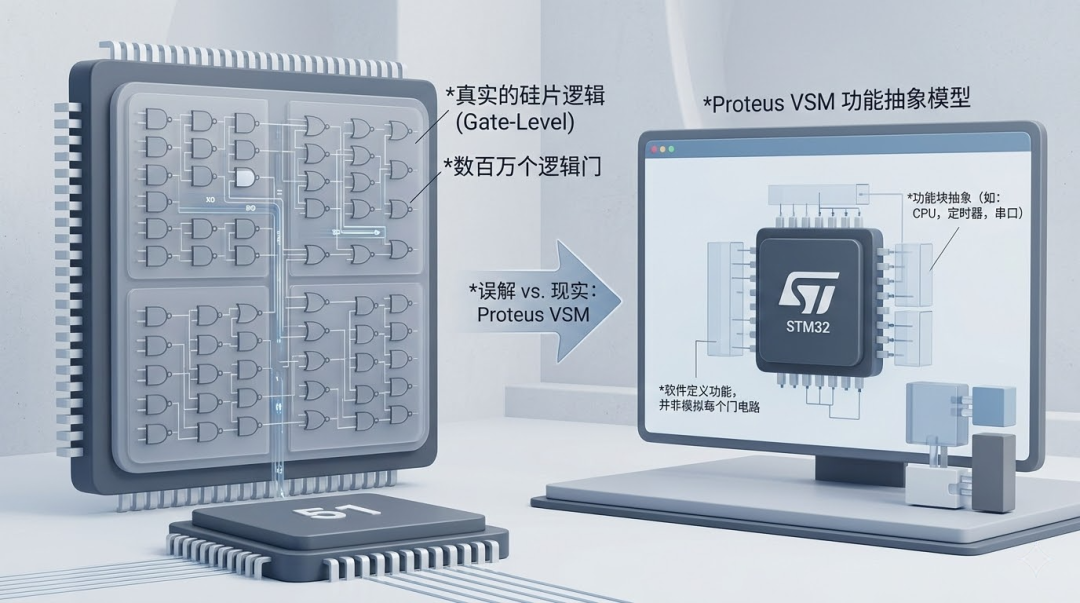

许多开发者存在一个误解,认为Proteus在仿真STM32或51单片机时,是在电脑里完整复刻了硅片逻辑。实际上,Proteus的VSM模型大多基于功能抽象,而非门电路级仿真。

当我们将一个 .hex 或 .elf 文件加载到Proteus的MCU模块时,仿真引擎运行的其实是一个指令集模拟器。它通过读取机器码,模拟堆栈指针、程序计数器以及通用寄存器的状态迁移。对于简单的逻辑控制,这种模拟足够准确;但一旦涉及精确时序场景,差距便暴露无遗。

例如,在真实的高性能MCU中,指令执行受三级或五级流水线影响,还存在分支预测失败导致的流水线清空开销。而Proteus的模型通常假设指令执行时间是恒定的。在编写精准的软件延时函数或处理超高频PWM捕获时,这种微小的时钟周期偏差会被急剧放大。更关键的是,Proteus很难完美模拟CPU的中断嵌套延迟。在物理硬件中,由于总线仲裁和Flash取指等待位的存在,中断响应时间会有数个周期的抖动;而在理想化的仿真环境里,这种抖动常被屏蔽,导致一些在硬件上可能出现的竞态条件在仿真中消失。

三、物理层电气特性的理想化陷阱

在Proteus的工作区里,导线被视为零阻抗,电源是完美的恒压源,地平面是绝对的零电位参考点。然而,在真实的硬件链路中,这些“理想化”假设恰恰是bug的温床。

一个典型例子是电源纹波与地弹。在Proteus中,你可以让10个LED同时以1kHz频率闪烁,仿真波形依然完美。但在实际PCB上,大电流的高频切换会导致电源轨产生瞬态电压降 $\Delta V$。由于PCB走线存在寄生电感 $L_{trace}$,这种电压波动可能触发单片机的欠压复位或导致内部时钟PLL失锁。Proteus的默认设置完全忽略了走线的分布参数。

此外,仿真中对输入引脚阻抗特性的简化也埋下隐患。真实硬件引脚存在输入电容(通常5-10pF)和漏电流。在进行I2C总线仿真时,Proteus里的上拉电阻设置一个值就能工作。但在实际电路中,如果上拉电阻过大,结合引脚寄生电容,会导致时钟信号上升沿变得极其缓慢,甚至无法达到逻辑高电平阈值 $V_{IH}$。这种典型的RC充放电延迟,在仿真中若不手动添加寄生模型,永远无法复现。

四、外设模型与传感器数据的“数学假象”

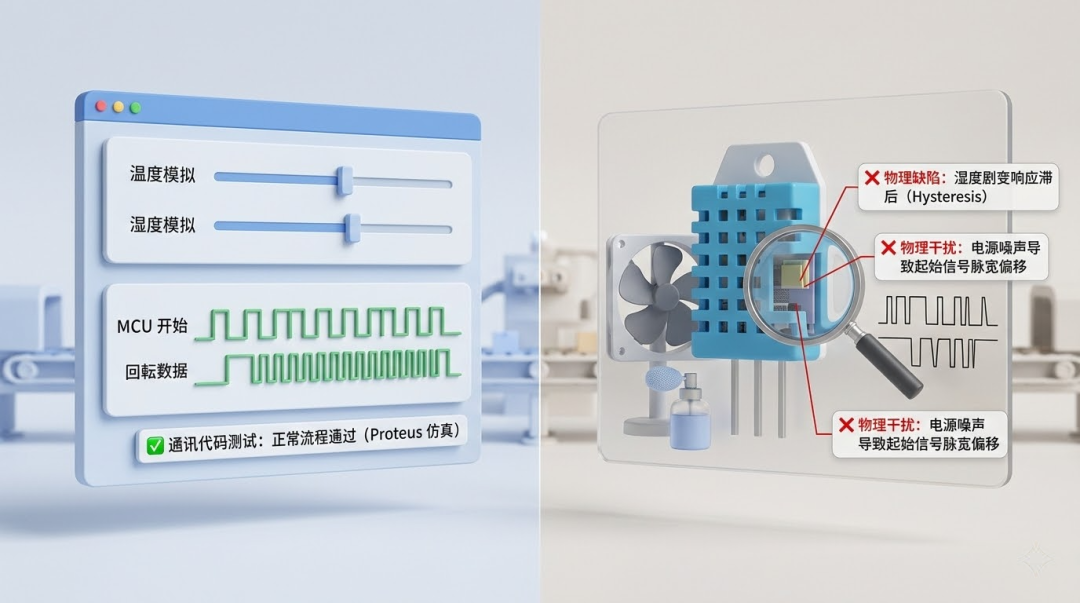

Proteus提供了丰富的组件库,从LCD显示屏到I2C温度传感器。但这些外设并非真实的物理模型,而是基于协议栈编写的“脚本行为”。

以常用的温湿度传感器DHT11为例,在Proteus中我们通过调节模拟滑块来改变温度值。仿真器接收到MCU的起始信号后,会按协议手册规定的时序回发一段预设数据流。这种模拟只验证了通讯代码在“理想流程”下是否正确,却无法模拟传感器的物理缺陷:例如湿度剧变时的响应滞后,或是电源噪声干扰导致的起始信号脉宽偏移。

更进一步,Proteus的LCD1602或OLED模型通常是直接解析MCU发送的指令并渲染到屏幕。它忽略了显示屏控制器内部严格的初始化时序要求。在真实硬件中,LCD初始化往往需要等待足够的Power-on Reset时间,如果代码中漏掉50ms延时,真实屏幕可能黑屏或花屏,但Proteus的虚拟屏幕却可能正常显示。这种“过度宽容”易让开发者养成不良编码习惯,忽视对硬件数据手册中时序参数的敬畏。

五、中断系统与异步事件的同步误差

在嵌入式开发中,最难调试的莫过于多任务下的异步事件冲突。Proteus的时钟系统是全局同步的,这意味着仿真的每一步都在仿真主时钟的节拍下进行。

在真实物理世界中,外部中断触发(如外部脉冲输入)与内部时钟频率是相互独立的异步过程。这会引入亚稳态的风险,即触发器在采样瞬间可能处于不确定的电平状态。Proteus的数字逻辑引擎基于离散状态切换,本质上无法模拟亚稳态现象。

此外,Proteus对多外设协作的仿真存在“单线程化”倾向。假设单片机正在执行DMA传输,同时CPU在处理高优先级定时器中断。在物理芯片内部,这涉及总线矩阵的仲裁,DMA和CPU可能竞争同一块SRAM区域。但在Proteus中,这种底层硬件资源竞争常被简化为互不干扰的逻辑流。如果代码中未处理好内存一致性问题,在仿真中可能永远跑不到错误分支,而在真实硬件上却会导致随机的内存踩踏。

六、为什么仿真时的时间并不是真实的时间

如果你尝试在Proteus中仿真一个72MHz的STM32运行复杂算法,会发现仿真进度条下方的“Simulation Time”远慢于现实中的秒表。这就是所谓的“仿真效率瓶颈”。

由于ProSPICE引擎需要不断求解复杂的非线性方程,当电路规模增大时,计算量呈指数级上升。当计算机CPU无法实时完成当前时间片内的所有计算时,Proteus就会被迫降速运行。这种模式虽保证了数学准确性,却破坏了对硬件“实时性”的直观感知。

在复杂系统中,由于这种降速,我们很难评估真实系统里的看门狗是否会溢出。在Proteus中,看门狗计时器也是相对于仿真时间运行的,因此即便系统运行极其缓慢,只要逻辑正确,看门狗就不会复位。但在真实的硬件生产环境中,由于复杂的EMI干扰或主频波动,代码执行时间可能超出预期,导致看门狗复位。这种对系统健壮性的关键考量,在仿真器中是完全失效的。

七、编译优化等级对仿真的诡异影响

一个硬核现象是:相同的C代码,在 -O0(不优化)和 -O2(性能优化)编译模式下,在Proteus里的表现可能一致,但在硬件上却天差地别。

这是因为编译器在高级优化模式下,会进行指令重排、循环展开及寄存器变量映射。在硬件层面,这些操作会显著改变代码执行的指令流速度,从而影响对时序敏感的寄存器操作。由于Proteus的VSM模型对寄存器写入的“物理生效时间”模拟不够精细(常认为写入即生效),它无法捕捉因CPU运行过快而导致的外设同步失效。

例如,连续写入两个SPI数据寄存器时,在真实硬件中必须等待状态位 TXE 置位。如果优化后的代码在硬件上运行极快,而我们忘记了检查标志位,数据就会丢失。但在Proteus中,由于其模型内部可能使用了缓冲队列,即使你不检查 TXE,它可能也能“顺畅”接收所有数据。这种隐蔽的bug会被仿真器完美掩盖,直到你在硬件调试时面对示波器上混乱的信号一筹莫展。

八、科学使用Proteus的工程师准则

既然Proteus与现实硬件存在如此多层面的断层,它是否就一无是处?绝非如此。关键在于明确仿真的“边界”。

我们应将Proteus定位为“逻辑验证工具”而非“物理验证工具”。它非常适合验证以下内容:

- 纯逻辑算法:如PID计算、滤波算法、复杂的通信协议解析状态机。

- 人机交互界面逻辑:菜单切换、按键扫描逻辑(忽略抖动时)。

- 大框架集成:验证多个模块(如串口、存储器、传感器)之间的基本业务数据流是否连通。

但对于以下场景,必须回归真实硬件(如开发板或示波器):

- 信号完整性分析:反射、串扰、上升沿畸变。

- 精密模拟电路:低功耗采样、小信号放大、高速运算放大器电路。

- 硬实时闭环控制:如电机控制中的FOC算法时序。

- 电源完整性与热设计。

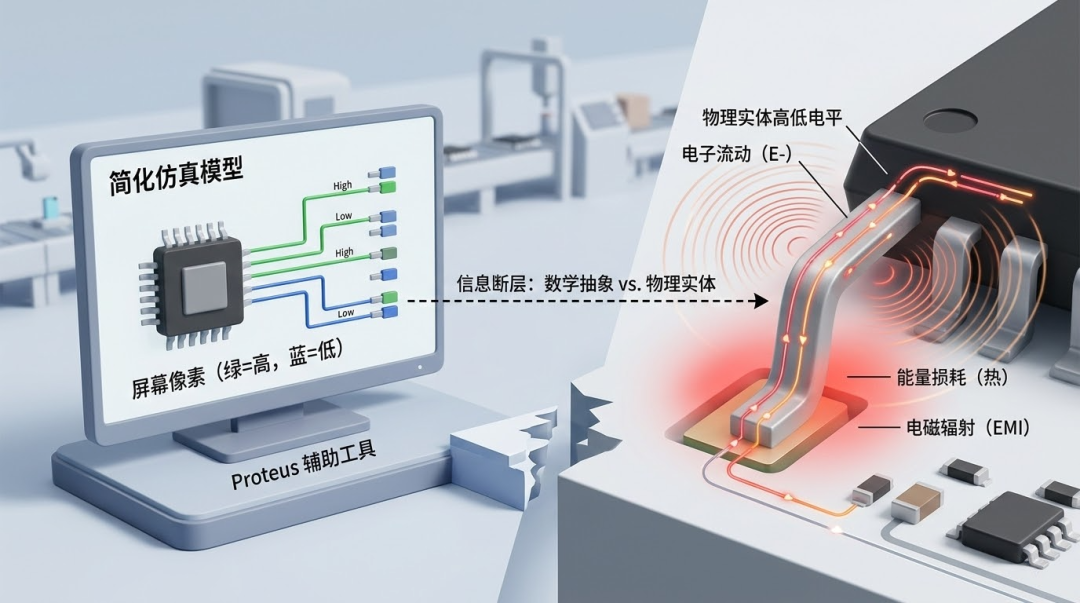

九、总结:建立基于“硬核怀疑”的开发思维

Proteus是一款极佳的辅助工具,但它建立在一套被高度简化的数学模型之上。作为专业的嵌入式工程师,我们需要时刻提醒自己:仿真器里的绿线(高电平)和蓝线(低电平)只是屏幕上的像素点,而物理世界中的高低电平是伴随着电子流动、能量损耗和电磁辐射的实体。

可靠的研发流程应当是:在Proteus中快速原型化,验证业务逻辑的完备性;一旦涉及底层驱动和硬件交互,必须尽早引入物理硬件进行交叉验证。只有理解了SPICE引擎的局限性、理解了指令模拟器的抽象边界、理解了PCB寄生参数的物理意义,我们才能跨越“仿真与现实”的鸿沟,编写出真正健壮的代码。对于更多深入的计算机基础讨论与嵌入式开发实践,欢迎在技术社区交流探讨。