PCIe(Peripheral Component Interconnect Express)链路的功耗管理机制,对于现代计算系统实现高性能与低功耗的平衡至关重要。其管理主要通过两种方式实现:一是基于硬件的ASPM(Active State Power Management,活动状态电源管理)自动机制;二是由系统软件驱动控制的PCI-PM(PCI Power Management)机制。这两套机制共同作用于PCIe设备的功能状态(D_state)与链路物理状态(L_state),两者紧密关联,可以相互影响。简而言之,软件可以通过PCI-PM控制D状态和L状态,而ASPM则专用于在特定条件下自动控制L状态,从而实现精细化的能耗控制。

ASPM:硬件自动链路节能

ASPM是一种完全由硬件实现的自主节能机制。其核心思想是:即使PCIe设备的某个功能(Function)处于全功率工作状态(D0 State),其连接链路(Link)也可以在空闲时自动进入低功耗状态(如L0s或L1),从而在不影响功能可用性的前提下降低系统功耗。

- 工作前提:设备必须处于D0状态,ASPM机制才会生效。

- 控制范围:ASPM专门管理链路在L0、L0s和L1状态之间的迁移。其中,L0到L0s/L1的切换过程完全由硬件逻辑控制,系统软件无法干预,只能全局启用(Enable)或禁用(Disable)此功能。

- 软件视角:对于传统的PCIe软件驱动而言,链路状态(L-state)通常是透明的,它们主要通过设备的电源管理D状态来感知功耗变化。

PCI-PM:软件驱动的电源管理

与ASPM聚焦于链路不同,PCI-PM机制允许系统软件直接管理PCIe设备功能(Function)的电源状态,即D状态。D0是正常工作状态,功耗最高;D1、D2、D3hot、D3cold则为不同级别的低功耗休眠状态,其休眠深度与节能效果依次递增。

D状态详解

软件通过向设备配置空间(Configuration Space)的电源管理控制状态寄存器(PMCSR)写入请求,来切换指定Function的电源状态。

各状态定义与能力如下:

- D0_uninitialized:设备经过基本复位(Fundamental Reset)后进入的初始状态。此时设备已上电,但其内部寄存器处于默认值,仅能响应配置读写请求(Configuration Request TLP),无法主动发起其他TLP。这是一个过渡状态。

- D0_active:在软件完成对设备的使能配置(如设置Command寄存器)后进入的状态。这是PCIe设备功能齐全的全功率工作状态。

- D1:可选的低功耗状态。在此状态下,设备只能发送电源管理事件(PME)消息TLP,并接收配置(Configuration)和消息(Message)类型的TLP请求。接收其他任何TLP请求或完成包(Completion)均被视为非法。

- D2:与D1类似,但休眠更深、功耗更低。通常在设备功能预计长时间不被使用时进入。

- D3hot:由软件配置进入的深度休眠状态。设备仅允许接收配置和消息请求。若在此状态下接收请求出错,链路必须恢复到L0状态并上报错误。关键点:从D3hot状态唤醒后,设备将返回D0_uninitialized状态(相当于经历了一次热复位),而非D0_active状态。

- D3cold:最高级别的休眠状态,通过直接移除设备的主电源(Vcc)进入。从D3hot迁移到D3cold通常由PME_Turn_Off消息触发。当Vcc重新上电后,设备从D3cold状态返回到D0_uninitialized状态。

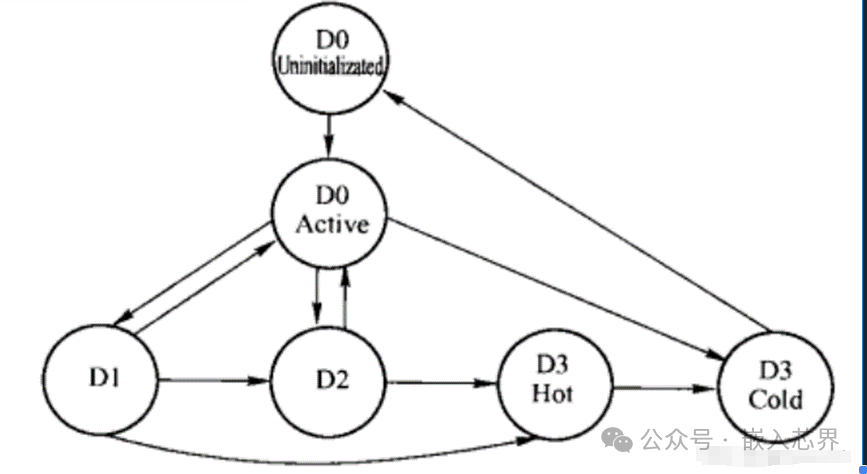

D-state状态机转换

下图清晰地展示了上述各D状态之间的转换关系与条件:

L状态分类与对应关系

链路物理状态(L-state)按照节能效果排序为:L0 < L0s < L1 < L2 < L3。状态越省电,恢复到全速工作状态(L0)所需的时间(延迟)也越长。

- L0:活动状态(Active State),ASPM和PCI-PM均在此状态下生效。

- L0s:低恢复延迟的节能“待机”状态。主电源、参考时钟和PLL均保持活动,为ASPM可选。

- L1:高延迟、低功耗的“待机”状态。可由PCI-PM触发,也为ASPM可选。此时主电源有效,但参考时钟和PLL可能关闭,导致退出延迟较大。此状态下禁止发送TLP和DLLP。

- L2/L3 Ready:一个过渡的伪状态,对应链路训练状态机(LTSSM)中的L2。当软件配置Function进入D3时,链路进入此状态。

- L2:由辅助电源(Vaux)供电的深度节能状态。Vaux负责为唤醒逻辑、PME上下文等供电。

- L3:完全断电状态,无任何电源供应。

D状态与L状态的对应关系是理解功耗管理的关键:

- 在D0状态下,链路可以处于L0、L0s或L1状态。

- 在D1、D2、D3hot状态下,链路仅支持L1状态。

- 在D3cold状态下,链路对应L2或L3状态(区别在于Vaux电源是否移除)。

L2/L3状态进入与退出

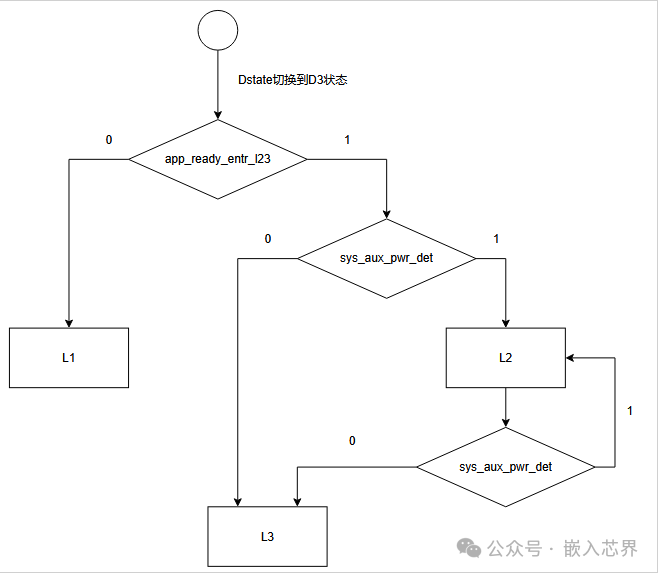

进入过程 (Entry):

默认情况下,当D状态切换到D3时,链路进入L1状态(对应D3hot)。若在切换前,相关控制信号(如app_ready_entr_l23)被置位,则链路可直接进入L2状态(对应D3cold)。如果系统进一步移除了辅助电源(sys_aux_pwr_det信号变化),则链路进入L3状态。

退出过程 (Exit):

系统可以通过多种方式从L2/L3状态唤醒:

- Beacon信号:软件可配置PHY寄存器,使能利用带内(in-band)信标(Beacon)信号唤醒链路退出L2状态。

- PERST#信号:通过解除置位(deassert)PCIe复位信号(PERST#)来退出L2或L3状态。

L2/L3的状态转换流程可参考下图:

驱动层实践:Linux内核中的PCIe功耗管理

在Linux内核的电源管理框架下,PCIe设备驱动程序可以通过实现标准的电源管理回调函数来支持休眠与唤醒。这对于嵌入式系统或服务器实现能效优化尤为重要。一个典型的驱动框架示例如下:

首先,在驱动结构体中声明电源管理操作:

static struct pci_driver xxx_driver = {

.name = "xxx",

.id_table = xxx_pci_table,

.probe = xxx_probe,

.remove = xxx_remove,

#ifdef CONFIG_PM

.suspend = xxx_suspend,

.resume = xxx_resume,

#endif

};

在挂起(Suspend)函数中,驱动程序保存设备状态、禁用设备并设置其进入低功耗状态(如D3hot):

static int xxx_suspend(struct pci_dev *pdev, pm_message_t state)

{

pci_save_state(pdev); // 保存设备配置状态

pci_disable_device(pdev); // 禁用PCIe设备

pci_set_power_state(pdev, PCI_D3hot); // 设置设备进入D3hot状态

return 0;

}

在恢复(Resume)函数中,驱动程序将设备状态设回D0,并根据需要禁用唤醒功能,最后恢复设备之前保存的状态:

static int xxx_resume(struct pci_dev *pdev)

{

pci_set_power_state(pdev, PCI_D0); // 将设备电源状态恢复至D0

pci_enable_wake(pdev, PCI_D0, 0); // 禁用唤醒功能(如不需要)

pci_restore_state(pdev); // 恢复设备配置状态

return 0;

}

通过这种方式,驱动能够很好地集成到操作系统的全局电源管理策略中,例如在系统待机(S3)或休眠(S4)时自动调用这些函数。更深入的Linux系统与驱动开发知识可以帮助开发者更好地理解和实现这些机制。

其他控制方式:app_req_entr_l1

除了标准的ASPM和PCI-PM,某些硬件平台或应用场景可能提供额外的控制接口。例如,上游端口(如EP)可以通过设置app_req_entr_l1信号,主动请求将本地链路置于L1状态。需要注意的是,下游端口(如RC)可以选择忽略此请求。