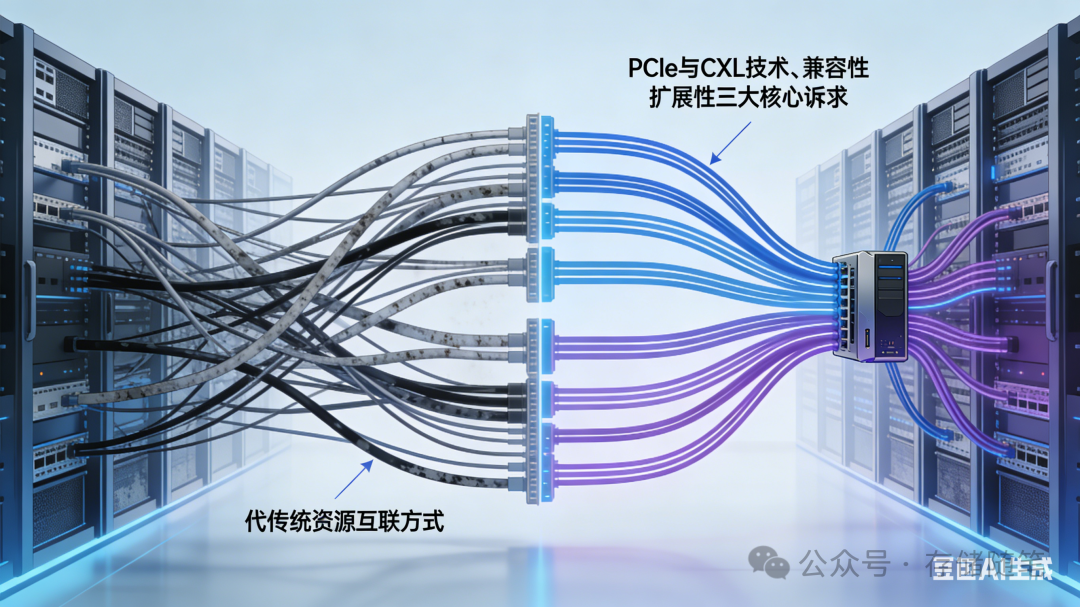

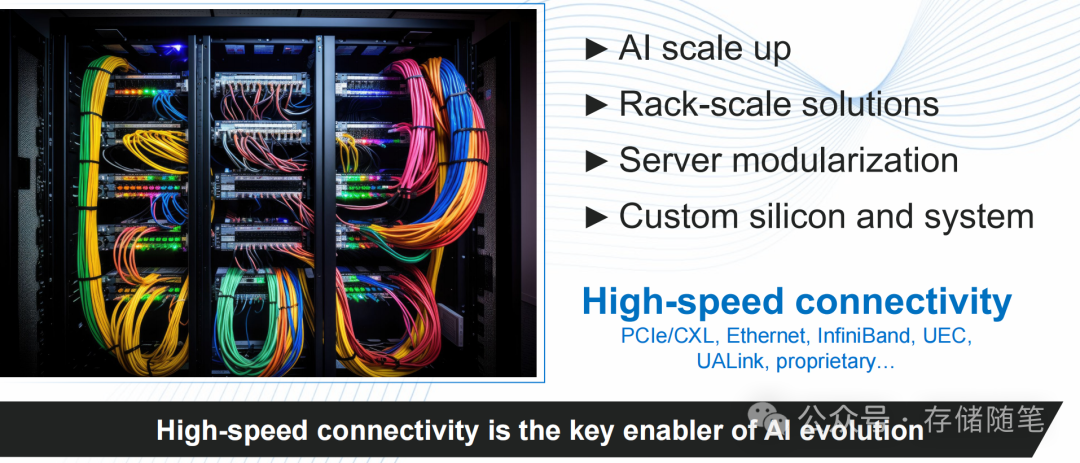

随着AI大模型参数规模迈入万亿时代,分布式计算成为常态,传统的数据中心内部互联方式面临巨大挑战。PCIe与CXL两项关键技术的协同演进,正从物理布线层面出发,重塑数据中心资源的调度与互联格局。

数据中心互联技术的迭代,始终围绕速度、兼容性与扩展性三大核心目标展开。PCIe与CXL的协同发展路径,共同构成了现代算力基础设施的互联基石。

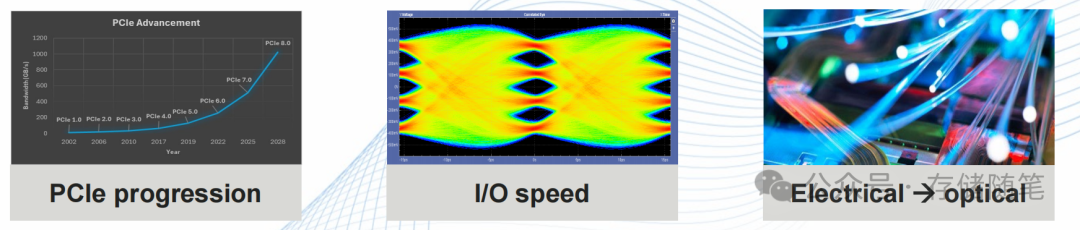

作为业界最普及的高速互联协议,PCIe的演进正在加速。它从早期的电信号传输迈向光学化,实现了质的跨越:

- 速率突破:目前已进入PCIe 6.0时代,单通道速率达到64 GT/s,相比上一代实现带宽翻倍,为存储、内存与各类计算单元之间的高速数据交换奠定了坚实基础。

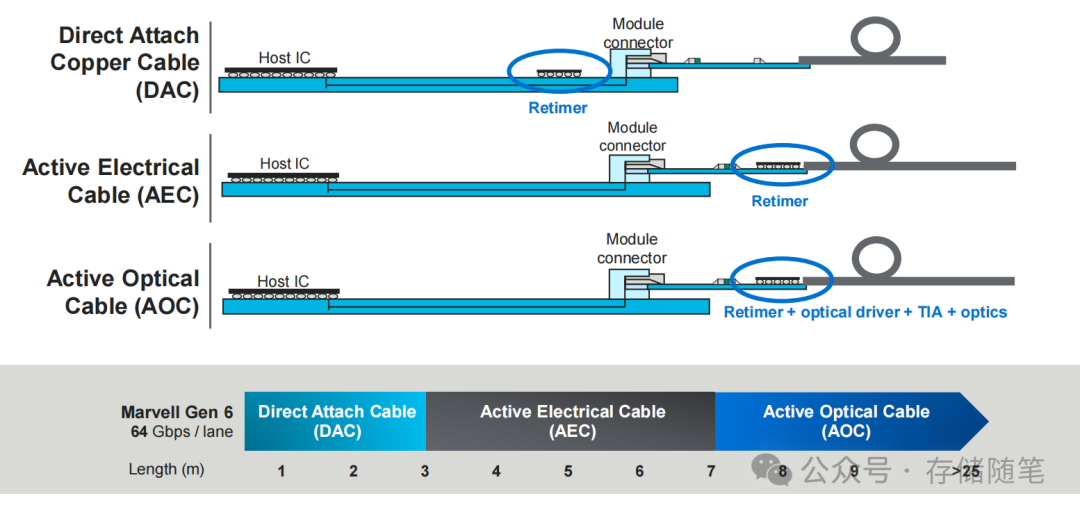

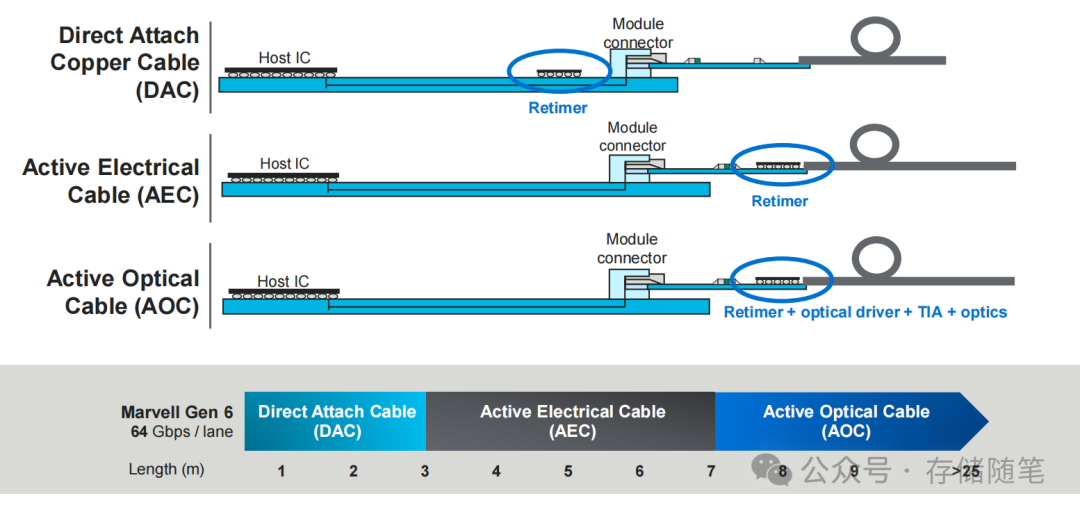

- 介质多元化:借助Retimer(信号中继器)技术,PCIe支持直接连接铜缆(DAC)、有源电气线缆(AEC)和有源光缆(AOC)三种核心线缆类型,分别覆盖板内、板间及机架间等不同距离和场景的需求。

- 距离延伸:不同线缆的组合实现了从1米到25米以上的全场景覆盖。其中AOC光缆突破了传统铜缆的传输距离限制,为大规模AI计算集群的部署提供了可能。

值得关注的是,业界已在关键展会上演示了10米PCIe 6.0 AOC端到端方案以及PCIe 6.0铜缆传输,标志着该技术已趋于成熟,具备大规模商用部署的条件。

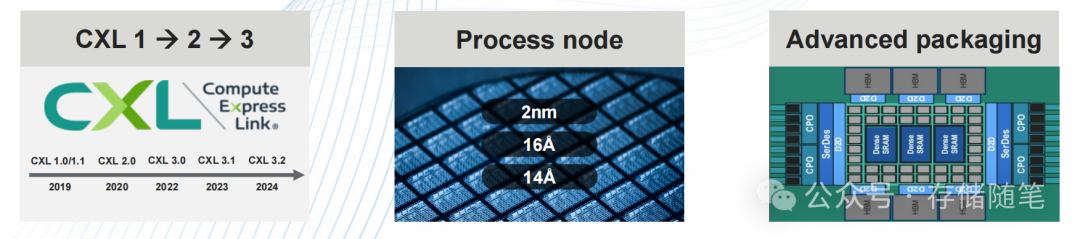

如果说PCIe致力于解决“设备间普遍互联”的问题,那么CXL则专注于实现“计算与内存的高效协同”。作为专为内存扩展设计的协议,CXL的演进逻辑清晰:

- 版本快速迭代:从CXL 1.0/1.1到2.0,再到近年的3.x版本,每一代都在带宽、延迟和扩展性上实现突破,尤其优化了内存池化与缓存一致性机制。

- 与PCIe深度协同:CXL构建于PCIe物理层之上,完全兼容现有PCIe生态,同时提供了更高效率的内存访问语义,使其成为AI等高带宽场景下内存扩展的核心协议选择。

- 先进封装融合:结合Chiplet(芯粒)等先进封装技术,CXL能够实现从芯片级到机架级的多层次内存共享,有效破解了大规模AI训练中的“内存墙”难题。

Retimer作为连接上层协议与物理传输介质的核心桥梁,在PCIe/CXL布线方案中扮演着关键角色。其主要价值在于:

- 补偿高速信号在长距离传输中的衰减,确保信号完整性。

- 实现不同介质(铜缆/光缆)和距离的灵活适配,使DAC、AEC、AOC能在同一架构下协同工作。

- 降低系统设计的复杂度,无需为不同传输场景重构底层协议,保护了现有投资。

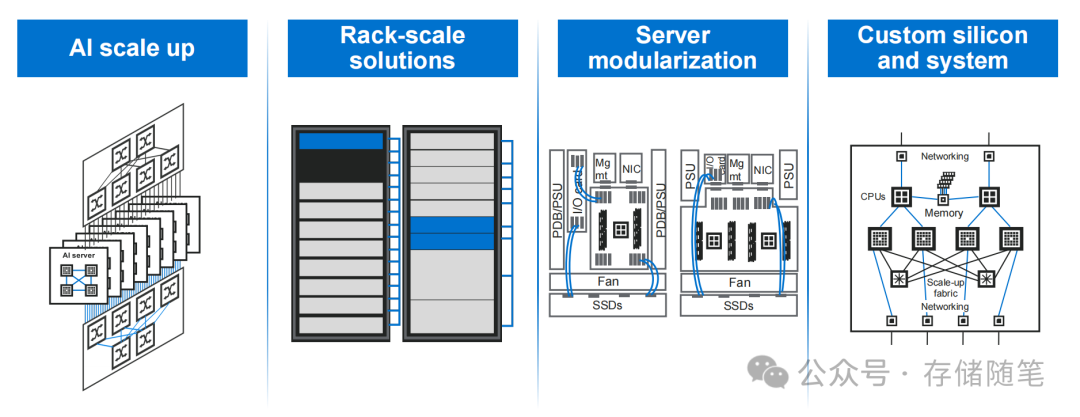

AI数据中心的规模化发展,正驱动其架构从“单机部署”向“机架级资源池”演进,而PCIe/CXL布线正是这一演进的核心支撑。

架构演进的三个层级

- 单机模块化:通过PCIe实现CPU、GPU、内存、存储等内部组件的灵活互联,将传统服务器解耦为可独立配置和升级的模块化组件。

- 机架级整合:基于OCP DC-MHS等开放标准,利用PCIe/CXL布线构建机架级资源池,实现同一机架内多台服务器的内存、存储和计算资源的共享与统一调度。

- 集群级互联:通过PCIe 6.0 AOC光缆,并结合高速以太网或InfiniBand,构建跨机架的分布式计算集群,满足超大规模AI训练对海量数据交互的需求。

核心应用场景落地

在AI训练与推理场景中,PCIe/CXL布线的价值得到充分发挥:

- 内存扩展:通过CXL实现内存池化,让多个GPU等加速器共享超大容量内存资源,突破单卡内存容量瓶颈,支持更大参数模型的训练。

- 存储加速:PCIe 6.0与NVMe SSD的结合,带来了存储吞吐的极大提升。配合AOC光缆,可以构建高性能分布式存储集群,满足AI训练对海量数据集的高速读写需求,这种架构对优化数据库与缓存系统的I/O性能也有重要意义。

- 计算协同:通过PCIe 6.0构建低延迟计算互联网络,实现CPU与GPU、FPGA等异构计算单元的高效协同,降低跨设备数据搬运延迟,提升整体计算效率。

关键技术支撑:生态协同

高速互联的实现依赖于整个技术生态的协同:

- 先进封装技术:Chiplet封装使得不同工艺、功能的芯片能通过高速互联实现异构集成,与PCIe/CXL布线形成互补。

- 光学传输技术:CPO(共封装光学)等技术与AOC的融合,将进一步降低光传输的功耗与延迟,提升端口密度。

- 开源标准推动:OCP等组织推动的硬件开放标准,加速了机架级模块化设计的普及,为PCIe/CXL布线的规模化应用铺平了道路。

随着AI、云计算与边缘计算的融合,异构计算成为主流架构,而PCIe/CXL布线正是其“神经系统”:

- 支持多类型计算单元:无论是CPU、GPU、FPGA还是专用AI芯片,均可通过统一的PCIe/CXL接口接入系统。

- 实现跨场景资源调度:从核心数据中心到边缘节点,统一的互联标准使资源调度更为灵活,支持云端训练与边缘推理的高效协同。

- 兼容未来技术演进:PCIe 7.0、CXL 4.0等下一代技术已在规划中,将持续提升速率与能效,为未来云原生应用与新兴算力场景预留扩展空间。

当计算需求从追求“单点性能”转向“集群协同”,当资源配置从“固定僵化”转向“弹性池化”,互联技术已成为决定数据中心效率的关键变量。PCIe与CXL的布线革命,不仅是协议的升级,更是产业生态的重构。它打破了计算、存储、内存之间的物理壁垒,构建了统一的资源互联平台,为AI算力的无限扩展提供了底层可能。 |