恩智浦最新的双核微控制器i.MXRT1180,在启动架构和外部存储器接口上带来了新的特性。对于开发者而言,理解其FlexSPI接口与NOR Flash的硬件连接方式是进行系统设计和软件移植的第一步。本文将深入解析RT1180支持的共计12种NOR Flash启动连接配置,帮助你一次理清所有硬件设计选项。

在详细展开之前,有两项重要的地址映射信息需要提前明确:

- Note1: 如果可启动的NOR Flash挂载在FlexSPI1上,系统为其分配的映射地址空间起始地址为

0x28000000/0x38000000。进行XIP(就地执行)应用程序开发时,链接起始地址需要设置在此之后。

- Note2: 如果可启动的NOR Flash挂载在FlexSPI2上,系统为其分配的映射地址空间起始地址为

0x04000000/0x14000000。XIP应用程序的链接起始地址需相应调整。

i.MXRT1180作为i.MXRT1170的架构升级版,采用Cortex-M33 + Cortex-M7双核设计。其启动流程有一个关键变化:系统永远从支持TrustZone安全特性的Cortex-M33核心开始启动,这源于其安全架构的重大升级。在启动特性上,RT1180引入了全新的启动头Container结构,取代了之前型号使用的IVT结构。本文聚焦的FlexSPI模块,RT1180芯片内部集成了两个:一个双通道8bit的FlexSPI1和一个双通道16bit的FlexSPI2。这两个FlexSPI端口均支持挂载NOR Flash作为启动设备,这一点与i.MXRT1170保持一致。

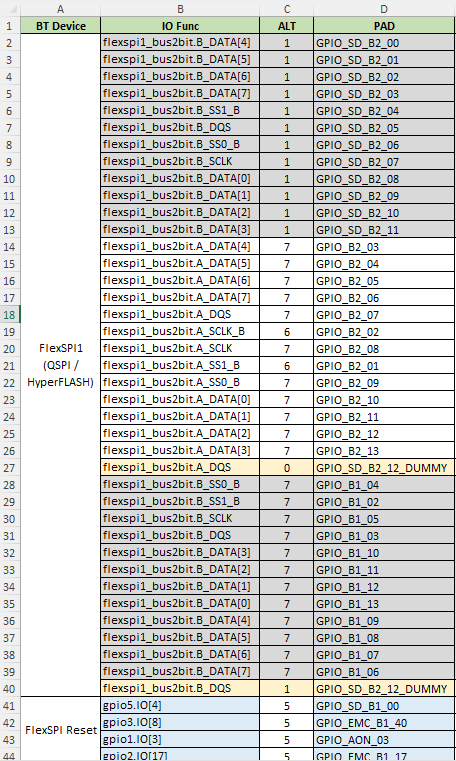

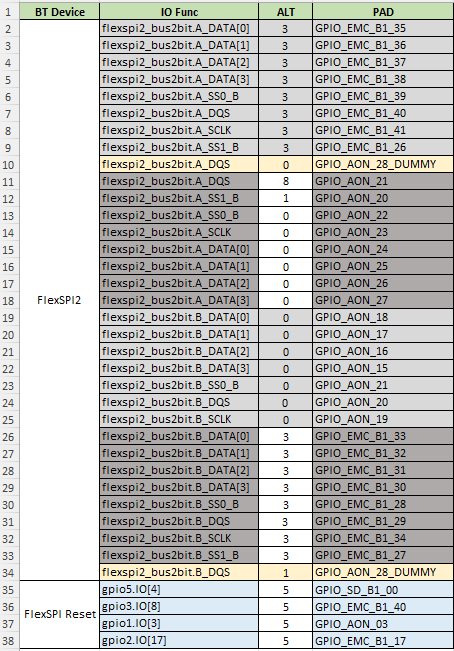

一、BootROM指定的FlexSPI NOR启动引脚

所有的启动连接方式都基于芯片BootROM预先定义好的引脚映射。我们可以在i.MXRT1180的芯片参考手册 System Boot 章节找到这些信息。为了更直观,以下是整理出的FlexSPI1和FlexSPI2相关引脚配置表,这对理解后续的连接组合至关重要。

二、单颗NOR Flash的12种启动连接方式

在实际系统设计中,使用单颗Flash芯片存放应用程序代码(即Code Flash)是最常见的场景。i.MXRT1180支持从这片Flash中原地执行代码(XIP),也支持将代码拷贝到内部RAM中执行。BootROM为单颗Flash提供了丰富的连接选项,总计12种,可以根据Flash类型和硬件布局灵活选择。

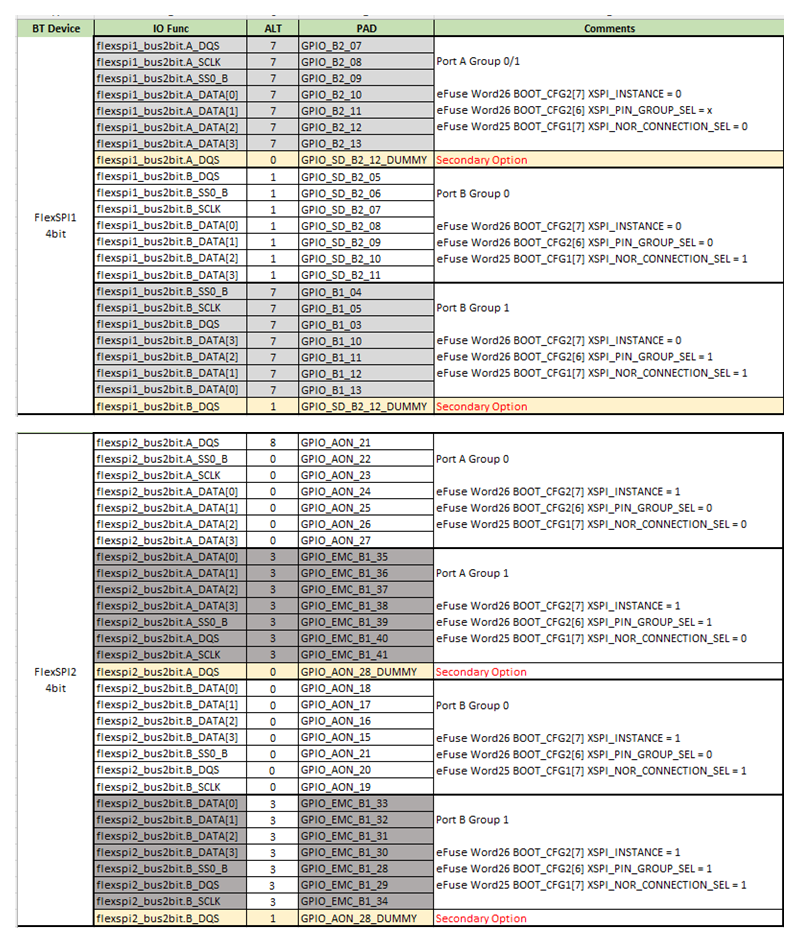

1. 四线QSPI Flash连接方式(7种)

前7种连接方式适用于标准的四线QSPI Flash。它们仅需使用FlexSPI PORTA或PORTB中的6根核心信号线(时钟、片选、数据线0-3)即可完成连接。

一个显著的特点是,对于8bit宽度的FlexSPI1,其PORTB可以独立连接一颗四线QSPI Flash并实现启动,这是此前i.MXRT10xx系列所不具备的能力,为PCB布局提供了更大的灵活性。

上表详细列举了FlexSPI1和FlexSPI2在4bit模式下的所有有效引脚组(Port A Group 0/1, Port B Group 0/1)及其对应的eFuse配置项(如XSPI_INSTANCE, XSPI_PIN_GROUP_SEL, XSPI_NOR_CONNECTION_SEL)。开发者需要根据实际使用的引脚组,通过编程eFuse的相应位来告知BootROM正确的配置。

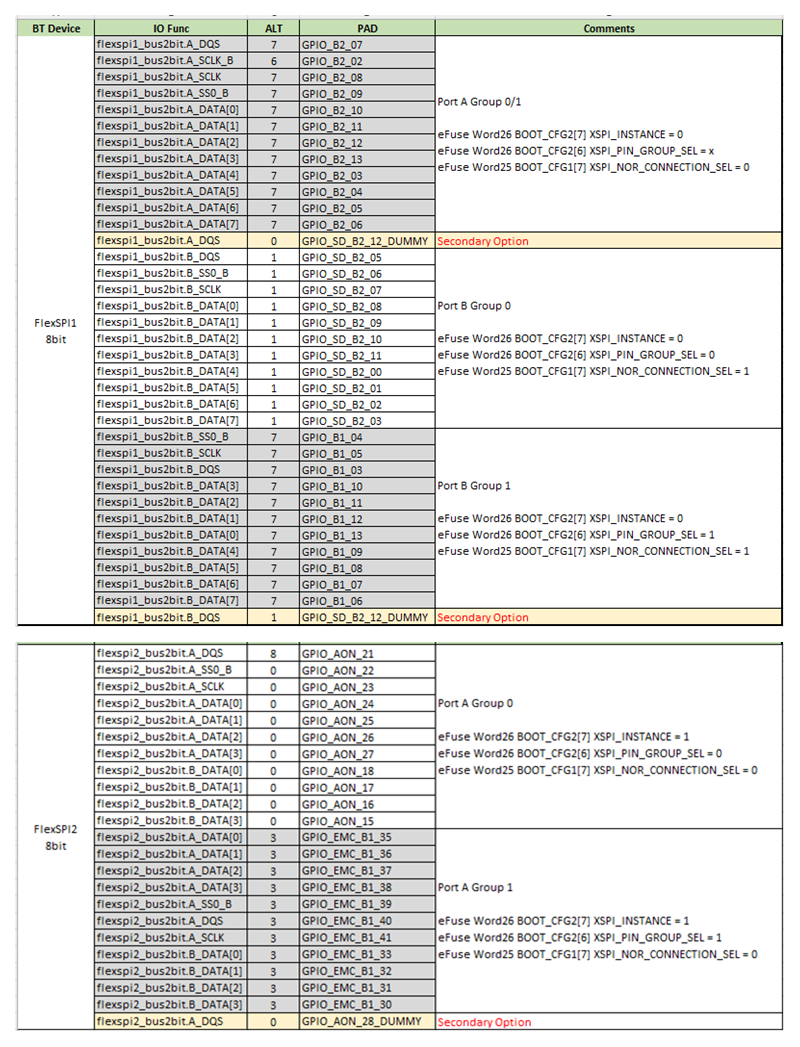

2. 八线Octal/Hyper Flash连接方式(5种)

后5种连接方式则用于八线Octal Flash或Hyper Flash。这类高性能Flash需要占用全部12根信号线(时钟、片选、数据线0-7)以实现更高的数据传输带宽。

这里有一个重要的区别:对于FlexSPI2,需要联合其PORTA和PORTB共同组成一个8bit端口;而对于FlexSPI1,其单独的PORTA或PORTB本身已是8bit宽度,足以连接八线Flash。请注意,出于启动设计限制,FlexSPI1不支持将PORTA和PORTB联合起来组成8bit端口。

此表展示了8bit模式下的引脚组配置。需要特别留意的是,FlexSPI2的部分连接组合涉及到AON(Always-On)电源域的引脚。由于AON域引脚的最高信号翻转频率通常被限制在100MHz,因此当选择通过这些引脚连接Flash时,Flash的工作模式(无论是SDR还是DDR)其时钟频率均不应超过100MHz,否则可能导致启动失败或运行不稳定。

以上就是i.MXRT1180微控制器关于FlexSPI NOR启动的全部12种硬件连接方式解析。正确理解这些引脚组合和配置选项,是确保嵌入式系统硬件设计成功的基础。如果你在系统启动或底层驱动开发中遇到问题,欢迎在云栈社区与更多开发者交流讨论。 |